目录

原题复现

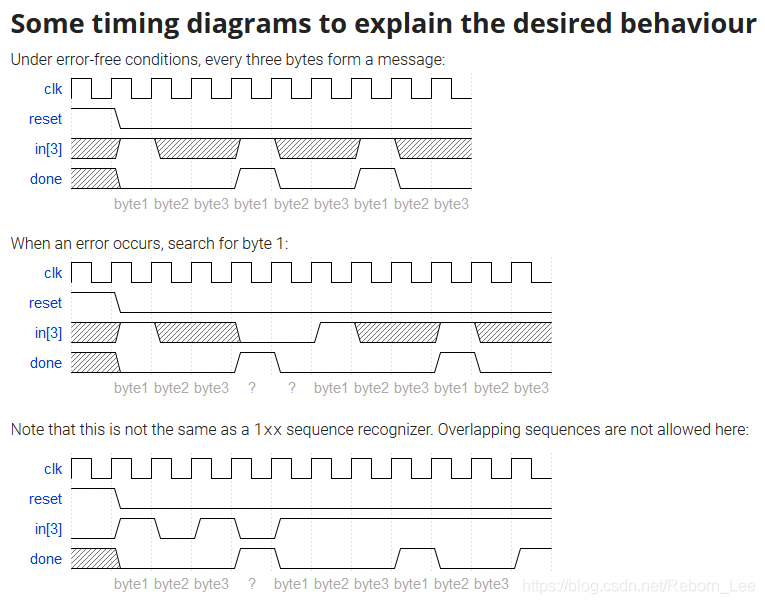

The PS/2 mouse protocol sends messages that are three bytes long. However, within a continuous byte stream, it's not obvious where messages start and end. The only indication is that the first byte of each three byte message always has bit[3]=1 (but bit[3] of the other two bytes may be 1 or 0 depending on data).

We want a finite state machine that will search for message boundaries when given an input byte stream. The algorithm we'll use is to discard bytes until we see one with bit[3]=1. We then assume that this is byte 1 of a message, and signal the receipt of a message once all 3 bytes have been received (done).

The FSM should signal done in the cycle immediately after the third byte of each message was successfully received.

审题

这是一个通信协议传送的问题,将上面的英文翻译下来如下:

PS / 2鼠标协议发送三字节长的消息。 但是,在连续的字节流中,消息的开始和结束位置并不明显。 唯一的指示是,每个三字节消息的第一个字节始终具有bit [3] = 1(但其他两个字节的bit [3]取决于数据,可能是1或0)。

我们想要一个有限状态机,当给定输入字节流时,它将搜索消息边界。 我们将使用的算法是丢弃字节,直到看到bit [3] = 1的字节为止。 然后,我们假设这是消息的字节1,并在接收到所有3个字节(完成)后,发出接收消息的信号。

在成功接收到每个消息的第三个字节之后,FSM应该立即在周期中发出完成信号。

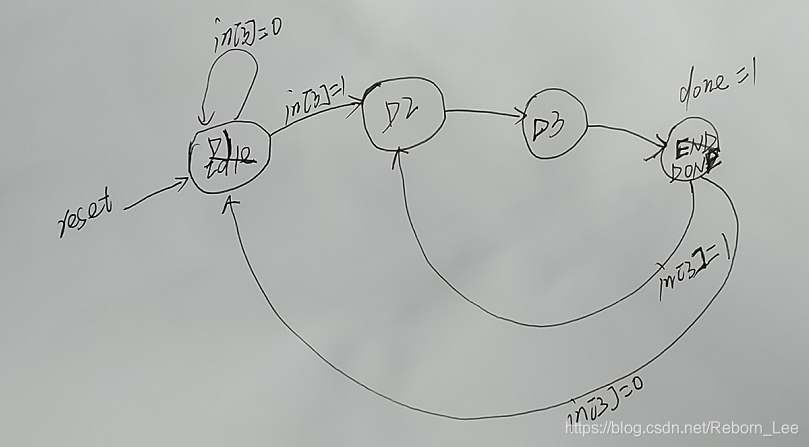

状态转移图

根据时序图以及题目描述,我们可以大概画出状态转移图:

第一个状态D1判断接受数据流的起始字节,如果是起始字节,则紧接着的两个字节为数据流的一部分,数据流总共三个字节,接受完毕之后的下一个时钟周期,输出接受完毕信号Done,于此同时,判断是否接受到了下一个数据流的起始字节,如果是则继续接受下两个字节,否则进入状态D1,继续判断是否接受到起始字节。

由此状态转移图就能得到设计:

我的设计

module top_module(

input clk,

input [7:0] in,

input reset, // Synchronous reset

output done); //

reg [1:0] state, next_state;

localparam D1 = 0, D2 = 1, D3 = 2, DONE = 3;

// State transition logic (combinational)

always@(*) begin

case(state)

D1: begin

if(in[3] == 1) next_state = D2;

else next_state = D1;

end

D2: begin

next_state = D3;

end

D3: begin

next_state = DONE;

end

DONE: begin

if(in[3] == 1) next_state = D2;

else next_state = D1;

end

default: begin

next_state = D1;

end

endcase

end

// State flip-flops (sequential)

always@(posedge clk) begin

if(reset) state <= D1;

else state <= next_state;

end

// Output logic

assign done = (state == DONE)?1:0;

endmodule

测试结果正确。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?