建立时间(tsu):触发器时钟信号上升沿到来以前,数据稳定不变的时间;

保持时间(th):触发器时钟信号上升沿到来以后,数据稳定不变的时间;

tsu和th都是为了可靠地对数据进行采样,时钟边沿触发事件,同步设计时芯片设计的基础。

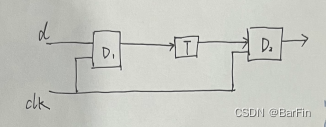

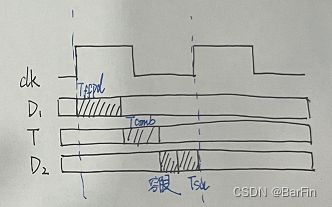

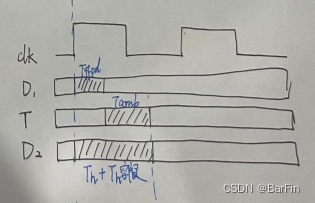

example:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问:触发器D2的建立时间和保持时间应满足什么条件?

对于建立时间来说,需满足的关系:

Tffpd+Tcomb+Tsu+建立时间容限 = Tclk

Tffpd:触发器的输出响应延时

Tcomb:组合逻辑延时

Tsu:触发器D2的建立时间

建立时间容限:≥0

根据上面公式化简,可以得到不等式

Tffpd+Tcomb+Tsu ≤ Tclk

对于保持时间来说,需满足的关系:

Tffpd+Tcomb = Th+保持时间容限

根据上面公式化简,可以得到不等式

Tffpd+Tcomb ≥ Tclk

若两级触发器之间的时钟存在延时t,则需要在公式左边减去。

跨时钟域设计不可避免,只能减少亚稳态的风险。

单比特数据CDC处理方法

①单比特CDC—慢到快

跨时钟信号的宽度 > 采样时钟的两个周期 → 两级同步

直接使用两级同步即可

跨时钟信号的宽度 < 采样时钟的两个周期 → 先脉冲扩展,再两级同步

先脉冲扩展,把脉冲信号的宽度扩展为 大于 采样时钟的两个周期,再使用两级同步。

②单比特CDC—快到慢

这种情况下,跨时钟信号的宽度(最小为快时钟的一个周期)肯定 小于 采样时钟(慢)的两个周期

跨时钟信号的宽度 < 采样时钟的两个周期 → 先脉冲扩展,再两级同步

先脉冲扩展,把脉冲信号的宽度扩展为 大于 采样时钟的两个周期,再使用两级同步。

握手处理

A时钟域向B时钟域发送req信号,保持为高

B时钟域对req打两拍采样到1,再返回ack信号

A时钟域对ack打两拍采样到1,拉低req

3、多比特跨时钟域

多比特跨时钟域打两拍存在的问题

两个信号同时变化有延迟,导致采样时钟采样错误,本来应该是同时拉高,但是跨过来之后错开了。

解决方法

①多比特信号合并为单比特信号

如果需要跨时钟域的信号存在逻辑关系,可以合并为单比特信号再跨时钟域传输

②格雷码

把多比特信号转为格雷码再进行跨时钟域传输。保证同一时刻只有1bit变化

二进制码转为格雷码:二进制码右移一位,和原值异或

③使用单比特握手信号

使用握手信号req和ack

A时钟域和B时钟域握手,握手期间保证传输的多bit数据稳定不变(稳定的数据可以随便跨时钟域)

④使用异步FIFO

数据通过FIFO传输

读写指针(格雷码)跨时钟域传输

避免

1 降低系统时钟(不常见,因为高速率正确处理才是目的)

2 用反应更快的触发器(工艺相关,受硬件制约)

3 引入同步机制,防止亚稳态传播(常见的处理方式,即通过一些机制,在现有硬件条件下,最大程度的减少亚稳态发生)

4 改善时钟质量,用边沿变化快速的时钟信号

2875

2875

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?