通常图中会有很多脉冲,脉冲会以特定的规律在各条端口线上出现。

除时间外,一般要注意上升沿、下降沿、高电平、低电平。

一般都会有时钟或同步信号,其它信号都是根据这个来工作的。

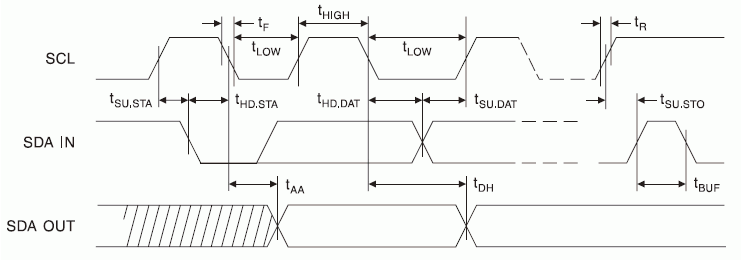

这里用IIC总线的一个图进行简单的说明。

图中有3个时序脉冲,从上到下分别为SCL(串行时钟线),SDA IN(串行数据输入线),SDA OUT(串行数据输出线)

图中SCL开始是低电平面,过一段时间后出现一个上升沿,此端口线电压从低电平跳变为高电来,例如从0V升为5V。

SCL端口线维持高电平一段时间,此过程中,第二根线SDA IN出现一个下跳变,电平从高变为低,如从5V升为0V。

在电平跳变瞬间,硬件内部会有所变化,以便准备执行对应的逻辑变化。

图中下边的SDA OUT为双线,表示该线会有高电平和低电平两种可能,数据线一般就会这样。

344

344

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?