一、计算机组成原理

1. CPU

-

运算器

1.算术逻辑单元ALU:数据的算术运算和逻辑运算

2.累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据和中间运算结果

3.数据缓冲寄存器DR:写内存时,暂存指令或数据

4.状态条件寄存器PSW:存状态标志与控制标志 -

控制器

①程序计数器PC:存储下一条要执行指令的地址(存储指令地址) 注意:不是指令的地址码,而是指令的地址

②指令寄存器IR:存储即将执行的指令 注意:存储指令的地址码和操作数

③指令译码器ID:对指令中的操作码字段进行分析解释

④地址寄存器AR:存储数据地址⑤时序部件:提供时序控制信号

重点 寄存器

-

地址寄存器:存储数据地址

-

通用寄存器: 运算时用于暂存操作数或地址

-

累加寄存器:暂时存放操作数和中间运算结果

透明的:数据缓冲寄存器、数据地址寄存器、指令寄存器

可见的:程序计数器,程序状态字寄存器,通用寄存器

控制器有: 程序,指令,时序,地址

透明的: 数据,指令

可见的: 程序

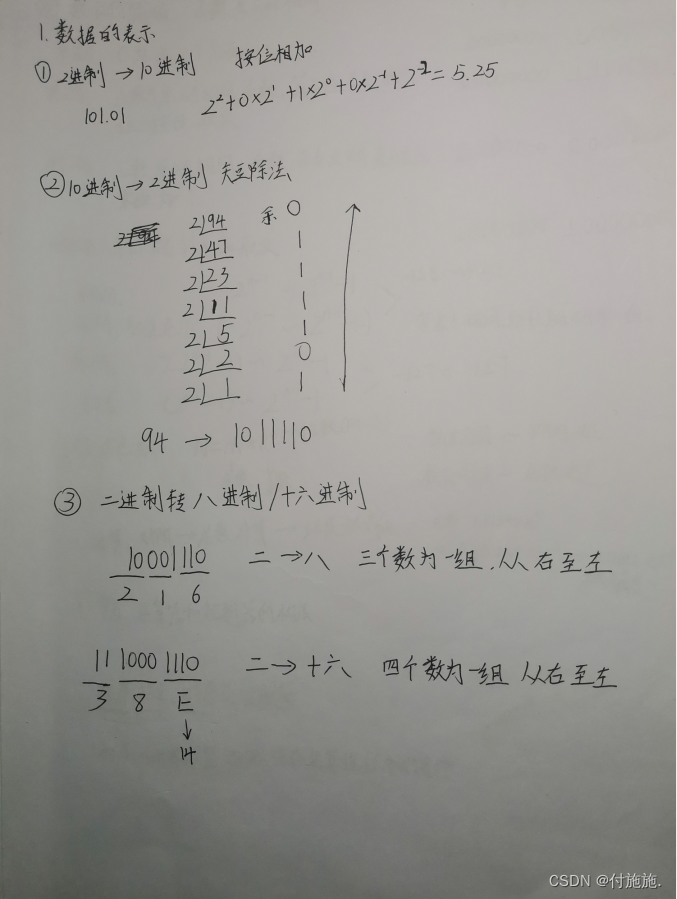

2.基本单位和进制转换

十进制(D)、二进制(B)、八进制(O)、十六进制(H)

- n进制—>10进制 按权相加

- 10进制—>n进制 短除法

- 二进制转八进制(三个数为一组,从左至右)/十六进制(四个数为一组,从左至右)

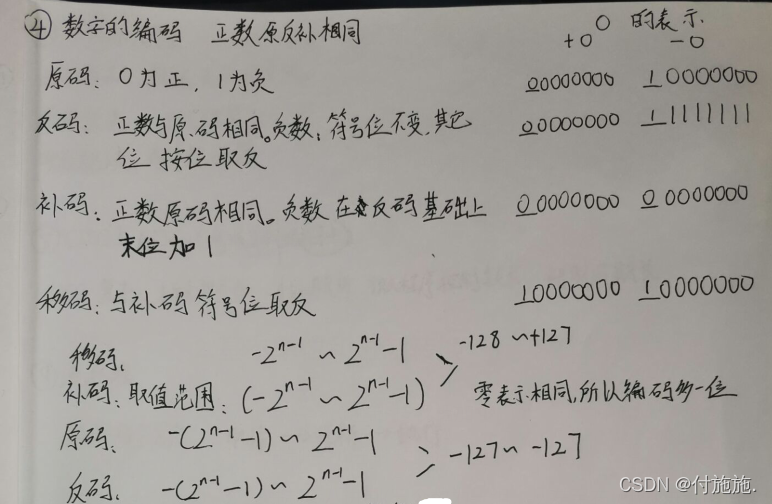

3.原、反、补、移码

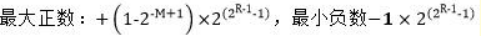

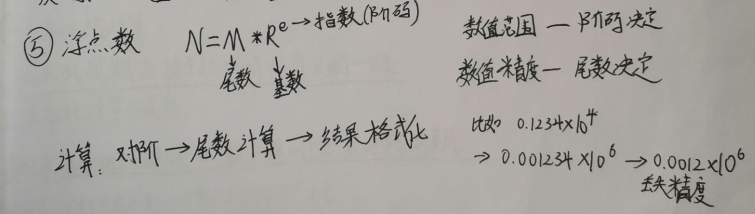

4.浮点数

- 浮点数的表示数值范围

如果浮点数的阶码(包括1位阶符)用R位的移码表示,尾数(包括1位数符)用M位的补码表示,则浮点数表示的数值范围如下。

那说明这种题目选择的时候,正数组合数字,负数正常数字,并且指数都不是2的倍数

- 尾数是四位,阶码加2,尾数右移,但尾数还是只保留四位,所以丢失了精度

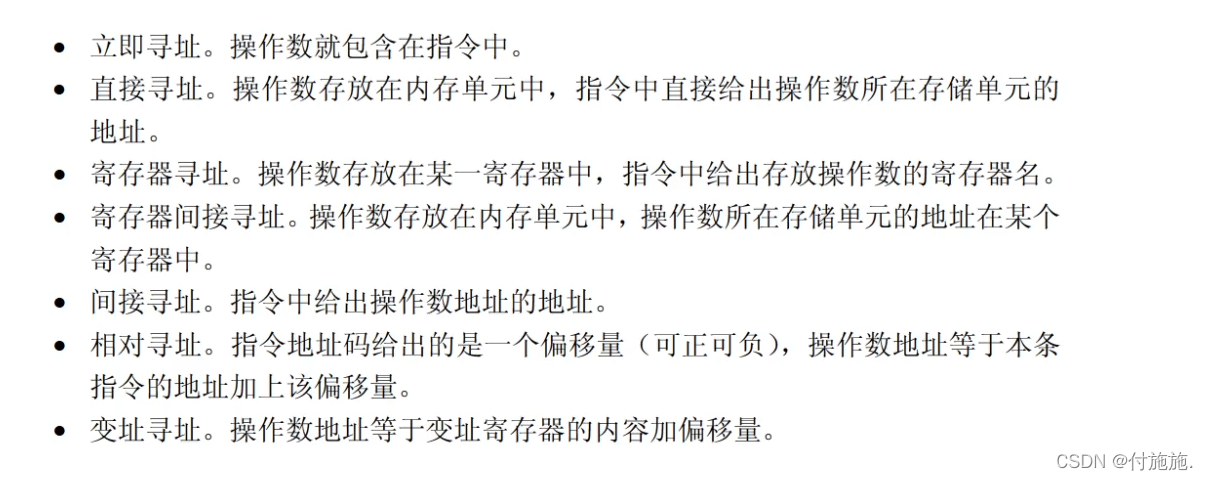

5.寻址

按速度排序

- 立即寻址:不用去寻找操作数

- 寄存器寻址:去寄存器里寻址操作数

- 直接寻址:去内存里找操作数

- 寄存器间接寻址:先去寄存器里拿操作数的地址,再去内存里寻找操作数

- 间接寻址:先去内存里拿到操作数的地址,再去内存里拿操作数

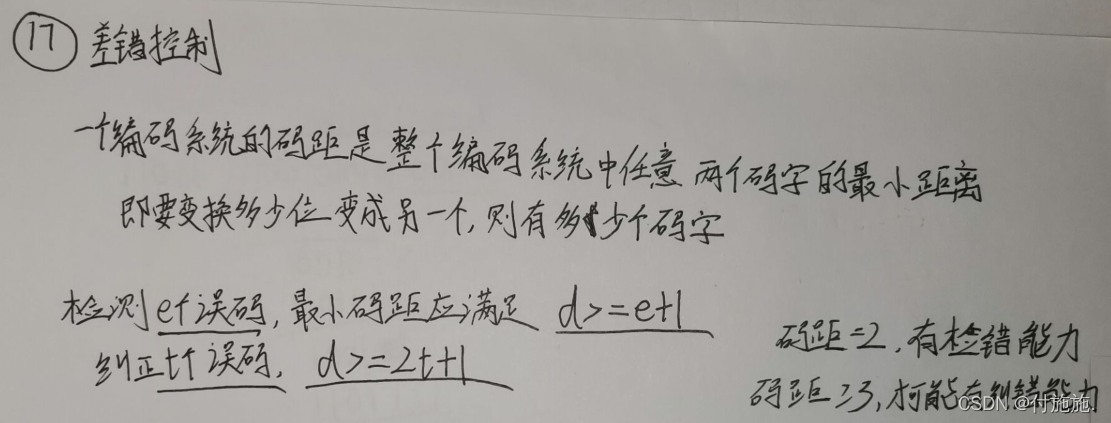

6.校验码

- 奇偶校验码:码距为2,只能检错,不能纠错(奇偶校验是校验1的个数,比如在奇校验,要把编码中1的个数补为奇数,数据传送到另一边,就是看1的个数,所以只能校验奇数个错误)

- CRC校验码:采用模2运算,码距为2,可以检错,不能纠错

- 海明校验码:码距为3,可以纠错

- 海明校验码满足:2^r>=n+r+1 ,r是校验码个数,n是信息位个数

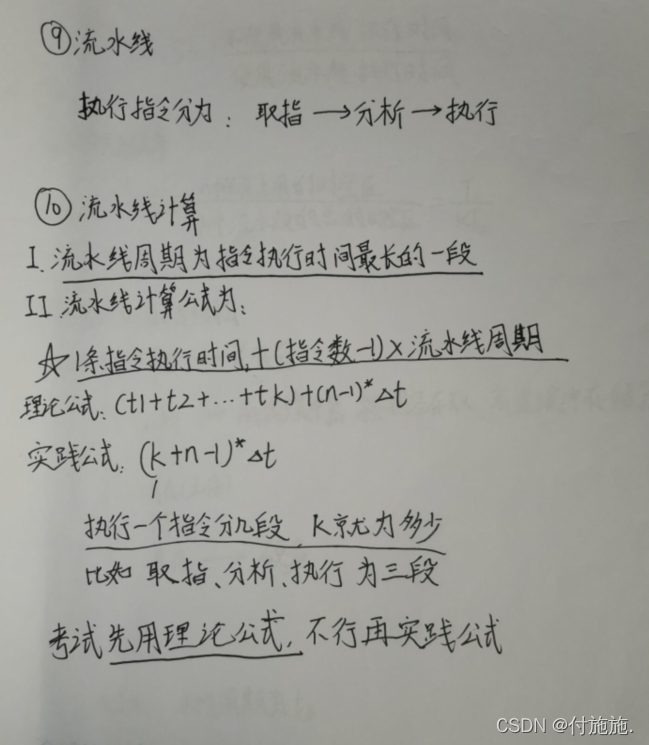

7.CISC与RISC

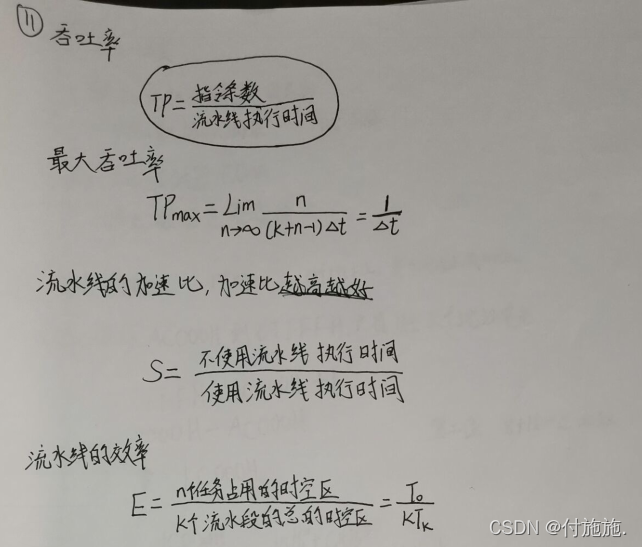

8.流水线

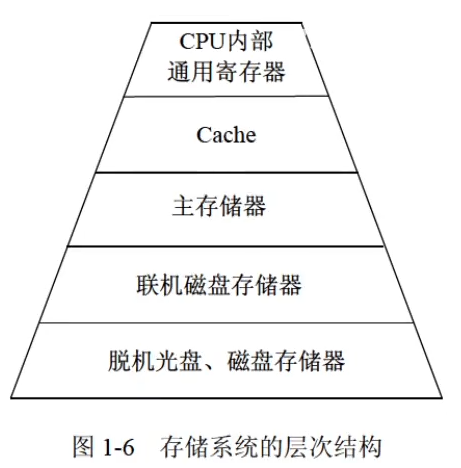

9.存储器

软考书上P21有笔记

CPU—Cache—主存储器—联机磁盘存储器----磁盘存储器

- RAM-----读/写存储器和随机存储器

- ROM-----只读存储器

- SAM------顺序存储器

- DAM------直接存储器

- Cache----SRAM(静态随机存储器)

- 主存------DRAM(动态随机存储器)周期性刷新

- 闪存(U盘)-----以块为单位删除,信息断电不会丢失,可以代替ROM不能代替主存

- 相联存储器----按内容访问

- 虚拟存储器-----由主存和辅存构成的

10.Cache(高速缓存)

-

由硬件自动完成Cache与主存之间的地址映射

-

对程序员来说是透明的

-

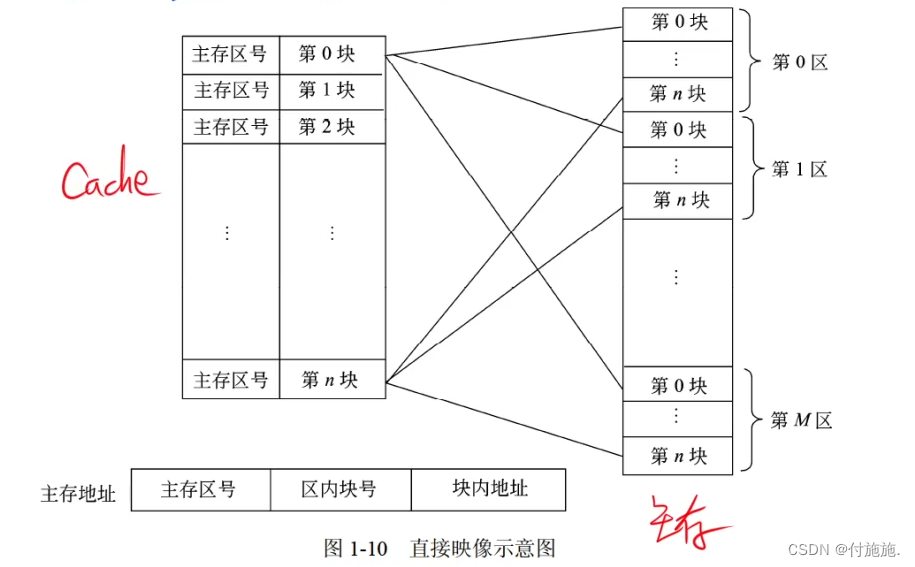

高速缓存中的地址映像方法

- 直接映像:主存的块与Caceh的块的对应关系是固定的。

- 比如内存中每个区的第0块都只能对应Cache中第0块

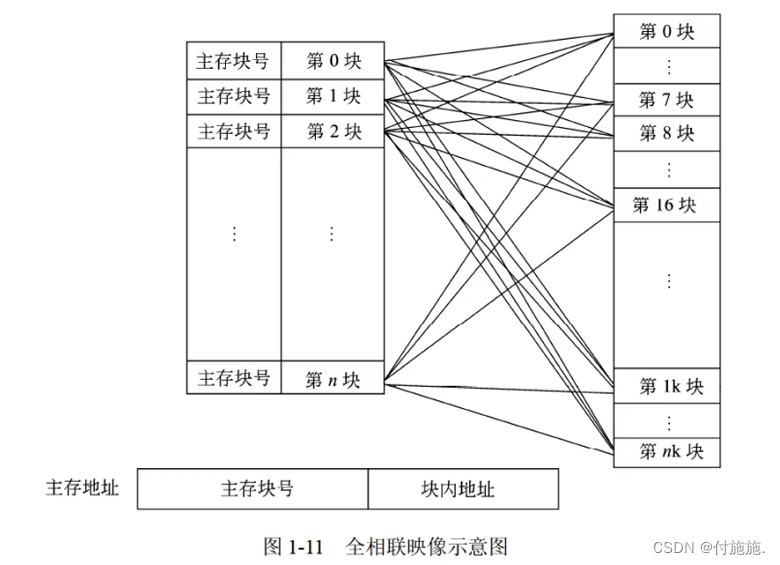

- 全相联映像:主存的任一块可以调入Cache中任一块的空间中,未满即可

- 级相联映像:内存块先分组,组是直接映像,组里面很多块,块是全相联映像

- 直接映像:主存的块与Caceh的块的对应关系是固定的。

-

cache命中率关键因素:程序的行为、cache的容量、组织方式、块的大小有关

- cache容量越大,命中率越高,最后趋于稳定

- 对于给定的Cache容量,当块大小增加时,命中率开始时处于上升趋势,后来反而会下降。

虚拟存储器由主存和辅存构成的

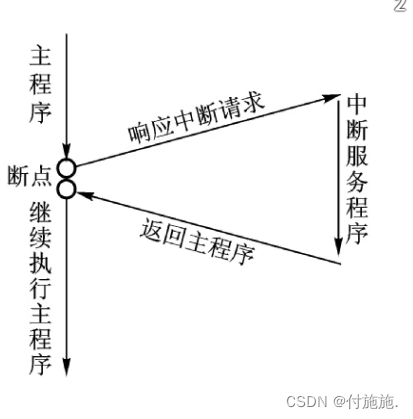

11.中断

- 中断向量:提供中断服务程序的入口地址

- 中断响应时间:发出中断请求开始,到进入中断服务程序

- 中断服务程序 就是 需要紧急处理的程序

- 存储现场:返回来执行源程序

12.输入输出(IO)控制方式

1、程序查询方式

-

CPU和I/0(外设)只能串行工作,CPU需要一直轮询检查,长期处于忙等状态。CPU利用率低

-

一次只能读/写一个字

-

由CPU将数据放入内存

2、中断驱动方式

-

I/O设备通过中断信号主动向CPU报告I/O操作己完成

-

CPU和I/O(外设)可并行工作

-

CPU利用率得到提升

-

一次只能读/写一个字

-

由CPU将数据放入内存

3、直接存储器存取方式(DMA)

- CPU和I/O(外设)可并行工作

- 仅在传送数据块的开始和结束时才需要CPU的干预

- 由外设直接将数据放入内存

- 一次读写的单位为“块”而不是字

若某计算机系统的I/O接口与主存采用统一编址,则输入输出操作是通过访存指令来完成的。

I/O接口单独编址是指通过设置单独的I/O地址空间,为接口中的有关寄存器或存储部件分配地址码,需要设置专门的I/o指令进行访问。这种编址方式的优点是不占用主存的地址空间,访问主存的指令和访问接口的指令不同,在程序中容易使用和辨认。

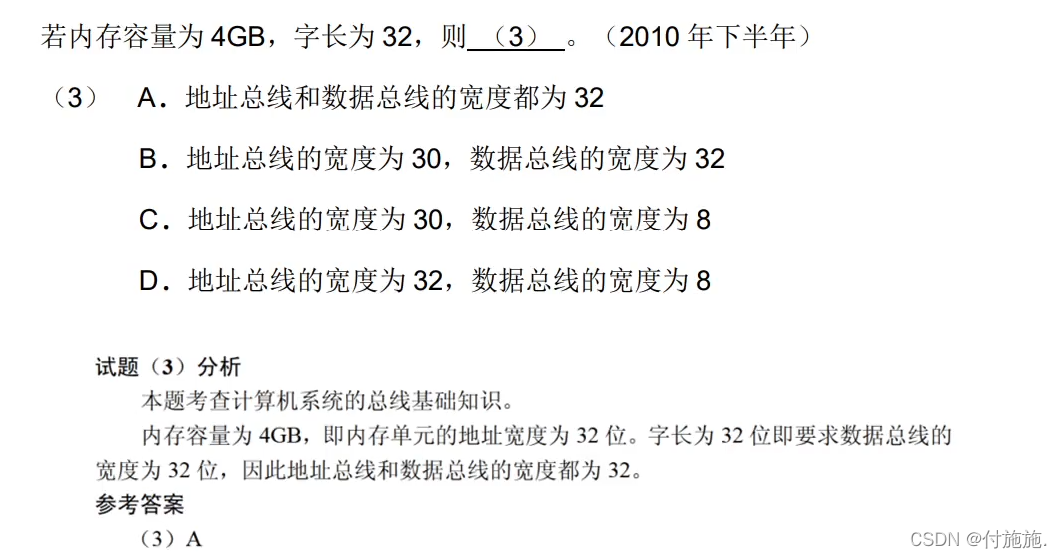

13.总线

分类:数据总线、地址总线、控制总线,数地控

以及13种总线,书上P36,可以去看看背背

-

内存大小和地址总线有关,4GB = 2^32 B,地址总线就是32位,字长就是 数据总线宽度

-

总线可以减少信息传输线的数量

-

带宽=(时钟频率/时钟周期)*总线带宽

14.安全性

1.信息系统安全属性

机密性、完整性、可用性、可控性与可审查性 五个属性

要有最小授权原则,能完成工作的最小权限

2.对称加密技术

特点:加密和解密是同一把密钥只有一把密钥

- 加密强度不高

- 密钥分发困难

- 加密快解密快,适合大量明文数据

加密算法:DES / 3DES / IDEA / RC-5 / RC4 / AES

3.非对称加密技术

特点:私钥只有自己有,公钥满天飞,公钥由PGP证书认证,需要认证这个公钥是谁的公钥

加密算法:RSA / ECC /DSA

- 在非对称加密技术(公钥体系)中,公钥加密,私钥解密

- 甲发给乙明文,则用乙的公钥加密,这样乙只能用自己的私钥解密

- 加密解密速度较慢,但密钥分发无缺陷

4.信息摘要(保证内容未被改)

因为明文内容通过Hash算法单向生成摘要,接收方一比对摘要就可以判断是否修改

摘要:将发送的明文进行Hash算法后得到摘要放在密文后一起发送过去,与接收方解密后的明文进行相同的Hash算法得到的摘要进行对比如果一致,则没有篡改,否则有篡改

算法:

-

MD5—>128位

-

SHA—>160位

5.数字信封(对称与非对称组合使用)

发送方将明文用对称密钥加密传输,而将对称密钥用接收方公钥加密,接受方接收到电子信封,取出对称密钥,获得明文信息

6.数字签名

- 在数字签名中,私钥加密,公钥解密

谁的数字签名用谁的私钥加密

这样用相对应他公钥解密证明是专属签名

私钥只有自己有,公钥满天飞,公钥由PGP证书认证,需要认证这个公钥是谁的公钥

7.认证技术

CA:权威机构

数字证书:用户向CA机构申请数字证书,将个人信息和自己的公钥发给CA机构,

CA机构发给用户数字证书,数字证书通过CA机构的私钥加密,别人只要使用CA机构的公钥解密,得到该用户的公钥

(可以知道这个数字证书被认证过,数字证书中的公钥也能得以保证,即认证了这个公钥是谁的公钥)

8.加密算法

对称加密算法:DES / 3DES / IDEA / RC-5 / RC4 / AES

非对称加密算法:RSA / ECC /DSA

信息摘要:MD5 / SHA

记非对称加密算法,其他就是选对称加密。

15.可靠性

串联:R=R1×R2×…×Rn

并联:R=1-(1-R1)×(1-R2)×…×(1-Rn)

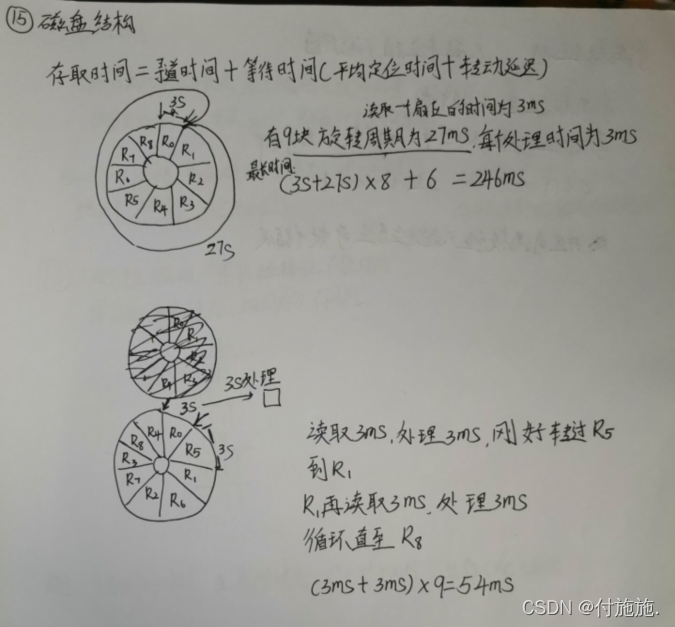

16.磁盘结构

3495

3495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?