第五篇仍然介绍隐层,这一篇其实是我最初要学习的主要内容——LSTM,LSTM的效果比rnn好,rnn存在的一个问题就是误差梯度会随着往前时刻深度的增加而逐渐减少消失,这样rnn的学习算法BPTT的深度就有了限制。LSTM解决了这样的问题,关于LSTM的结构的扩展也有几个阶段,这篇不会再去详细介绍LSTM了,关于LSTM更详细的介绍可以看看我写的另外一篇博客。仍然和前面一样,自己的认知与理解有限,哪里写的不对的还请看到的朋友指出,再次谢过~

LSTM的实现在lstm.cc里面,在rwthlm工具包里面,这是最核心的实现,也是代码量最大的部分,大概超过1000行代码的实现。首先把lstm.cc的构造函数放上来,其实通过构造函数的初始化分配,就能够把LSTM的网络结构给画出来,代码如下:

LSTM::LSTM(const int input_dimension,

const int output_dimension,

const int max_batch_size,

const int max_sequence_length,

const bool use_bias)

: Function(input_dimension,

output_dimension,

max_batch_size,

max_sequence_length),

sigmoid_(),

tanh_() {

//这里的一维数组仍然是前面那种类似的结构

int size = output_dimension * max_batch_size * max_sequence_length;

//lstm层的cell的输出

b_ = FastMalloc(size);

//保存cec的输入输出

cec_b_ = FastMalloc(size);

//cell的输入

cec_input_b_ = FastMalloc(size);

//保存输入控制门的输入输出

input_gate_b_ = FastMalloc(size);

//保存遗忘控制门的输入输出

forget_gate_b_ = FastMalloc(size);

//保存输出控制门的输入输出

output_gate_b_ = FastMalloc(size);

//_t_命名类指针都是会变动的,用于表示时间的变化

b_t_ = b_;

cec_input_b_t_ = cec_input_b_;

cec_b_t_ = cec_b_;

input_gate_b_t_ = input_gate_b_;

forget_gate_b_t_ = forget_gate_b_;

output_gate_b_t_ = output_gate_b_;

//这里不明白为啥要重新赋值,上面定义size时不就初始化为这个了嘛

size = output_dimension * max_batch_size * max_sequence_length;

//output gate的误差信号

cec_epsilon_ = FastMalloc(size);

delta_ = FastMalloc(size);

//输入控制门的误差

input_gate_delta_ = FastMalloc(size);

//遗忘控制门的误差

forget_gate_delta_ = FastMalloc(size);

//输出控制门的误差

output_gate_delta_ = FastMalloc(size);

//这里同上

cec_epsilon_t_ = cec_epsilon_;

delta_t_ = delta_;

input_gate_delta_t_ = input_gate_delta_;

forget_gate_delta_t_ = forget_gate_delta_;

output_gate_delta_t_ = output_gate_delta_;

//std::cout << "input_dimension: " << input_dimension << "\toutput_dimension: " << output_dimension << std::endl;

//假设命令是myExample-i10-M12

//这里的input_dimension就是10,output_dimension就是12

size = input_dimension * output_dimension;

//这里的权值仅仅是输入层到该lstm层的

weights_ = FastMalloc(size);

//下面控制门的权重仅仅是输入层到控制门的

input_gate_weights_ = FastMalloc(size);

forget_gate_weights_ = FastMalloc(size);

output_gate_weights_ = FastMalloc(size);

momentum_weights_ = FastMalloc(size);

momentum_input_gate_weights_ = FastMalloc(size);

momentum_forget_gate_weights_ = FastMalloc(size);

momentum_output_gate_weights_ = FastMalloc(size);

//这部分权重是循环结构的,即前一时刻lstm层到当前时刻lstm层的连接

size = output_dimension * output_dimension;

recurrent_weights_ = FastMalloc(size);

input_gate_recurrent_weights_ = FastMalloc(size);

forget_gate_recurrent_weights_ = FastMalloc(size);

output_gate_recurrent_weights_ = FastMalloc(size);

momentum_recurrent_weights_ = FastMalloc(size);

momentum_input_gate_recurrent_weights_ = FastMalloc(size);

momentum_forget_gate_recurrent_weights_ = FastMalloc(size);

momentum_output_gate_recurrent_weights_ = FastMalloc(size);

//从上面的分配来看,容易知道控制门的输入来自于3部分: 1.输入层的输出 2.本层的前一时刻输出 3.来自cec状态的前一时刻输出

//lstm层的输入自于这两部分:1.输入层的输出 2.本层的前一时刻输出

//peephole connection,这是从cec到gate的连接

input_gate_peephole_weights_ = FastMalloc(output_dimension);

forget_gate_peephole_weights_ = FastMalloc(output_dimension);

output_gate_peephole_weights_ = FastMalloc(output_dimension);

momentum_input_gate_peephole_weights_ = FastMalloc(output_dimension);

momentum_forget_gate_peephole_weights_ = FastMalloc(output_dimension);

momentum_output_gate_peephole_weights_ = FastMalloc(output_dimension);

//从这里的分配来看,能够知道lstm层内部的结构:

//output_dimension的大小即是block的大小,每个block大小包含一个cell,一个cell里面包含一个cec

//即output_dimension的大小就是cec个数,每个cec与三个gate连接

//bias的设置

bias_ = use_bias ? FastMalloc(output_dimension) : nullptr;

input_gate_bias_ = use_bias ? FastMalloc(output_dimension) : nullptr;

forget_gate_bias_ = use_bias ? FastMalloc(output_dimension) : nullptr;

output_gate_bias_ = use_bias ? FastMalloc(output_dimension) : nullptr;

momentum_bias_ = use_bias ? FastMalloc(output_dimension) : nullptr;

momentum_input_gate_bias_ = use_bias ?

FastMalloc(output_dimension) : nullptr;

momentum_forget_gate_bias_ = use_bias ?

FastMalloc(output_dimension) : nullptr;

momentum_output_gate_bias_ = use_bias ?

FastMalloc(output_dimension) : nullptr;

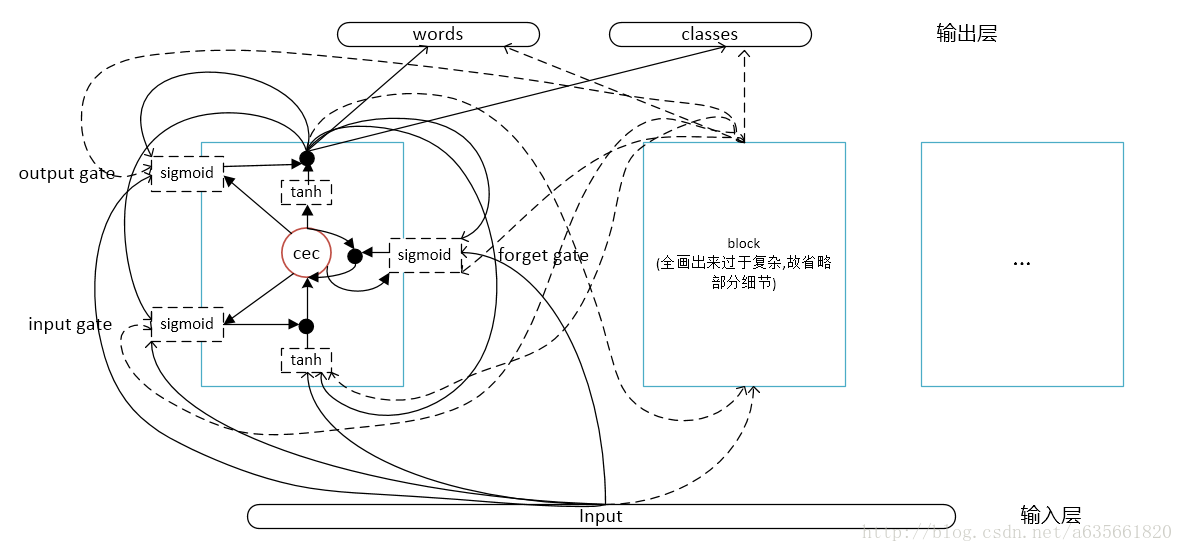

}从代码来看,能够得到LSTM网络的结构如下图:

整个LSTM的结构是每个block(图中方框)包含一个cell(从tanh到tanh部分), 每个cell包含一个cec(图中红色圆圈) (PS: 这个图没画全,画了第一个block就已经觉的很复杂了,加上第二个估计会被连接线绕昏头了,而且比较费时,如果觉的不错,就点个赞吧,哈哈,开玩笑:D)

从代码的执行来看,容易知道每个block的输入来自于两部分:

- 输入层的输出

- 本层前一时刻block的输出

gate的输入来自于3部分:

- 输入层的输出

- 本层的前一时刻block输出

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1084

1084

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?