第二节:操作系统准备知识

安装了操作系统的计算机可以看作是一台用户友好的通用图灵机, 它接受任意程序文件和数据文件,利用数据运行程序并产生输出。

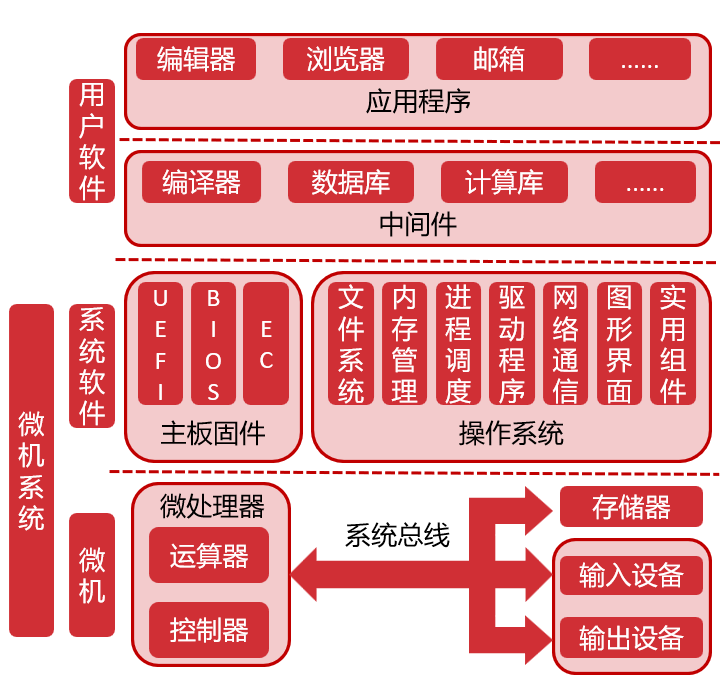

计算机系统的概念图

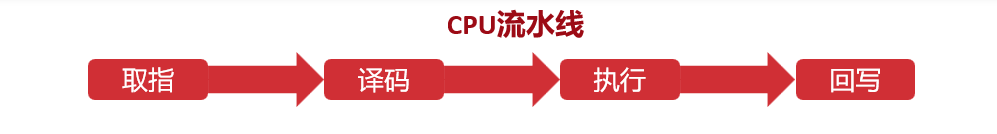

CPU流水线

回写: 将指令执行的结果写回到寄存器组中

存储器层次组织

数据在存储器中的表示

单字节值:

按地址从小到大存储,每个地址存储一个值。

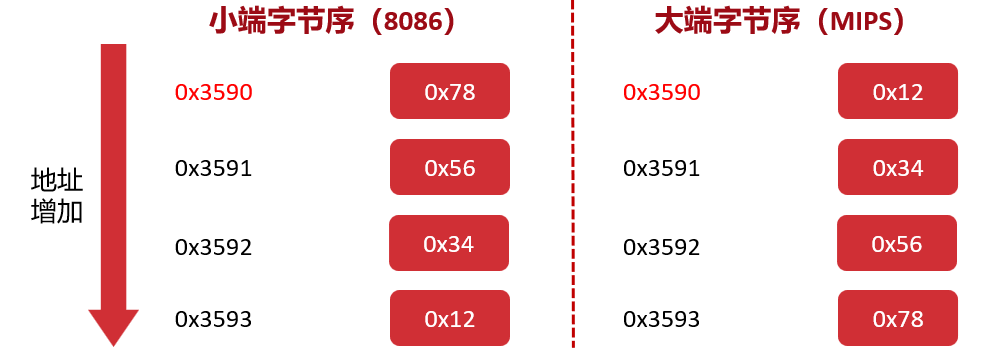

多字节值:

有两种存储方法,一种叫做大端字节序,高位存储在低地址,一 种叫做小端字节序,低位存储在低地址。

多字节值的存储地址被 认为是其占用的地址最低的存储单元的地址。

小端字节序在逻辑上更顺畅,大端字节序人阅读更方便。

小端字节序是主流选择。8086是小端字节序。

指令集架构

- 指令系统:全部指令集称为指令系统。指令系统反映了CPU的基本功能,对 于一款CPU来说是固定的。也称为指令集。 软件设计人员和硬件设计人员之间的重要共识。 也叫指令集架构(Instruction Set Architecture, ISA),或体系结构。 同一个ISA设计可由不同厂家(Intel/AMD)提供不同实现。

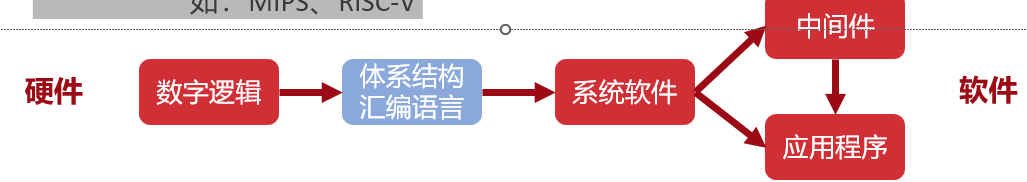

- CISC:复杂指令集计算机(Complex Instruction Set Computer) 增强指令功能,设置功能复杂的指令,尽量使用硬件来实现功能 如:x86,8051

- RISC:精简指令集计算机(Reduced Instruction Set Computer) 简化指令功能,降低指令数量,以软件来实现复杂功能 如:MIPS、RISC-V

- 从硬件到软件:

汇编语言:

-

汇编语言基本等于机器语言的人类友好形式。

-

8086(X86的公共子集)

-

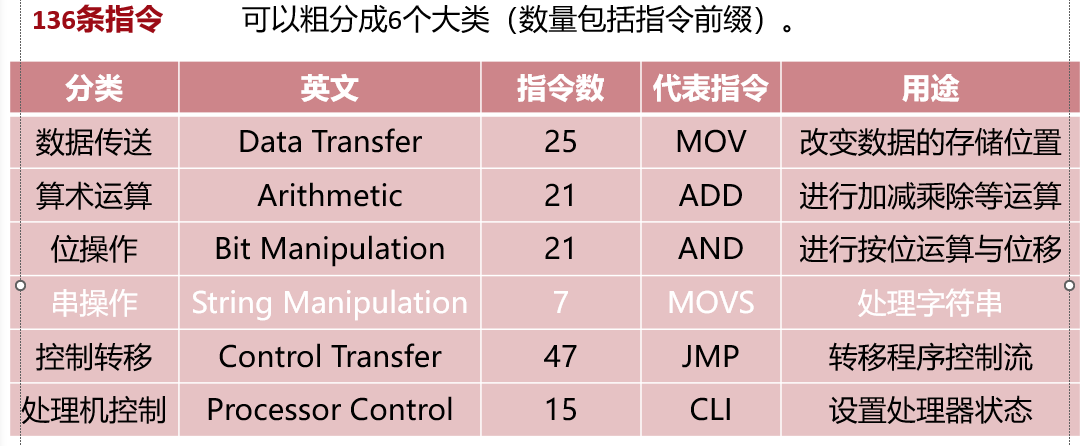

**常见CPU指令集,一般都包括哪五种类别的指令?**数据传送,算术运算,位操作,控制转移,处理机控制

-

8086专用寄存器

- IP 指定将IP用于指令地址记录,即Instruction Pointer。每次取指后都自增1。

- FLAGS 指定将FLAGS用作程序状态指示,也即PSW(Program Status Word)。

-

8086的通用寄存器

-

AX 鼓励将AX用作累加器,Accumulator。

BX 指定将BX用作基地址寄存器,Base。

CX 鼓励将CX用作计数寄存器,Counter。

DX 鼓励将DX用作数据暂存器,Data。

分段 以上四个16位寄存器均可分成高、低8位独立访问, 如AX的高8位称为AH,AX的低8位称为AL。

SI 指定将SI用作源变址寄存器,Source Index。

DI 指定将DI用作目的变址寄存器,Destination Index。

BP 鼓励将BP用作目的基址指示器,Base Pointer。

SP 指定将SP用于堆栈指针,Stack Pointer。

-

-

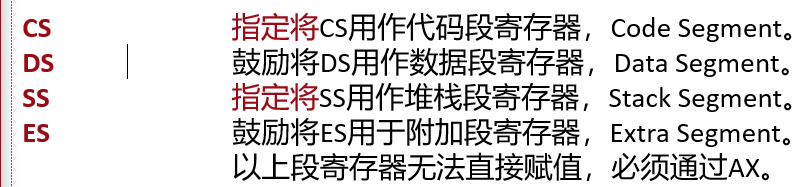

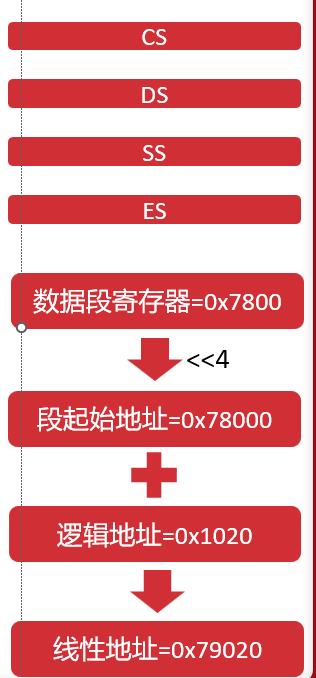

8086段式内存管理

-

为什么需要它:16位地址空间仅64kB,不够用,但市场上大 部分软件却是16位的,而且32位机成本也高。 因此,需要一种低成本、兼容性好的方法, 让16位机也能访问大地址空间,比如20位地 址空间,同时又无需修改原有程序。

-

逻辑地址 程序中引用的16位地址,也叫偏移量或有效 地址。

-

线性地址 经段式内存管理机制转换后,8086 CPU要实 际访问的20位地址,也叫物理地址。

-

一些寄存器的名字:

-

地址生成算法:线性地址=(段寄存器值<<4)+逻辑地址;左移4位等于乘以16,16进制补一个0即可。示意图如下:

-

-

输入输出设备

-

信息交换

-

外设和主机交互包括四种主要方式:

-

直接交换 外设总是准备好接受或发送数据,主机直接读写

-

查询(轮询) 在读写前查询外设是否准备好,主机再读写

-

中断 外设通过中断主动通知主机准备好,主机再读写

-

成组传送 由DMA控制器读写设备,CPU不干涉,性能最高。

四种方式使用都很普遍,其中中断相对而言是主流方式。

-

-

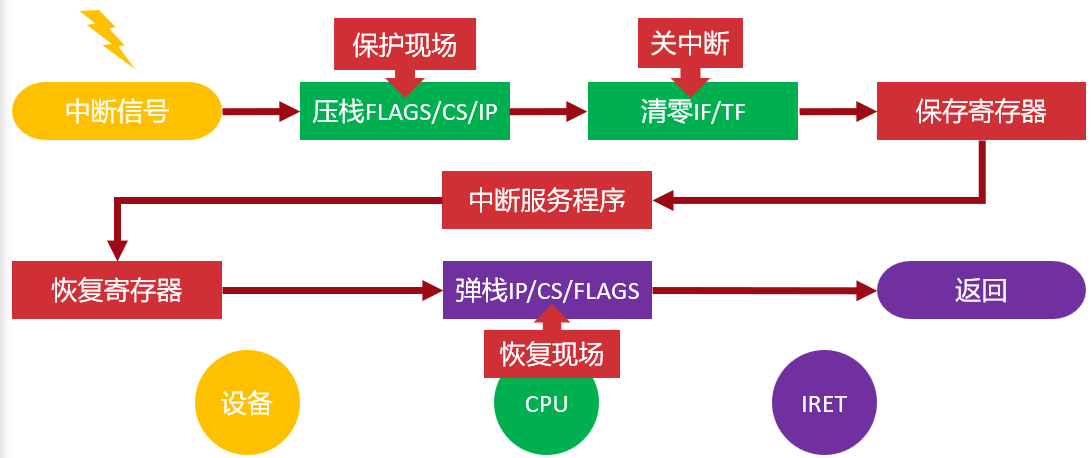

8086中断响应的流程

-

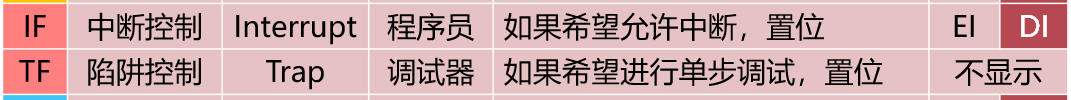

和中断相关的两个寄存器:

-

流程图:

-

需要说明的地方:

- 当中断来临时,CPU执行完当前正在执行的指令,就跳转去ISR,且IRET返回时返回到下一条指令处。当然,某些特殊情况不是这样,这要看处理器的设计。

- (1)如果指令本身是REP字符串指令,则执行完一次拷贝就跳转去ISR,且IRET返回时仍回到指令本身以继续拷贝;

- (2)如果中断是一个异常,则IRET返回到指令本身再次尝试执行;(我的理解是这个异常可能是指令造成的,中断处理完毕后需要判断该指令是否可以继续执行)

- (3)STI、IRET指令以及操作段寄存器的指令会导致执行完本指令之后再执行指令才响应中断。

- 当中断来临时,CPU执行完当前正在执行的指令,就跳转去ISR,且IRET返回时返回到下一条指令处。当然,某些特殊情况不是这样,这要看处理器的设计。

-

中断服务程序(Interrupt Service Routine (ISR))

-

由CPU在响应中断时,自动调用的一段对应于中断号的特殊过程。 也叫中断例行程序、中断向量(Interrupt Vector)。

-

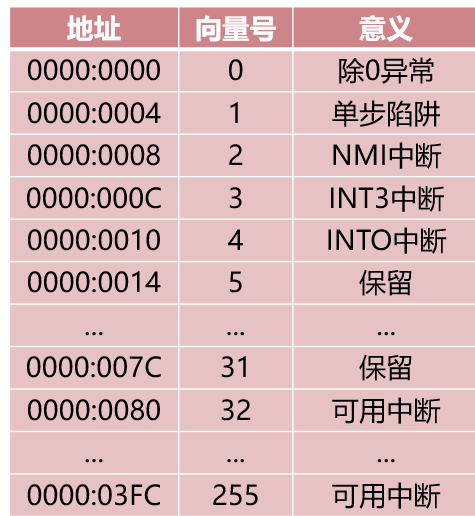

设立向量表(这个地方我不是非常理解,但我感觉不大重要)

-

中断向量的地址一般是4个字节

-

由用户程序直接读写对应的中断向量:对于向量号N,IP存放在[0000:4N],CS则存放在[0000:4N+2]

-

使用DOS系统调用:写入中断向量:AH=25H,AL=中断向量号,DS:DX=中断向量INT 21H

读取中断向量:AH=35H,AL=中断向量号INT 21H,返回时送ES:BX=中断向量

-

-

-

中断嵌套

- CPU一旦进入中断,IF就被清零,这意味着它无法再响应任何中 断。但在中断程序中可以通过STI来手动置位IF,这样CPU就又可 以响应优先级比当前中断高的中断了。在很多实时系统中,一 进入中断就直接执行STI来置位IF能保证高优先级中断得到最快响 应。但是,一个中断无法嵌套自己(无法递归),因为自己和 自己的优先级是一样高的。

-

软件中断

-

异常捕获:当程序中的指令执行发生错误,就会抛出异常,异常会被同步 捕获(和通常的中断与CPU异步不同)

-

陷阱设置:除了设置TF之外,程序单步调试的一个重要手段就是将断点位置 换成INT 3(该指令有特殊单字节编码CC,而非常规的CD 03)。 这样,运行到此处便会触发3号中断,使调试器捕获该断点。此类用法又叫做陷阱

-

**为何要给INT3分配特殊的单字节编码?**http://t.csdnimg.cn/7wQq1核心内容:

INT3指令生成一个特殊的单字节操作码(CC),用于调用调试异常处理程序。(这种单字节形式很有价值,因为它可以用来用断点替换任何指令的第一个字节,包括其他单字节指令,而不会重写其他代码)。

软件断点指令应该是最小的指令大小,这样它就不会覆盖可能成为跳转目标的指令,并且当程序跳到断点指令的中间时会导致灾难。(严格来说,断点必须不大于可能成为跳转目标的指令之间的最小间隔

-

-

系统调用:是陷阱的一种特殊情况。DOS常用INT 21H,而Linux等现代操作系统使用INT 80H。最新的 AMD64架构甚至具备专用的syscall/sysret(或sysenter/sysexit)来 加速调用过程。进行系统调用时,还会从用户态切换到内核态。

-

-

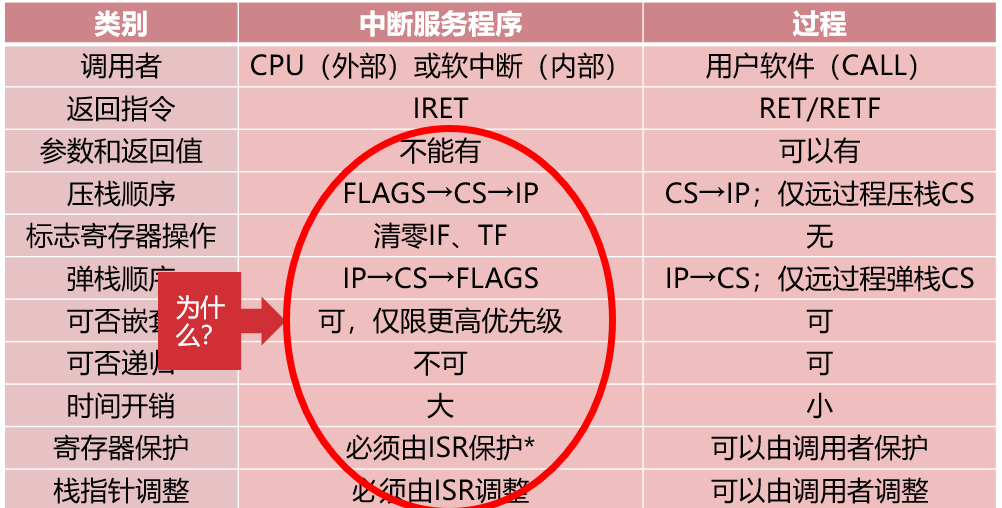

中断服务程序和过程:

-

EOI 中断结束寄存器(End of Interupt)

应用程序的隔离

处理器特权级

-

硬件特权级:用户模式,内核模式

-

特权级通过什么机制切换?中断机制和专用指令机制

-

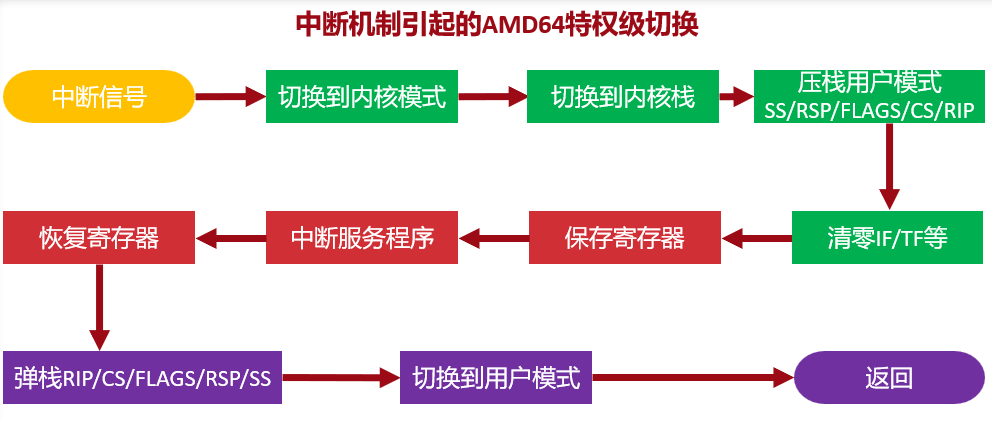

中断机制引起的AMD64特权级切换:

-

相比8086,为何AMD64要切换到内核栈且多压栈了SS和RSP?

进入内核模式时,必须修改FLAGS/CS/RIP以关中断而且跳转到中 断服务程序。我们可以把它们的原值保存在栈上。但此时的 SS:RSP是指向用户空间的不可信的值,不能在内核模式对它进行操作,否则一旦应用程序有恶意就导致内核出错。

这就导致进入中断时,CPU必须切换到内核的SS:RSP,才能压栈 FLAGS/CS/RIP。但这会使原来的用户模式SS:RSP丢失。为了避免 产生此问题,CPU会将用户态的SS:RSP压在内核栈上。

-

操作系统的结构

-

库结构(简要结构,单核结构)

特点 无内核模式与用户模式的区分。

所有应用程序以及内核都在同一个保护域。

应用程序可以随时对任何资源做任何操作。

应用程序间为合作关系,操作系统的角色偏重协调而非管理。

适应场合 设备功能较简单、预算较低的场合。

-

宏内核结构——最容易出现问题的是驱动程序(由硬件制造商提供)

特点 有内核模式与用户模式的区分。

每个应用程序在不同的保护域。

内核的所有功能位于同一个保护域。

应用程序必须请求内核完成敏感资源操作。

应用程序间为合作或竞争关系,操作系统的协调和管理并重。

适应场合 桌面计算等复杂度和性能要求适中的常规应用场合

最广泛使用的内核结构之一。

-

微内核结构

特点 有内核模式与用户模式的区分,每个应用程序在不同的保护域。

内核除基本功能外,其它功能分别位于不同的用户模式进程中。

应用程序必须请求守护进程中的策略分配敏感资源。

守护进程则转而使用内核提供的机制完成这些分配操作。

适应场合 高性能、高可靠性或高灵活性(策略定制)计算等应用场合。

嵌入式和非标领域最广泛使用的内核结构之一。

抗软件故障和攻击,操作系统的一部分损坏不会影响其它部分。

-

外核结构

-

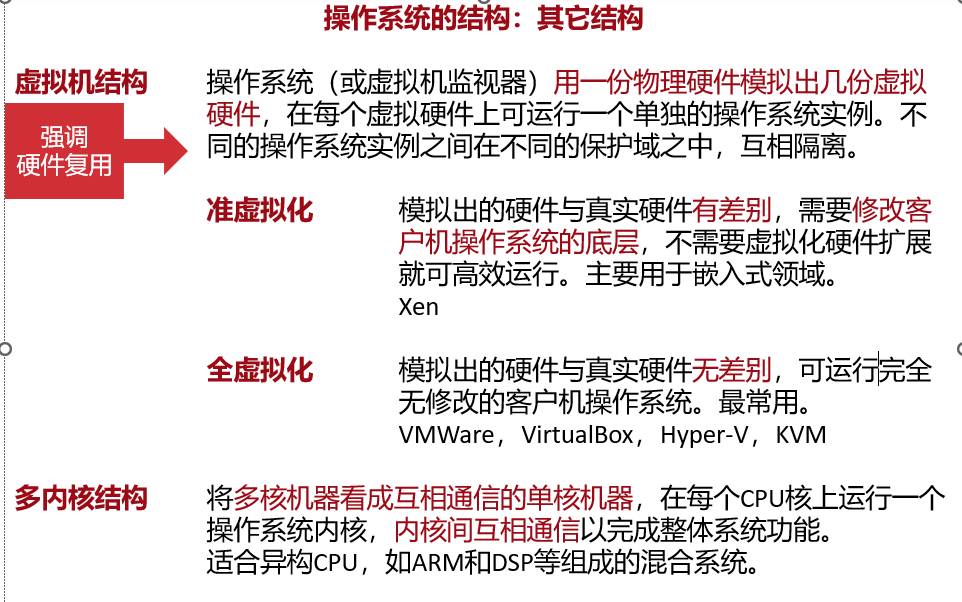

一些其他结构

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?