软件版本:Libero SOC V11.8;

实验测试目的:只读操作——读取RAM初始化时的数据;

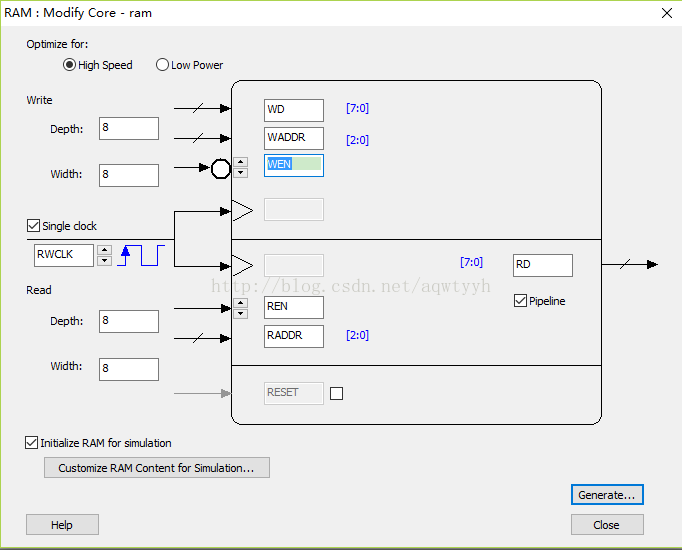

Two port RAM界面如上。

RWCLK:读写共用时钟,也可以选择独立时钟;

REN :读使能,高有效。也可以选择触发极性;

RADDR:读地址,需要自己写Verilog控制;

RD :读数据输出;

虽然只用到读功能,但是写部分的Width和Depth也要写,并且和读部分的Width和Depth相等;

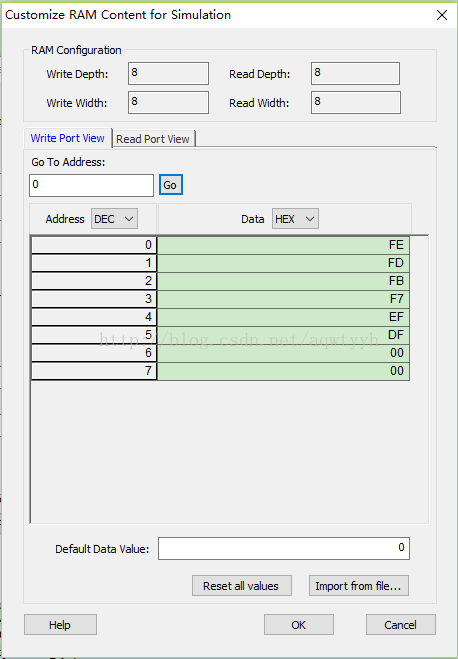

初始化数据在“Customize RAM Content for Simulaion”中写入,支持HEX等文件导入,但不支持.mif文件。

初始化框中的“Write port view”和“Read for view”,在初始化时数据写入任何一个view都行,你会发现当写入read for view时,write port view也会出现一样的数据。

Two port RAM的操作极其简单,一开始我想复杂了。只要给个时钟,给个恒定的REN就行了(除非你不想一直可以读数据,那就不要给REN恒定的高电平),再写一下简单的产生地址RADDR模块就行了。

Tips:1、RAM中不用的脚一定要接地;2、RESET脚只复位输出,并不复位初始化数据;

我的RAM例化代码:

module top(

input clk50m,

input rst_n,

output [7:0] data

);

wire clk;

syspll u_syspll(

.POWERDOWN(1),

.CLKA(clk50m),

.LOCK(),

.GLA(clk)

);

ram u_ram(

.WD(0),

.RD(data),

.WEN(0),

.REN(1),

.WADDR(0),

.RADDR(addr),

.RWCLK(clk)

);

wire [2:0] addr;

ctrl u_ctrl(

.clk(clk),

.rst_n(rst_n),

.addr(addr)

);

endmodule

顺便说一下:Actel的Libero SOC中的identify Debug不能实时反映板级调试数据,这一点很不好。

(Identify Debug类似于quartus的Signaltap)

282

282

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?