完成本实验后,您应该能够:

• 在现有 Verilog 设计中使用 VCS 中的竞态检查器实用程序定位竞态条件

• 找出现有 Verilog 设计中的仿真不匹配

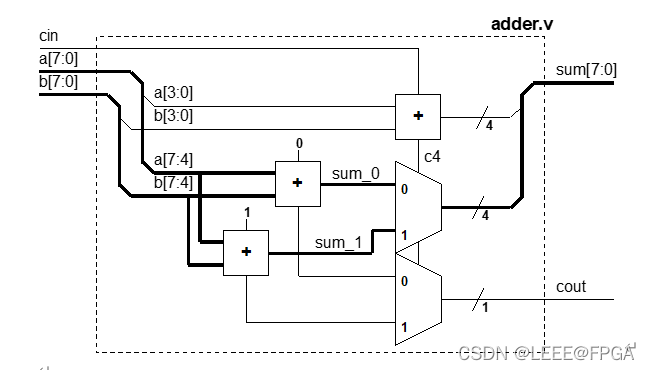

继续使用adder

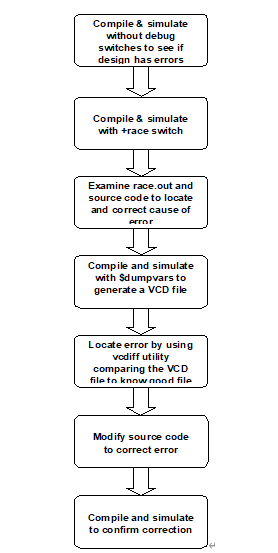

在实验室文件中,存在由竞争条件引起的错误。 目标是使用 VCS 来识别和定位竞争条件的原因。 一旦更正,您将重新编译和重新仿真以验证我们更正的功能。

这是您将要执行的操作的预览:

• 在 A 部分中,您将编译和仿真以查看加法器是否正确运行。 然后,我们将使用 +race 编译时开关并重新编译和重新仿真加法器。 通过检查race.out 文件并在源代码中定位竞争条件,您将能够做出适当的更正。

• 在 B 部分中,您将使用 $vcdpluson 进行编译以生成 VPD 转储文件。 检查 DVE 中的差异,您将找到竞态条件。 源代码将被修改。 最后你将重新编译和重新仿真,以验证加法器操作的正确性。

1实验流程

TASK1

任何调试过程的第一步都是在不使用调试开关的情况下编译和仿真设计以查看是否有任何错误。

订阅专栏 解锁全文

订阅专栏 解锁全文

2583

2583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?