学习中经常要用到将十进制数据转换为BCD码,算法比较简单,简单说明一下。

**BCD码:**4位二进制数来表示一位十进制数的编码,例如十进制数279,转换为BCD码就是’h177。

算法实现流程:二进制数据每次左移一位,每四位判断是否大于4,满足条件则加四,不满足继续移位。

Verilog实现:FSM状态机实现 32bit十进制数据输入

部分代码:

//==============================================================================

//状态机

//==============================================================================

always @(*)begin

case(r_current_state)

IDLE :

begin

if(en == 1’b1)

r_next_state = DATA_RECV;

else

r_next_state = IDLE;

end

DATA_RECV :

begin

if(en_dly1)

r_next_state <= SHIFT;

else

r_next_state <= DATA_RECV;

end

SHIFT :

begin

if(shift_cnt == SHIFT_DEPTH + 1)

r_next_state = DONE;

else

r_next_state = SHIFT;

end

DONE :

begin

r_next_state = IDLE;

end

default:

r_next_state = IDLE;

endcase

end

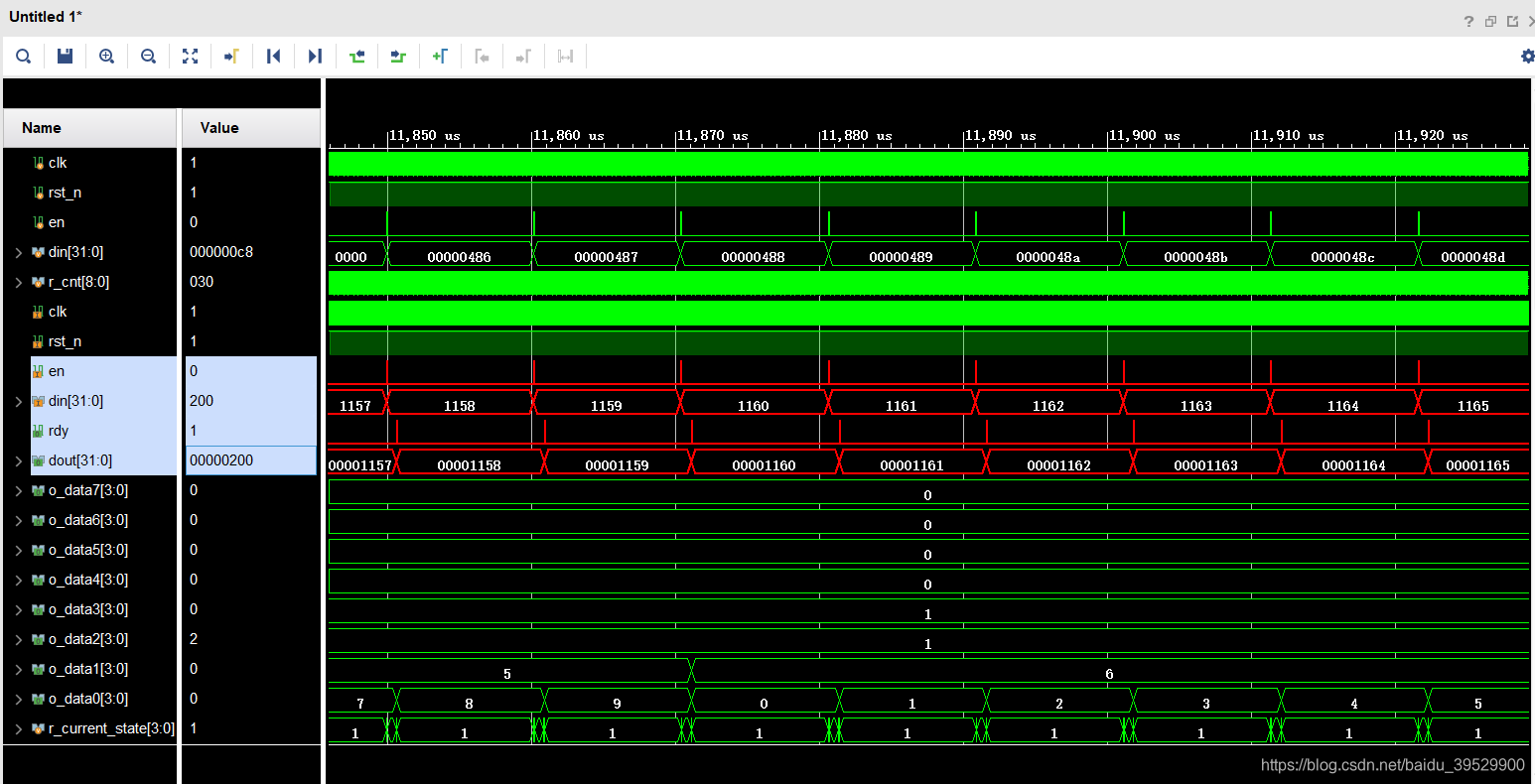

仿真结果:

8373

8373

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?