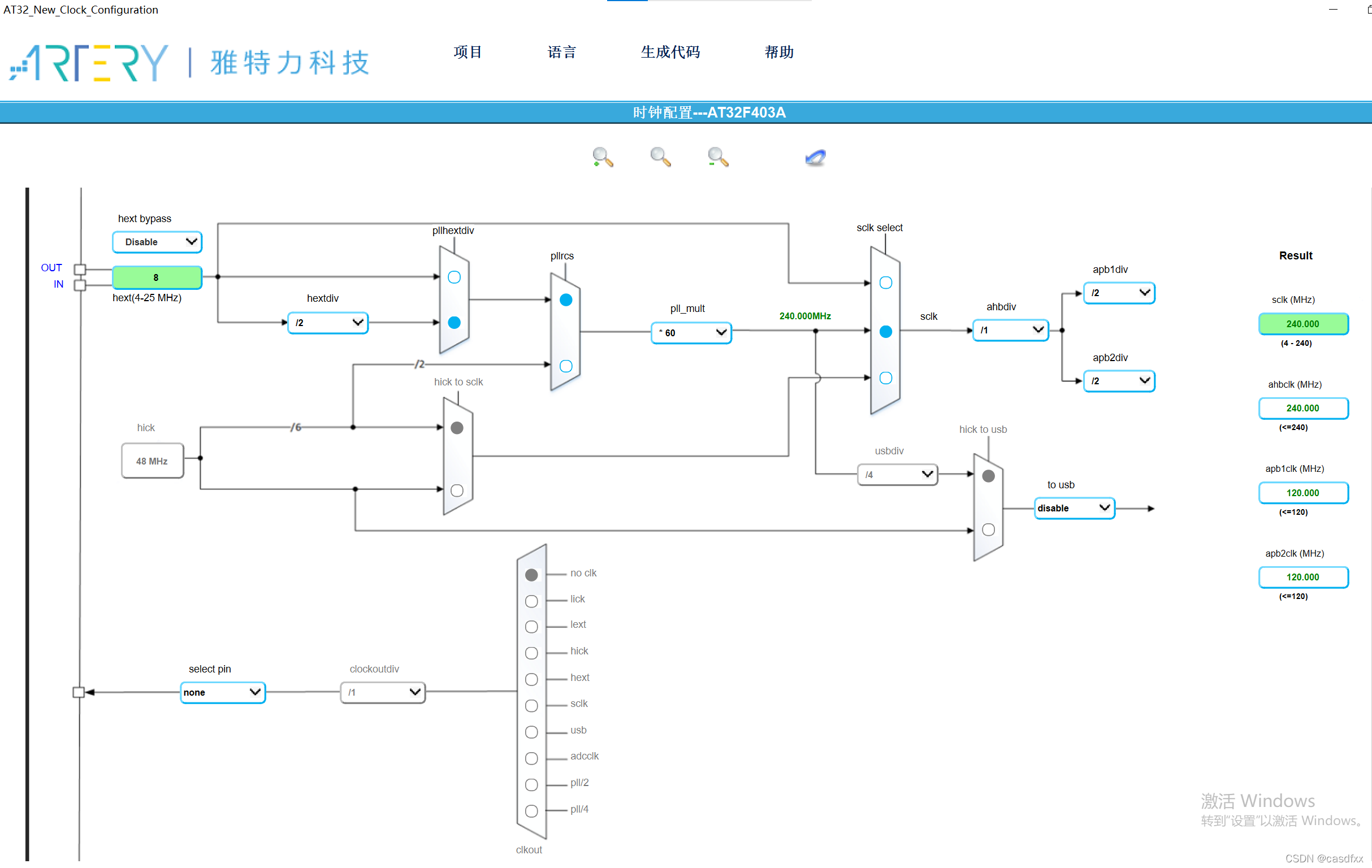

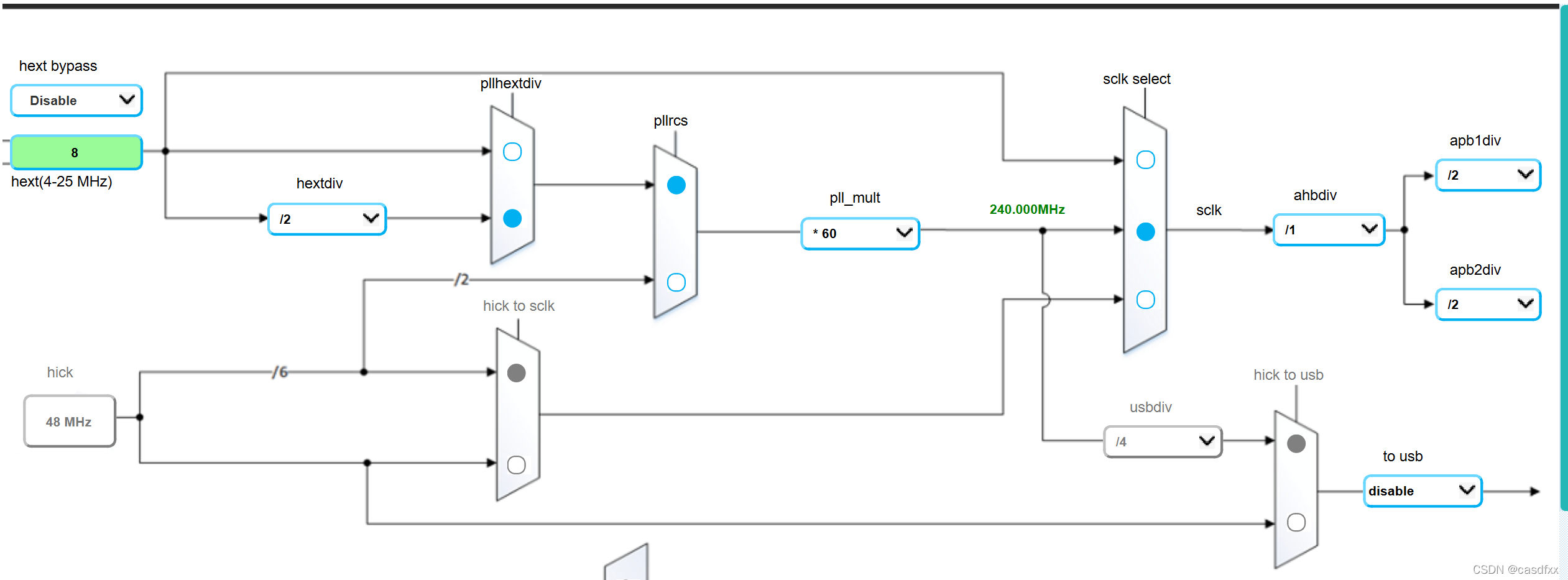

1、修改AHB主频

通过修改 at32f403a_407_clock.c 里的函数:

crm_pll_config(CRM_PLL_SOURCE_HEXT_DIV, CRM_PLL_MULT_60, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

1)、超频360MHz(程序无法运行)

crm_pll_config(CRM_PLL_SOURCE_HEXT, CRM_PLL_MULT_45, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

2)超频288MHz(程序可以运行)

试着往下降,CRM_PLL_MULT_42,CRM_PLL_MULT_40,CRM_PLL_MULT_38,CRM_PLL_MULT_36。

直到CRM_PLL_MULT_36可以运行。

crm_pll_config(CRM_PLL_SOURCE_HEXT, CRM_PLL_MULT_36, CRM_PLL_OUTPUT_RANGE_GT72MHZ);3) 将APB1、APB2频率上调

/* config apb2clk */

crm_apb2_div_set(CRM_APB2_DIV_1);

/* config apb1clk */

crm_apb1_div_set(CRM_APB1_DIV_1);发现没什么效果。

4)将XMC时序缩短

都减小为0,ILI9488 480*320的屏仍能正常显示

/* timing configuration */

xmc_norsram_timing_default_para_init(&rw_timing_struct, &w_timing_struct);

rw_timing_struct.subbank = XMC_BANK1_NOR_SRAM1;

rw_timing_struct.write_timing_enable = XMC_WRITE_TIMING_ENABLE;

//rw_timing_struct.addr_setup_time = 0x2;//缩短为0

rw_timing_struct.addr_setup_time = 0x0;

rw_timing_struct.addr_hold_time = 0x0;

//rw_timing_struct.data_setup_time = 0x2;//缩短为0

rw_timing_struct.data_setup_time = 0x0;

rw_timing_struct.bus_latency_time = 0x0;

rw_timing_struct.clk_psc = 0x0;

rw_timing_struct.data_latency_time = 0x0;

rw_timing_struct.mode = XMC_ACCESS_MODE_A;

w_timing_struct.subbank = XMC_BANK1_NOR_SRAM1;

w_timing_struct.write_timing_enable = XMC_WRITE_TIMING_ENABLE;

//w_timing_struct.addr_setup_time = 0x2;//缩短为0

w_timing_struct.addr_setup_time = 0x0;

w_timing_struct.addr_hold_time = 0x0;

//w_timing_struct.data_setup_time = 0x2;//缩短为0

w_timing_struct.data_setup_time = 0x0;

w_timing_struct.bus_latency_time = 0x0;

w_timing_struct.clk_psc = 0x0;

w_timing_struct.data_latency_time = 0x0;

w_timing_struct.mode = XMC_ACCESS_MODE_A;

xmc_nor_sram_timing_config(&rw_timing_struct, &w_timing_struct);

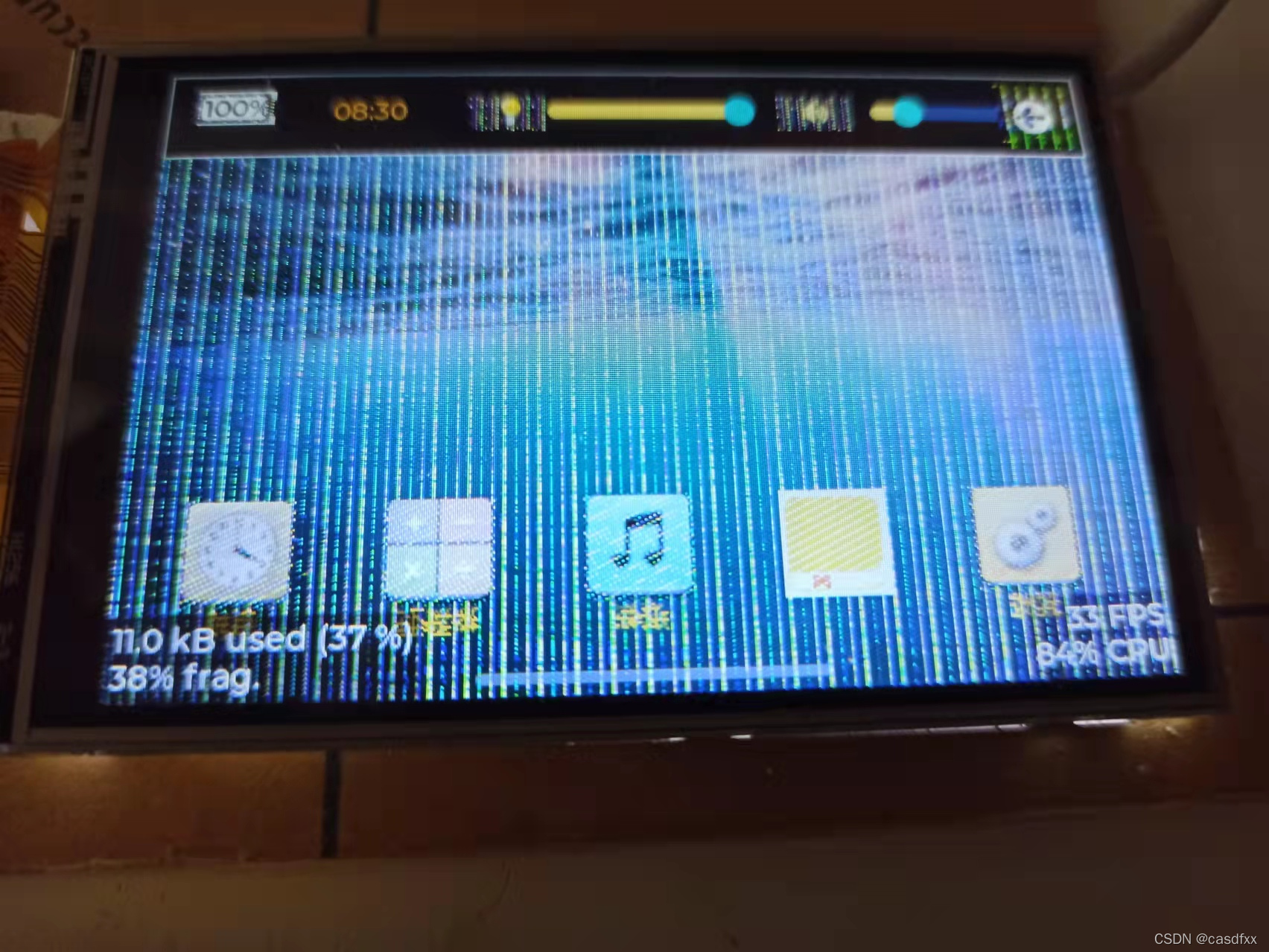

观察屏幕上显示的内容,大吃一惊。如下:

这应该是SPIM的问题。我把图片与字库都放在SPIM里了。

2、适用于SPIM的最高频率:

因为APB1与APB2超频后没什么感觉,所以就仍恢复以前的二分频。

1)只将AHP主频减小,如下:

crm_pll_config(CRM_PLL_SOURCE_HEXT, CRM_PLL_MULT_30, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

/* config hext division */

crm_hext_clock_div_set(CRM_HEXT_DIV_2);

发现比以前清楚多了,不过还是会出现一些不该出现的小点。

2 )

接着改为如下:

/* config pll clock resource */

crm_pll_config(CRM_PLL_SOURCE_HEXT_DIV, CRM_PLL_MULT_30, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

//crm_pll_config(CRM_PLL_SOURCE_HEXT, CRM_PLL_MULT_30, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

/* config hext division */

crm_hext_clock_div_set(CRM_HEXT_DIV_2);与1)中的一样。其实原理上主频也应该相同。

3)

/* config pll clock resource */

crm_pll_config(CRM_PLL_SOURCE_HEXT_DIV, CRM_PLL_MULT_30, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

//crm_pll_config(CRM_PLL_SOURCE_HEXT, CRM_PLL_MULT_30, CRM_PLL_OUTPUT_RANGE_GT72MHZ);

/* config hext division */

crm_hext_clock_div_set(CRM_HEXT_DIV_2);

这样显示就正常了。不过是以牺牲主频为代价的。此时主频为120MHz。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?