提升性能的编码方式

对高性能设计而言,本章节中讨论的编码方法 (提升性能的编码方法)能够减少潜在的时序问题。

关键路径上的高扇出

高扇出网络宜在设计进程早期阶段进行处理。性能要求和路径的结构往往会导致高扇出问题。您可以使用以下技术来

解决高扇出网络的问题。

建议:

在综合后使用

report_high_fanout_nets

Tcl

命令识别高扇出网络。随着流程进入实现过程,您可以监测这

些网络对设计性能的影响。

在不需要高扇出网络的设计部分精简负载

对高扇出控制信号,评估设计的所有编码部分是否都需要高扇出网络。减少负载数量可以大幅度减少时序问题。

使用寄存器复制

寄存器复制可以通过复制寄存器来加快关键路径的速度,以减少给定信号的扇出。这便于实现工具更加灵活地对各类

不同负载和相关逻辑进行布局布线。综合工具广泛采用了这种方法。

大多数综合工具使用扇出阈值限值来自动判定是否需要复制寄存器。降低全局阈值,就可以自动复制高扇出网络。但

是,降低全局阈值不能控制对哪些寄存器进行复制以及如何将它们的负载进行分组。此外,全局复制机制不能准确评

估时序裕量,进而导致不必要的复制单元、逻辑占用率增加以及潜在功耗增加。

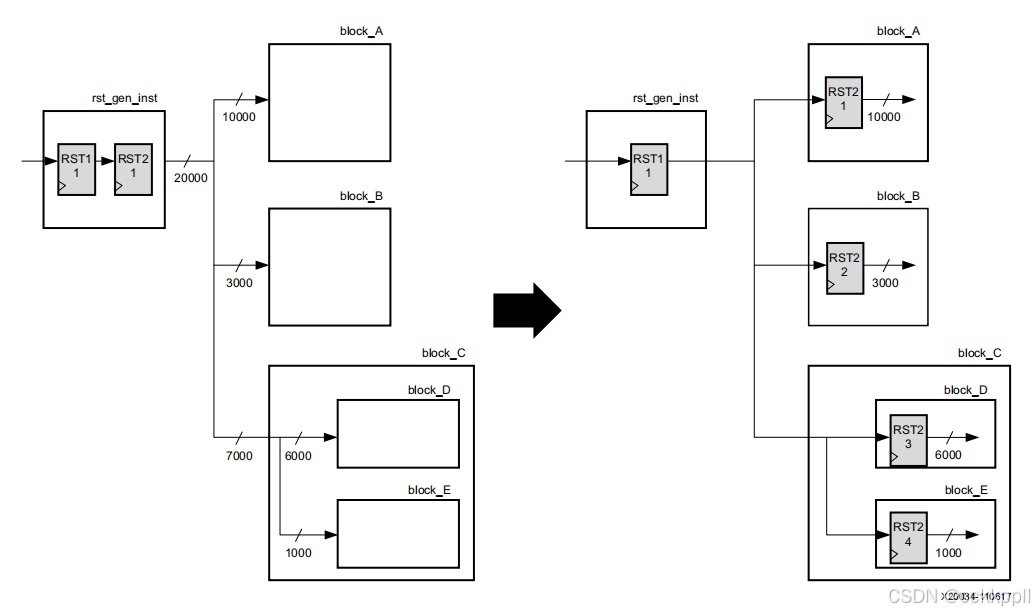

通常,减少扇出的更好方法是对高扇出信号使用平衡树。考虑基于设计层级手动复制寄存器,因为包括在层级中的单

元通常布局在一起。例如,在下图所示的平衡复位树中,高扇出复位

FF RST2

在

RTL

中复制以平衡不同模块之间的扇

出。如果需要,物理综合可以基于布局信息执行进一步的复制以改进

WNS

。

提示:

要在综合中保留重复寄存器,请使用

KEEP

属性,而不是

DONT_TOUCH

。

DONT_TOUCH

属性阻止在实现流程

中稍后的物理优化期间的进一步优化。

注释:

如果发现复制的是

LUT1

而不是寄存器,就说明不正确地应用了属性或约束。

建议:

将

MAX_FANOUT

属性用于全局高扇出信号会导致与在综合中降低全局扇出限制时类似的次优复制结果。基于这

个原因,赛灵思建议仅在支持中低扇出的本地信号上使用层级内部的

MAX_FANOUT

。

请勿复制寄存器用于同步跨时钟域的信号。如果在这些寄存器上添加

ASYNC_REG

属性就会造成工具无法复制寄存器。如

果同步链有极高扇出且又必须使用复制来满足时序要求,则需在没有

ASYNC_REG

约束的同步链之后添加额外的寄存器。

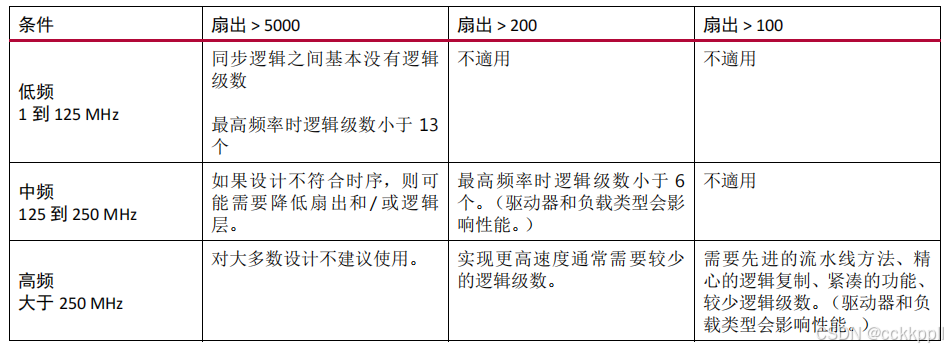

下表是您设计中可接受的扇出数量提示性指南。

提示:

如果时序报告提示高扇出信号将限制设计性能,应考虑使用诸如

opt_design -hier_fanout_limit

、

place_design

和

phys_opt_design

等实现工具选项对其进行复制。

提示:

当复制寄存器时,应采用惯例对其命名,例如

<original_name>_a

,

<original_name>_b

等,以便轻松理

解复制的意图,从而更易于对

RTL

代码进行维护。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?