一、IO类型

(1)配置专用IO

| 名称 | 功能 |

|---|---|

| CFGBVS | 配置bank电压选择 |

| M[2:0] | 配置模式选择 |

| TCK | JTAG标准信号,Test Clock |

| TMS | JTAG标准信号,Test Mode Select |

| TDI | JTAG标准信号,Test Data In |

| TDO | JTAG标准信号,Test Data Out |

| PROGRAM_B | 配置逻辑复位信号,能触发新的配置过程 |

| INIT_B | 双向,输出能指示初始化和错误,输入能停止加载过程 |

| DONE |

指示配置完成 |

| CCLK | 配置始时钟 |

(2)多功能IO

| 名称 | 功能 |

|---|---|

| PUDC_B | 低有效使能IOB内部上拉电阻(在上电之后,配置结束之前) |

| EMCCLK | 外部主控配置时钟输入 |

| CSI_B | SelectMap 片选输入 |

| CSO_B | 片选输出 |

| DOUT | 数据输出 |

| RDWR_B | SelectMap数据总线方向控制 |

| D00_MOSI | Master SPI下的MOSI,BPI下的D00 |

| D01_DIN | Master SPI下的MISO,BPI下的D01 |

| D[00-31] | 数据总线,不同模式使用不同 |

| A[00-28] | 地址总线,不同模式使用不同 |

| FCS_B | Flash片选输出 |

| FOE_B | Flash输出是能输出 |

| FWE_B | Flash写使能输出 |

| ADV_B | 地址有效 |

| RS[0:1] | 版本选择,可以选择高位地址总线作为加载起始 |

| VCCBATT | 外部电池供电输入 |

多功能管脚在配置过程结尾的GTS失效之后,就变成用户IO,默认情况下就是DONE拉高后的一个时钟周期之后,用户IO可以对其进行操作。例如一个BPI FLASH接在了这些Multi-Function IO,在上电之后通过这些接口进行FPGA的配置,及配置成功结束之后,用户可以自由访问这些接口,对BPI FLASH进行读写擦操作。

(3)用户IO

用户IO也分为设计工程中使用的IO和未使用的IO。

二、不同阶段

(1)上电到配置之前

该场景讨论不是很多,一般都是上电-初始化,然后直接进去配置过程。可以认为在该过程中管脚的状态和配置过程中是一致的。

(2)配置过程中

配置过程中,配置专用输入IO的电平取决于VCCO_0,可以是LVCMOS15/18/25/33,配置专用输出IO的电平为VCCO_0,12mA驱动,fast slew rate。专用配置管脚中只有TDO、INIT_B、DONE、CCLK是可以作为输出的。TDO需要接菊花链中下个FPGA的TDI或者接JTAG接口的TDO,其电平状态取决与FPGA内部JTAG操作状态,INIT_B为open_drain(漏极开路)双向接口,当作为输出时,只能输出高阻和0,如果需要输出1,则需要额外的上拉电阻,xilinx也是建议通过小于4.7K的上拉电阻到VCCO_0,DONE也是漏极开路的双向IO,该管脚内部存在10K的上拉。CCLK在Master配置模式下是输出,Slave模式下是输入,JTAG模式下是高阻。

配置过程中,多功能管脚的电平要与外部连接的器件一致,由VCCO_14/15来决定,也是LVCMOS,12mA驱动,fast slew rate,内部上下拉状态由PUDC_B决定。

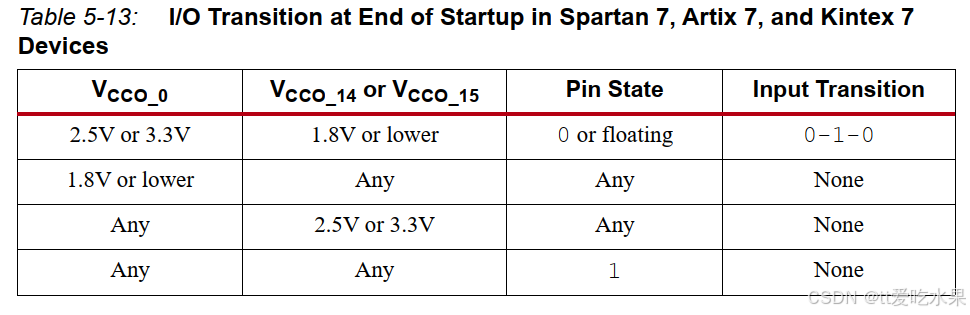

7系列中除V7外,多功能配置管脚存在一个特殊情况:

就是在VCCO_14/15为1.8V或更低的时候,如果输入管脚为0或悬空,则该管脚会在EOS之后有一个CFGCLK时钟周期的高脉冲,因为此时已经配置完成,所以这个可能会对FPGA内部逻辑产生影响。

普通用户IO的状态取决与PUDC_B。

(3)配置成功完成后

配置完成之后,专用管脚的电平可以由vivado进行配置上下拉,下面会给出。

多功能管脚变成了普通IO管脚,状态与普通IO管脚一致。

设计中使用的用户IO管脚状态由设计决定,每个输出或双向IO都可以设置内部上下拉,在没有驱动的时候决定管脚的状态:

set_property KEEPER true [get_ports <ports>]

set_property PULLDOWN true [get_ports <ports>]

set_property PULLUP true [get_ports <ports>]

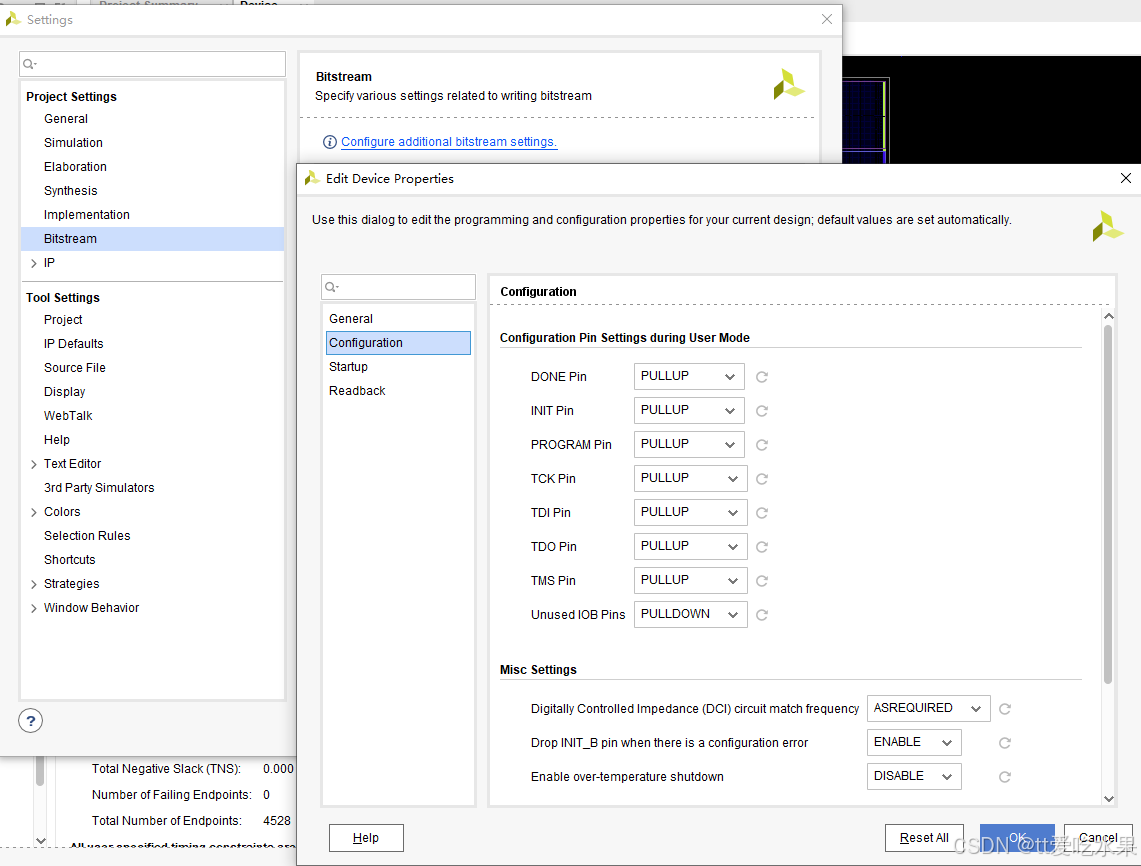

设计未使用的管脚状态可以由vivado中设置上下拉,生成bit完成之后,open implemented design,然后点Tool-Setting-Bitstream-Configure additional bitstream settings:

或者是在XDC中加入:

set_property BITSTREAM.CONFIG.UNUSEDPIN Pulldown [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullnone [current_design]

默认是Pulldown

另外就是在给Flash烧程序的时候,也会让你选择管脚的上下拉状态,那个也是选择配置完成之后,unused pin的状态。

三、一表总结

| pin类型\阶段 | 上电后配置前 | 配置中 | 配置后 | |

|---|---|---|---|---|

| 专用IO | PUDC_B | PUDC_B | 设置 | |

| 多功能IO | PUDC_B | PUDC_B | 设置 | |

| 用户IO | 使用的IO | PUDC_B | PUDC_B | 设计决定 |

| 未用的IO | PUDC_B | PUDC_B | 设置 | |

2128

2128

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?