FPGA调试心得

一、下载到板子上却是没有反应

用modelsim仿真,看看功能是否正确,测试文件应该要尽可能多的考虑各种问题。建议下载到板子之前要先做功能仿真。

二、当代码写完后,仿真通过后,下载到板子上却是没有反应,可以尝试以下方法

a)仔细的看看警告的信息,没有错误并不代表就是正确的,还要看看警告的信息,

1)对那些一直为低或者为高的要注意,看看你是否真的想让他一直为高,如果不是的话,就要去看看源代码,看看他为什么会一直为高或者低。

2)对于一些位宽不匹配的也要注意一下,看看是否是位宽定义不对。

3)模糊连接的就是信号没有定义,回到源码,去定义一下就可以了

4)产生了锁存器,如果不是自己想要的产生的就要去修改一下源码了

b)检测clk,rst_n,以及引脚绑定是否正确。这个可以看Pin Planner

c)检测计数器位宽是否正确

d)查看RTL_view,看看框图是否是自己想要的,从宏观上检测连线等

e)使用Signal Tap 在线调试,看看具体的波形。

f)input / output是否正确,不单单是顶层需要检查,子模块的端口也要检查。

g)以上还不行就得考虑时序了,这个就得用到时序分析了,看看建立时间和保持时间是否符合要求。

三、如果系统比较大的话,可以单独的测试各个小功能模块。总之不要心急,不要慌。

写代码一定要小心,要规范,下载到板子前最好先仿真。端口输入输出要想清楚,位宽什么的要数清楚。

四、调试实例

在做sdram时,仿真没有问题,但是下载到板子就是一点反应都没有,下面我将详细讲一下调试的过程。

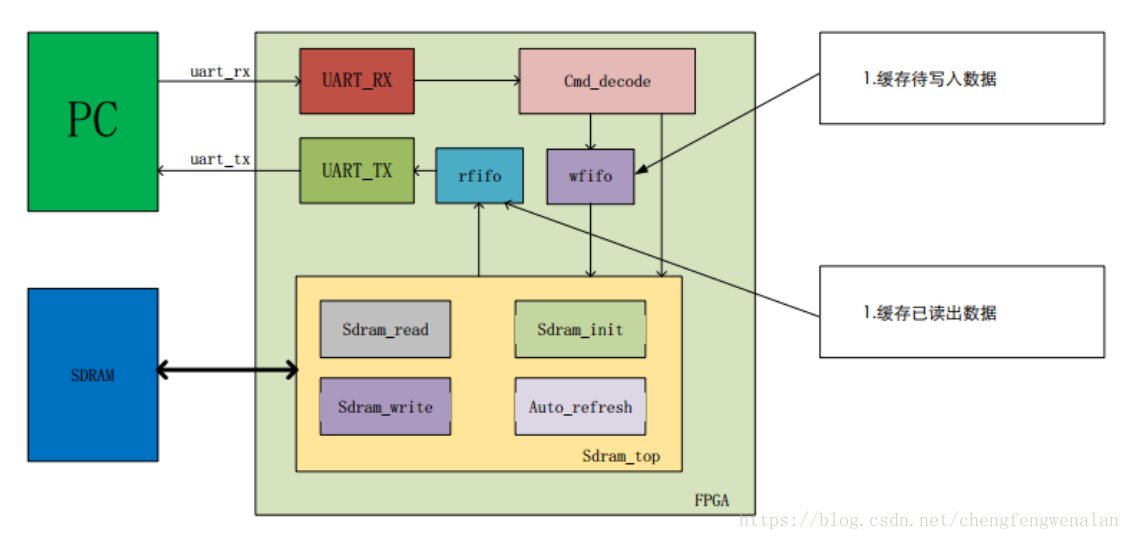

被调试的项目框图如下:

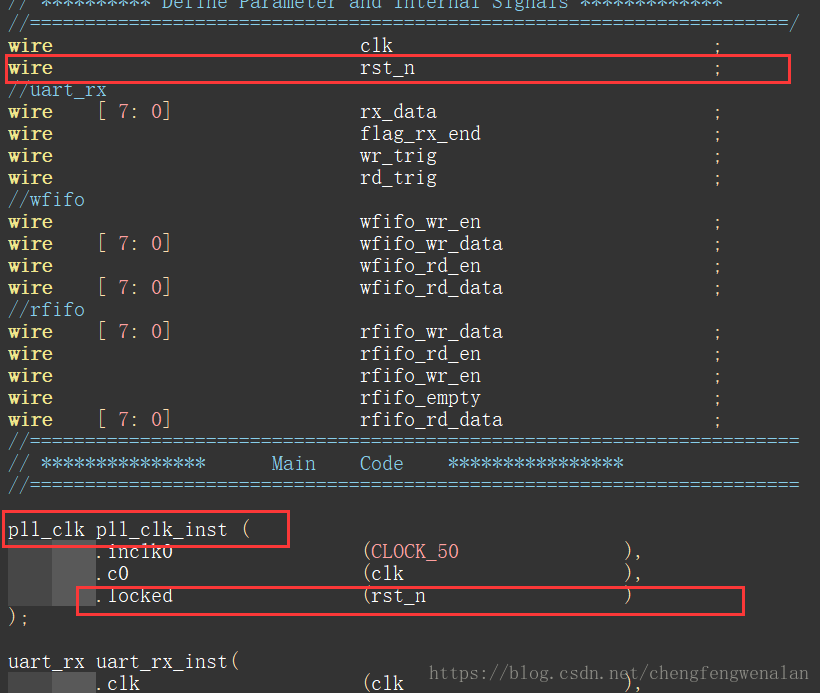

1)下载到板子没有反应,给我的第一感觉就是检查一下clk和rst_n引脚有没有绑定正确,于是便于检查了一下顶层文件,果然rst_n没有定义,对于复位信号,可以采用“异步复位,同步释放”(外部按键)的方法,也可以采用pll的locked做为复位,我这里就采用了pll的locked做为复位端了,去工程里调用一下pll的ip核,在顶层模块例化一下就ok了。

2)修改完第一步后,再重新全编译一遍,然后发现还是没有反应,则开始查看一下警告信息

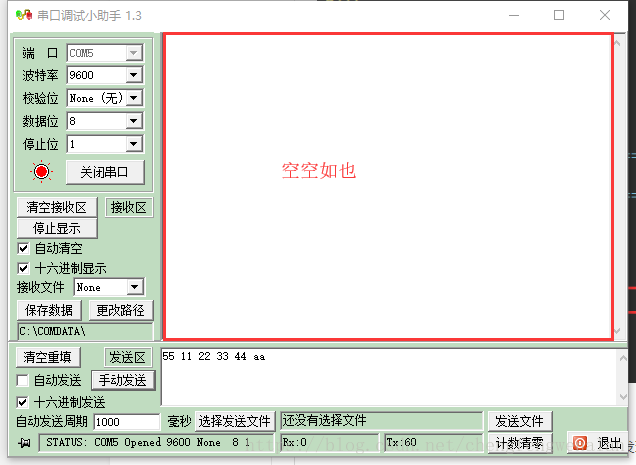

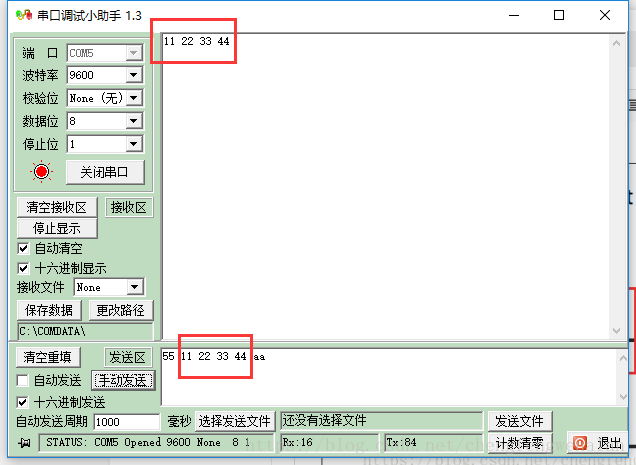

因为没有反应,clk和rst_n都已经检测好了,所以这个时候要去检测和pc最先接触的那个模块,于是我便开始去检测串口的接收模块,看看接收是否正确,首先查看一下警告信息

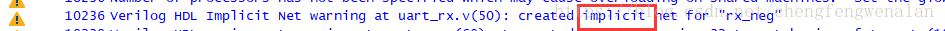

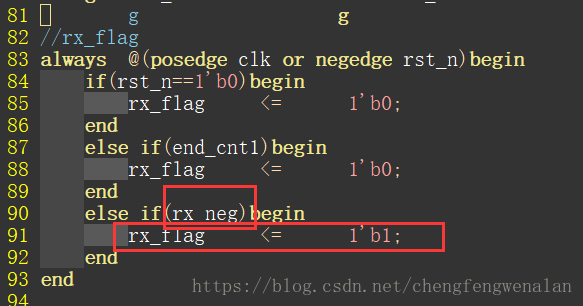

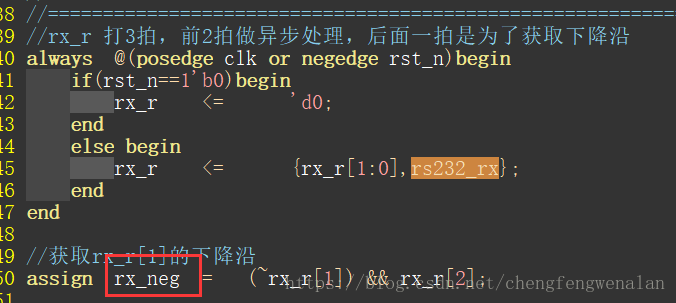

发现有个rx_neg是含蓄的信号,这个就是说rx_neg没有定义,去源码查看一下,给它定义一下就可以了。继续看警告

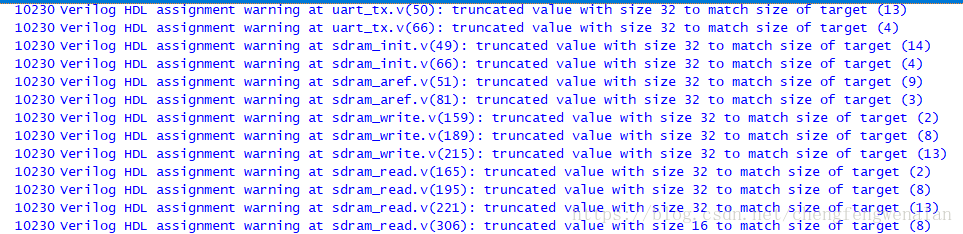

发现有很多位宽不匹配的警告,双击警告看看是什么回事

发现是由于+1这个“1”没有说明位宽,就默认32位了,然后编译器就把它截取以适配cnt0的位宽,那个是正确的,所以可以忽略这个警告

继续看警告,

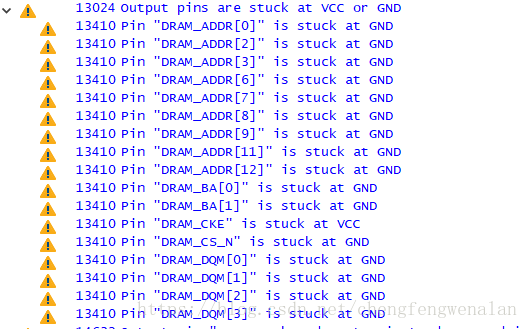

这些保持为低或者高的信号是我自己所需要的,所以也可以忽略

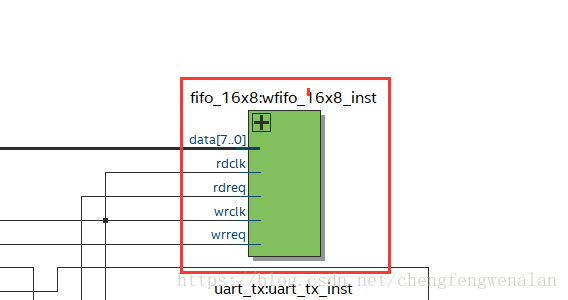

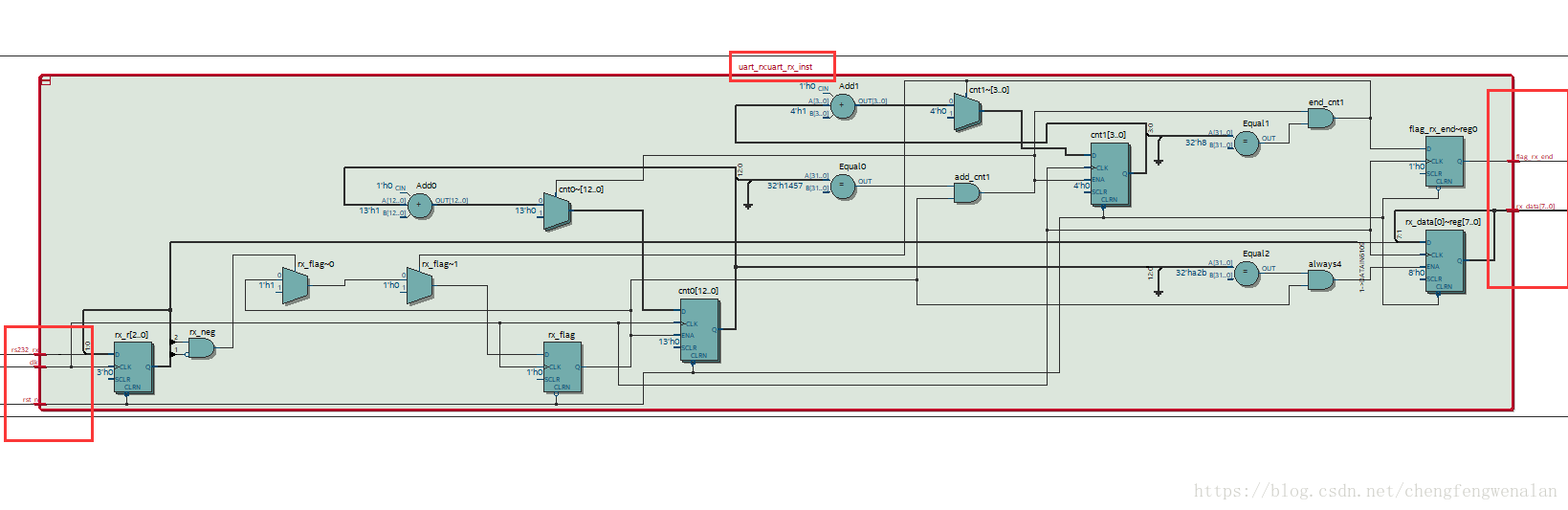

3)查看RTL_view,看看是否有连线不对,或者端口输入输出不对

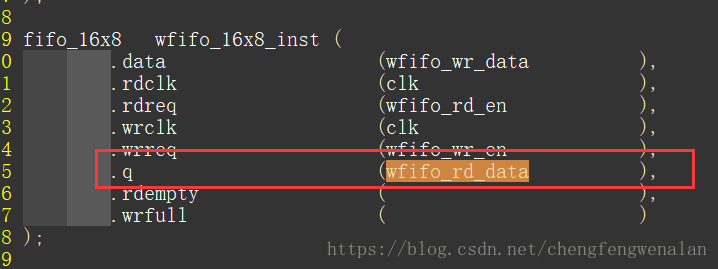

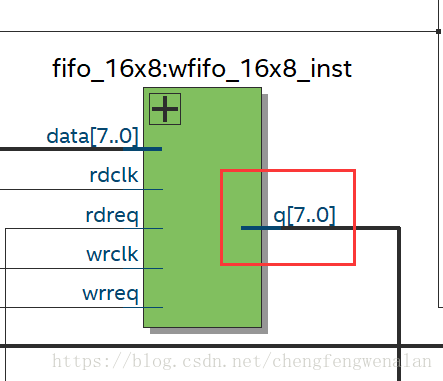

一下子就看了这个wfifo_16x8_inst的模块没有输出,说明他的端口定义或者连线可能有问题,故查看一下源码

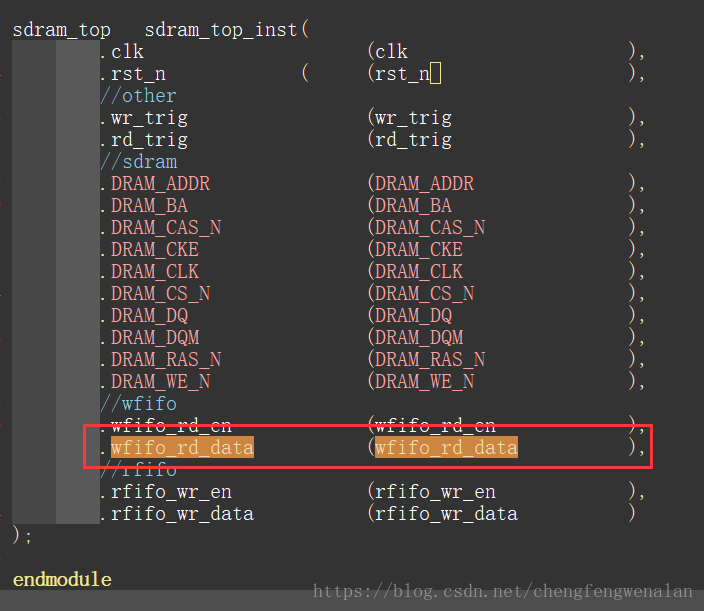

发现这个wfifo_rd_data连到了wfifo的q端(输出端),所以可以确认是wfifo_rd_data出问题了,

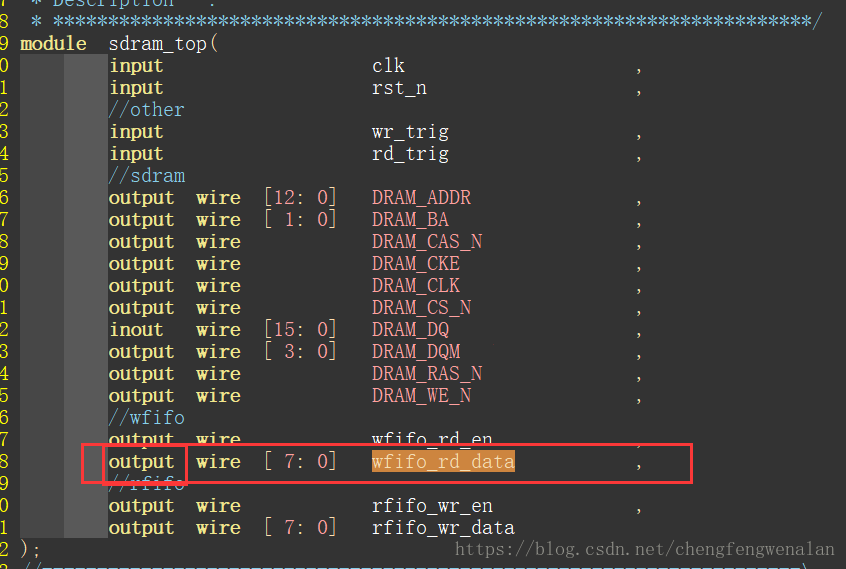

一路追踪下来发现是sdram_top的wfifo_rd_data的端口输入输出方向定义错了,把output改成input就可以了

顶层的框图已经没有问题了,继续查看RTL_view,查看子模块

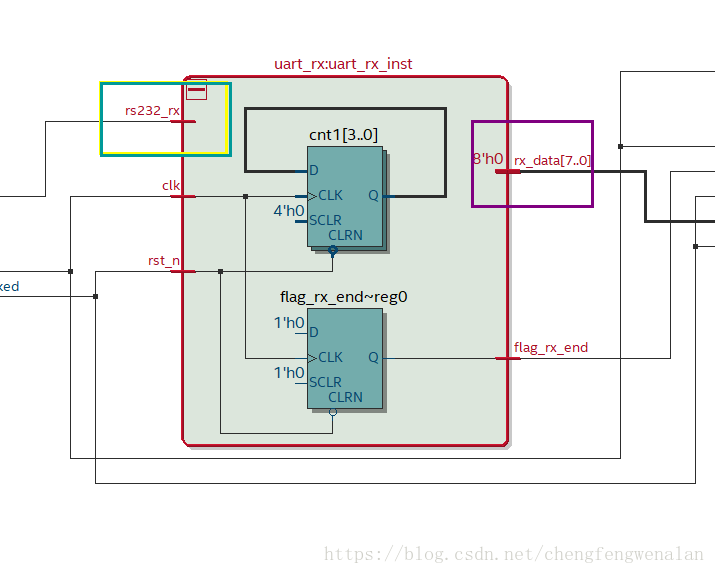

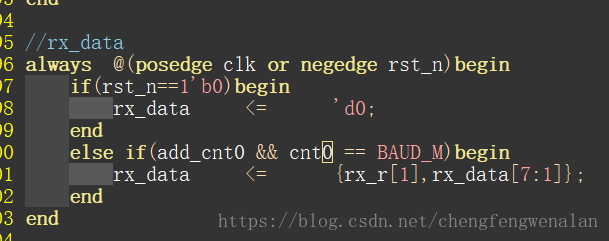

发现rx_data[7..0]一直为0,故查看他的源码,这里就可以体现出了一个信号一个always的好处了,对调试是很好用的,

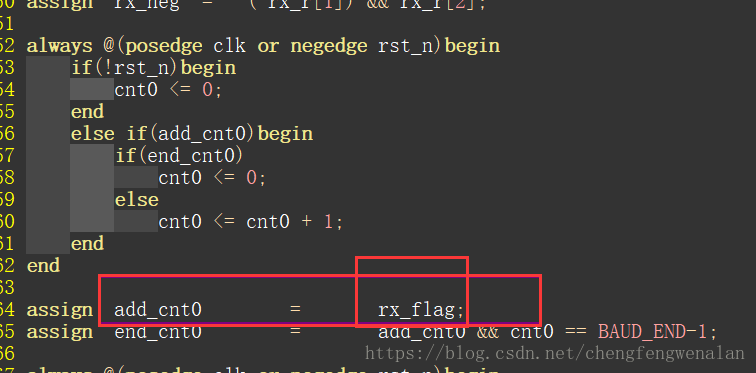

rx_data一直为0,说明add_cnt0 && cnt0 == BAUD_M 一直为假,先追踪add_cnt0,看看这个信号是否有问题

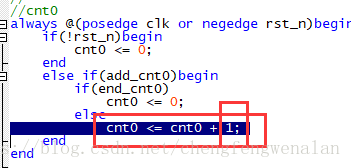

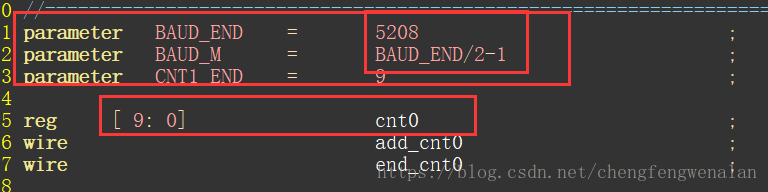

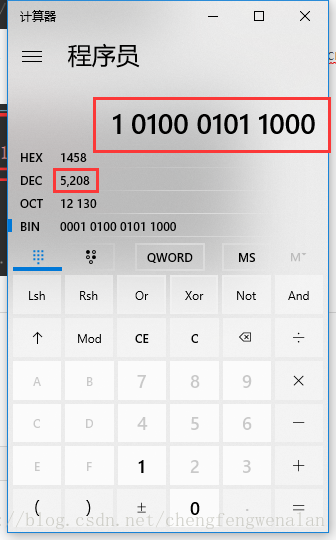

结果发现add_cnt0没有问题。故cnt0 == BAUD_M这个条件有问题了,稍微有点经验就会反应过来,这个很大可能是因为cnt0的位宽不够,导致他不可能计数到BAUD_M

结果发现真的是位宽写出了,手贱一下把算错了位宽,

5208应该用13位的,所以把9改成12就可以了(其实这个仿真时是好的,因为我仿真的时候是通过参数重定义了,把BAUD_END重定义为28了,所以仿真没有发现问题),继续查看RTL_view,没有发现其他问题。故重新全编译一遍。

编译完了发现之前那些警告消除了,再查看一下RTL_view的uart_rx以及wfifo的框图是否正确

发现框图基本都正确了,这个时候再下载到板子试试。

总算出来了,大功告成,圆满结束。哈哈,其实如果还出不来就只能用signal tap慢慢的调试一波了,再不行的话就得考虑时序分析,建立时间和保持时间是否满足。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?