以前的学习的时候,没有用过verilog中的for循环。在数字电路的课堂上,也经常会想循环电路到底是一个什么样的电路呢?在我的脑海中,感觉循环电路就像那种重复利用已知电路的电路,我是这样理解的:for循环语句块中的执行语句是一样的,其生成的电路也是一样的,这个电路我把 它交做执行电路。那么循环电路是不是就是根据条件判断运行执行电路呢,就是那种类似于负反馈电路。根据执行电路输出的一个结果来决定下次 是否要还要继续运行执行电路。

module Pro(

input clk,

input rst_n,

input[12:0] data,

output[3:0] numout

);

reg[3:0] i;

reg[3:0] num;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

num = 'd0;

i = 'd0;

end

else begin

num = 'd0;

for(i = 'd0;i <= 12;i = i + 1)

if(data[i])

num = num + 1;

end

end

assign numout = num;

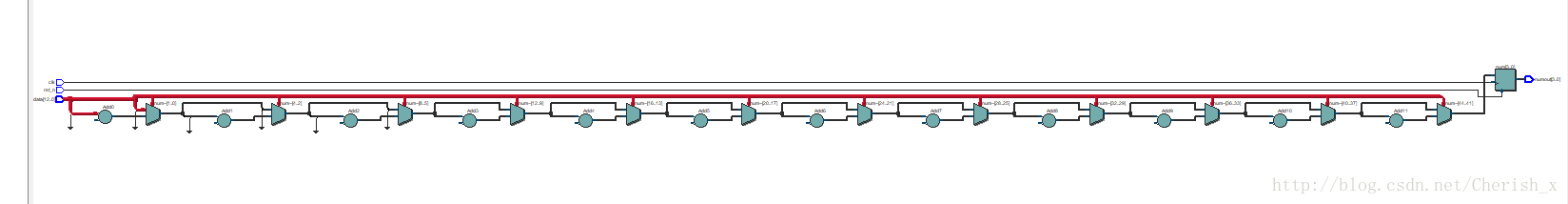

endmodulefor循环生成的RTL图如下:

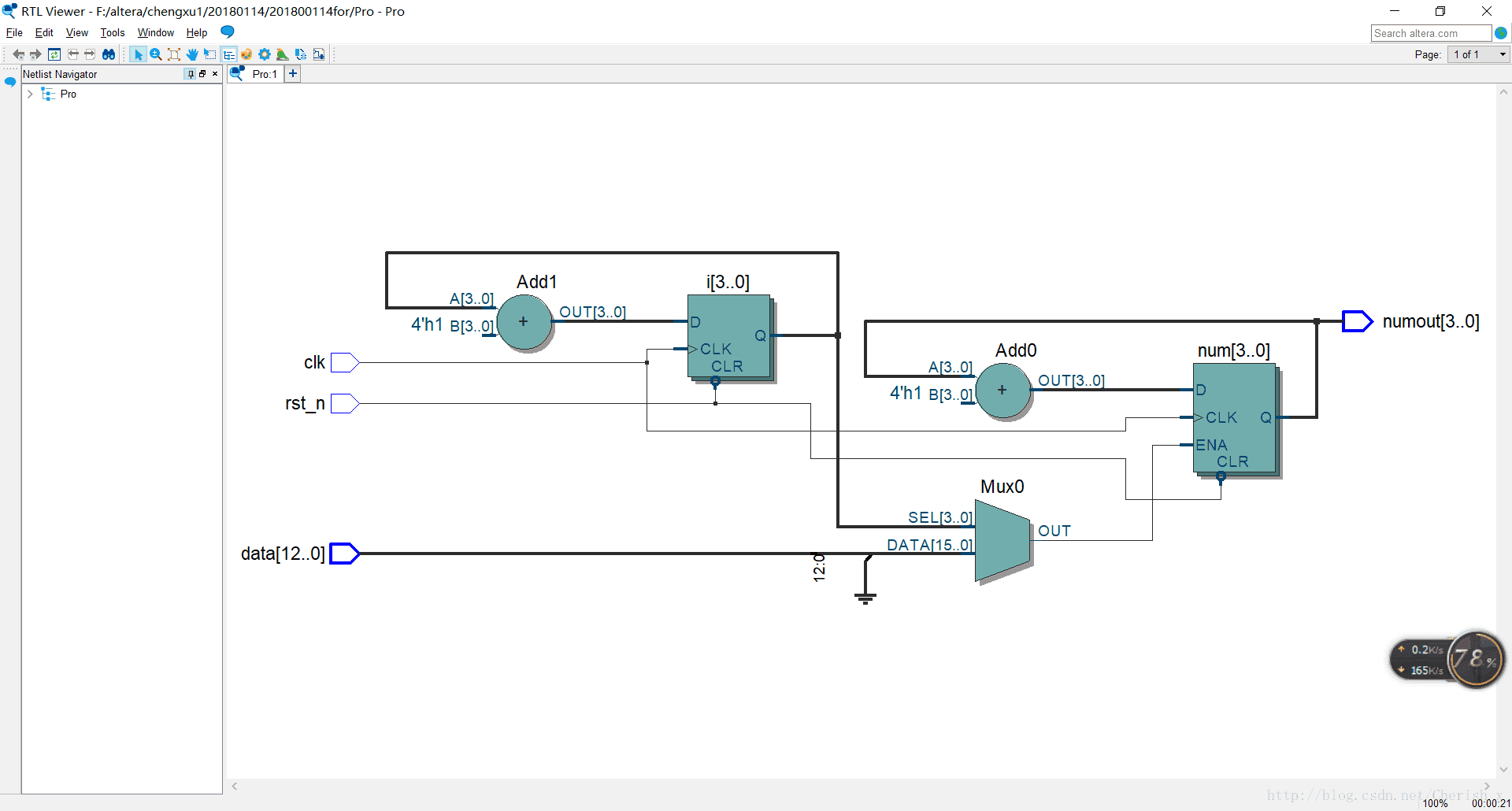

一个时钟周期检测一次的RTL图如下:

事实结果和我想的相差太远,反而是一个时钟周期检测一次的电路和我想的一样。我们可以看到for循环电路虽然节省了时间,但是占用的资源也明显较多。

在实际应用中,我们到底应该不应该大胆的使用for循环呢?

我自己的观点:当你只考虑速度而不关心电路的话,是可以使用for循环的。

6237

6237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?