使用Verilog代码编写的串口接收程序:

数据位8位,停止位1位,校验位没有,流控没有

波特率由波特率模块生成

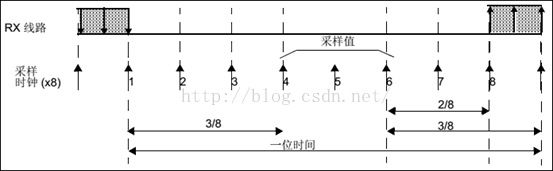

串口时序大致如下图所示:

module uart_recv(GClk,clk_bps,reset,rx_en,Rxd,datain,rx_ok);

input GClk,clk_bps,reset,rx_en,Rxd;

output [7:0]datain;

output rx_ok;

//neg_rx:__/\______________________________

//rx_ok:_________________________________/^\_

//rx_en:^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^

//RxAv:____/^^^^^^^^^^^^^^^^^^^^^^^^^^^^\___

wire clk_bps;

reg [7:0]data;//接收数据缓存

reg [7:0]data_temp;

reg

本文介绍了一种使用Verilog编写的串口接收程序,配置为8位数据位,1位停止位,无校验位和流控,波特率由专用模块生成。通过时序图理解串口通信过程。

本文介绍了一种使用Verilog编写的串口接收程序,配置为8位数据位,1位停止位,无校验位和流控,波特率由专用模块生成。通过时序图理解串口通信过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

403

403

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?