名称:信号延迟电路设计Verilog代码ISE Xilinx CPLD开发板(文末获取)

软件:ISE

语言:Verilog

代码功能:

信号延迟电路设计

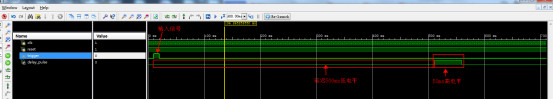

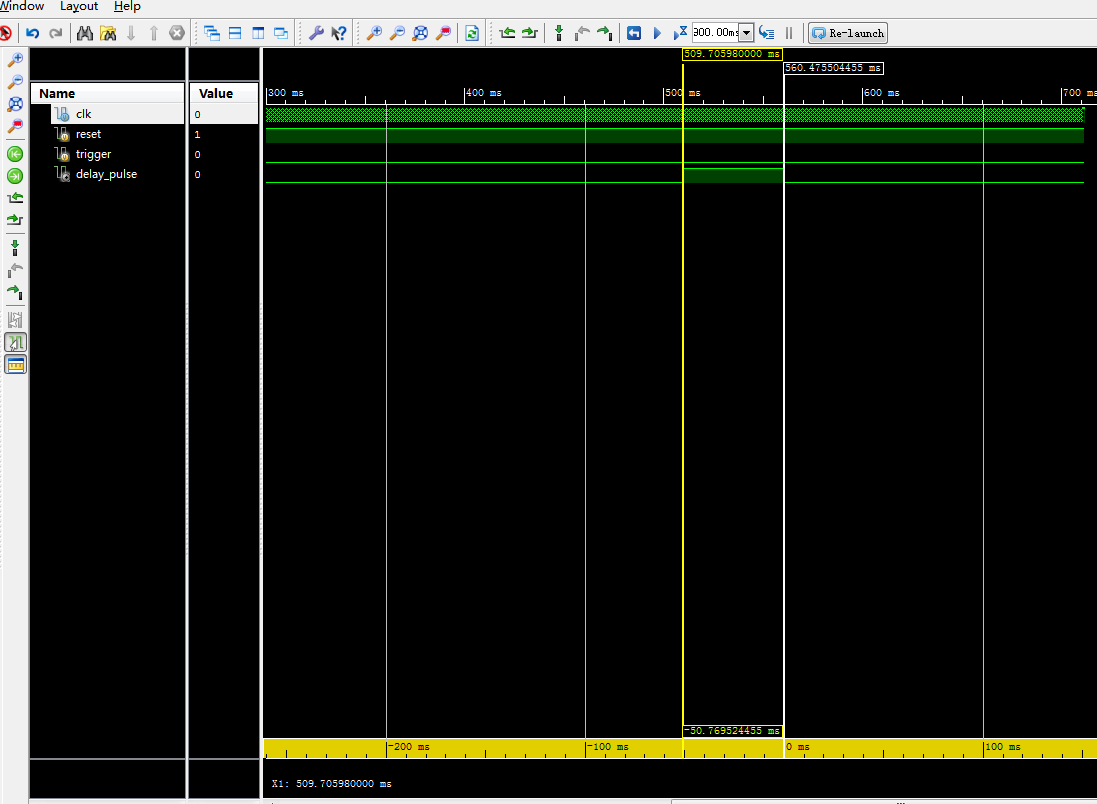

检测一个输入信号的高电平,延迟500ms再输出这个高电平信号,高电平持续50ms

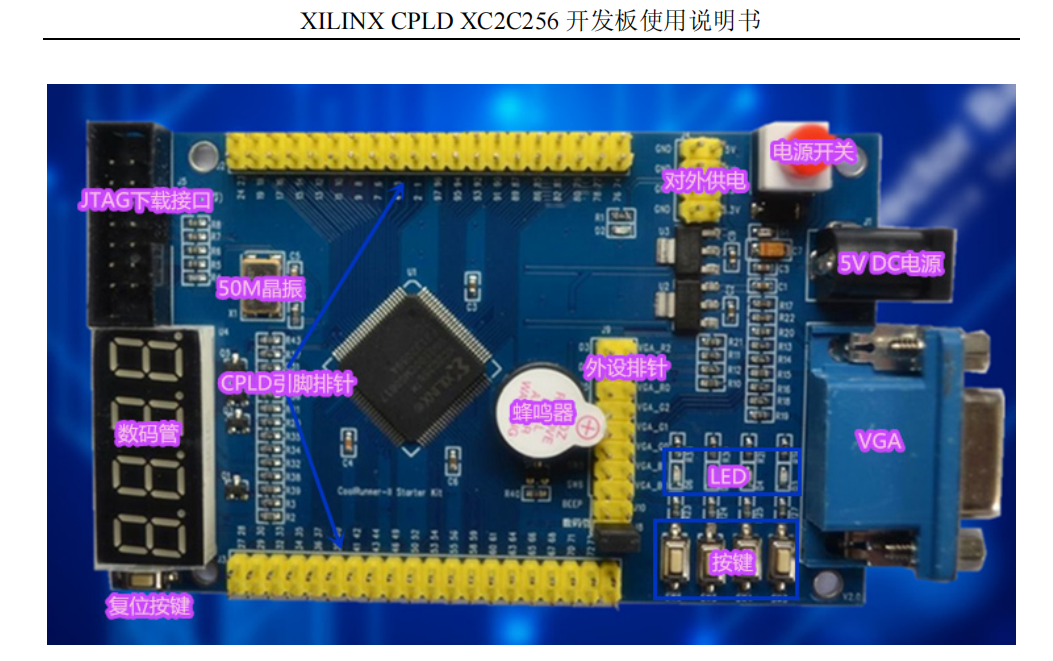

本代码已在Xilinx CPLD开发板验证,Xilinx CPLD开发板如下,其他开发板可以修改管脚适配:

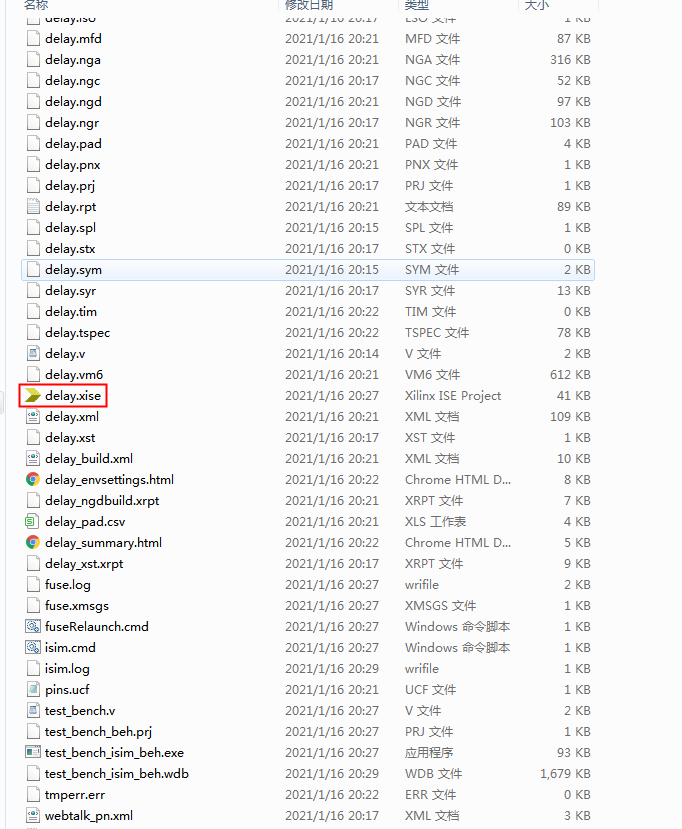

1. 工程文件

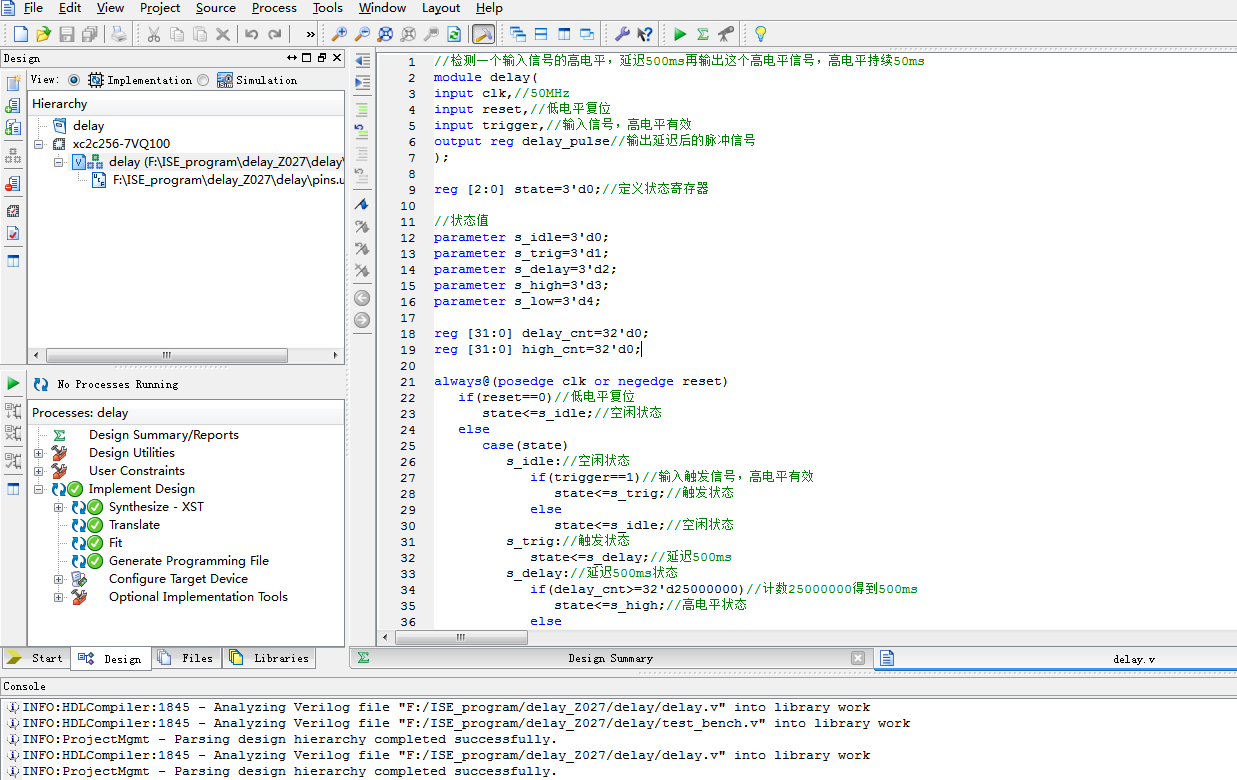

2. 程序文件

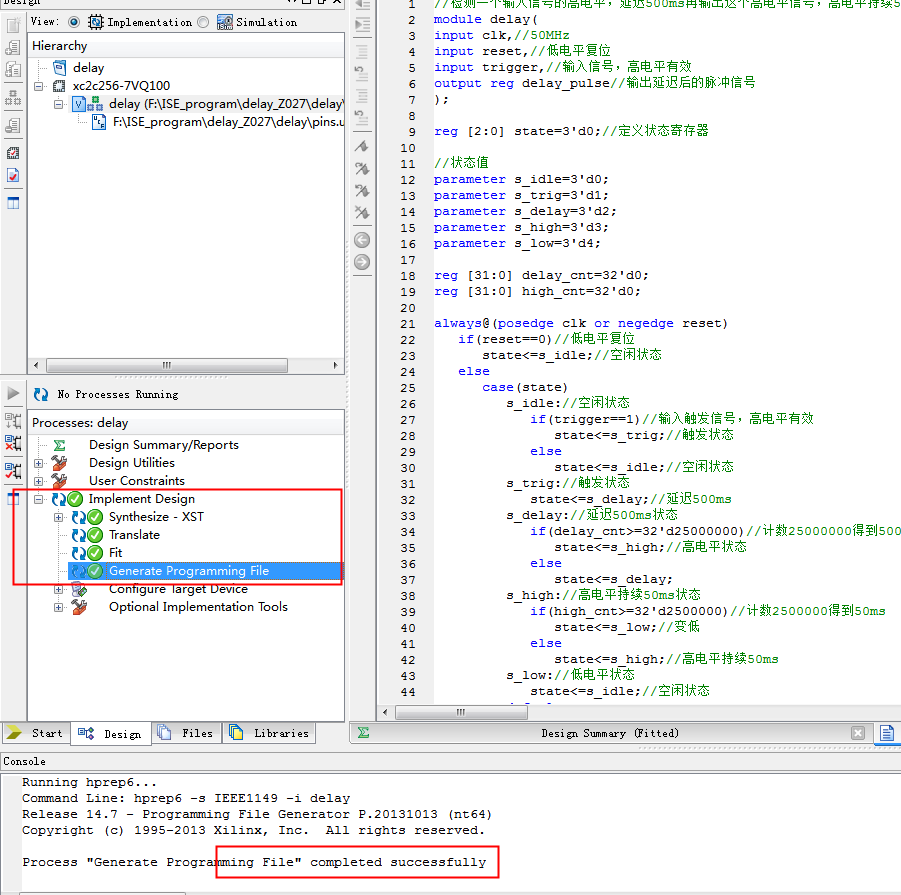

3. 程序编译

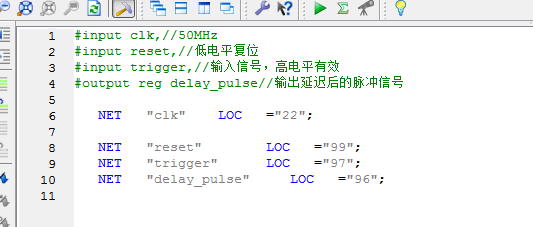

4. 管脚分配

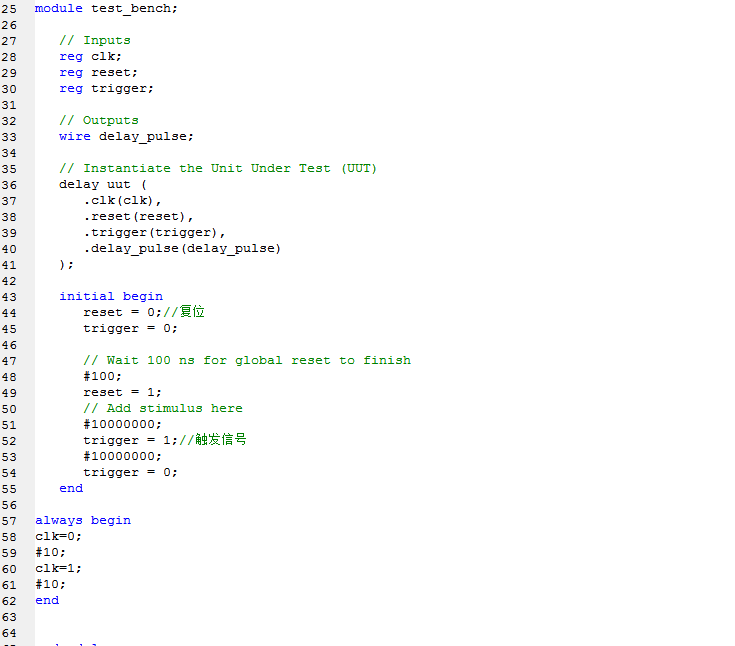

5. Testbench

6. 仿真图

部分代码展示:

//检测一个输入信号的高电平,延迟500ms再输出这个高电平信号,高电平持续50ms module delay( input clk,//50MHz input reset,//低电平复位 input trigger,//输入信号,高电平有效 output reg delay_pulse//输出延迟后的脉冲信号 ); reg [2:0] state=3'd0;//定义状态寄存器 //状态值 parameter s_idle=3'd0; parameter s_trig=3'd1; parameter s_delay=3'd2; parameter s_high=3'd3; parameter s_low=3'd4; reg [31:0] delay_cnt=32'd0; reg [31:0] high_cnt=32'd0; always@(posedge clk or negedge reset) if(reset==0)//低电平复位 state<=s_idle;//空闲状态 else case(state) s_idle://空闲状态 if(trigger==1)//输入触发信号,高电平有效 state<=s_trig;//触发状态 else state<=s_idle;//空闲状态 s_trig://触发状态 state<=s_delay;//延迟500ms s_delay://延迟500ms状态 if(delay_cnt>=32'd25000000)//计数25000000得到500ms state<=s_high;//高电平状态 else state<=s_delay; s_high://高电平持续50ms状态 if(high_cnt>=32'd2500000)//计数2500000得到50ms state<=s_low;//变低 else state<=s_high;//高电平持续50ms s_low://低电平状态 state<=s_idle;//空闲状态 default:; endcase always@(posedge clk or negedge reset) if(reset==0)//低电平复位 delay_cnt<=32'd0; else if(state==s_delay)//延迟500ms状态,计数

源代码

点击下方的公众号卡片获取

3202

3202

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?