ARM coretex_m3内核支持256个中断和可编程256级中断优先级设置。

Stm32的NVIC是coretex_m3的NVIC的子集。

Stm32目前支持84个中断和16级可编程中断优先级。仅使用中断优先级设置8位中的高四位。

每个中断对应一个外围设备,每个外围设备包括许多个引起中断的中断源或中断事件。这些中断源与中断事件都要通过指定的中断通道向内核申请中断。中断通道的优先级确定设备整体的优先级,而设备本身的多个中断执行顺序由用户的中断服务程序决定。

Stm32的68个外部中断通道固定分配给相应的外部设备。每个终端通道都具备自己的中断优先级控制字节PRI_n(8位,用高四位),每四个通道构成一个32位优先级寄存器。总共17个32位的优先级寄存器。

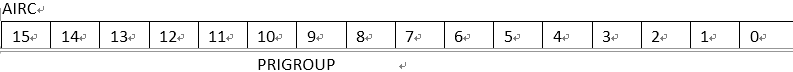

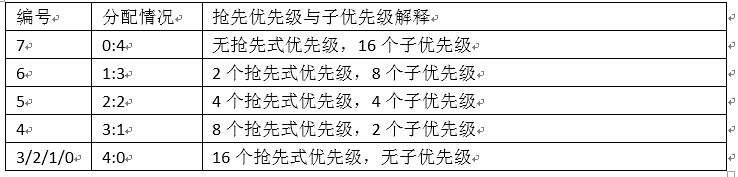

上表中断优先级寄存器的配置需在初始化时写入到一个32位寄存器AIRC(Application Interrupt and Reset Control Register)的第[10:8]这三位中,这三位叫做PRIGROUP。

假如写入的是0x04(即011)到PRIGROUP中,则有8个抢先式优先级和两个子优先级。

当上电Reset后,寄存器AIRC中的PRIGROUP值为0,既有16个抢先优先级,无子优先级。

对于某一个外部中断通道,有相应的控制字和控制位,用于单独的和总的控制该中断通道:

中断优先级控制字:PRI_n;

中断允许设置位:在ISER寄存器中;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1998

1998

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?