传统数据存储介质有磁带、光盘等,但更多的是硬盘(HDD,Hard Disk Drive)。随着数据呈爆炸式增长,对数据存储介质在速度上、容量上有更高的要求。时势造英雄,固态硬盘(Solid State Disk,SSD)横空出世。SSD使用电子芯片存储数据,没有HDD的机械式部件,因此在速度、时延、功耗、抗震等方面,与HDD相比有碾压式优势。无论是个人存储,还是企业存储,都在逐渐用SSD取代HDD。大数据时代,SSD必将是主角。

第1章 SSD综述

SSD(Solid State Drive),即固态硬盘,是一种以半导体闪存(NAND Flash)作为介质的存储设备。和传统机械硬盘(Hard Disk Drive,HDD)不同,SSD以半导体存储数据,用纯电子电路实现,没有任何机械设备,这就决定了它在性能、功耗、可靠性等方面和HDD有很大不同。

注:NAND是一个英文缩写,全称为“NotAnd”,它是一种电路逻辑,是反逻辑的基础,它的功能是当两个输入信号同时为高电平时,输出信号为低电平,而当其中一个输入信号为低电平时,输出信号为高电平,其结构为一个门(与非门),可以把它看作是一个反向的AND门,也就是说,当两个输入信号同时为高电平时,输出信号为低电平。

1.1 引子

SSD是一种以半导体为主要存储介质、外形和数据传输接口与传统的HDD相同的存储产品。目前主流SSD使用一种叫闪存的存储介质,未来随着存储半导体芯片技术的发展,它也可以使用更快、更可靠、更省电的新介质,例如3D XPoint、MRAM等。当前业界主要使用的还是闪存。

外观上,加上铝盒的2.5寸的SSD,和2.5寸HDD外观基本相同。除了有传统HDD的2.5寸和3.5寸的外观外,SSD还可以有更小的封装和尺寸,图1-2所示为M.2接口的SSD。

图1-2 SSD外观(左:2.5寸盘;右:M.2SSD) 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

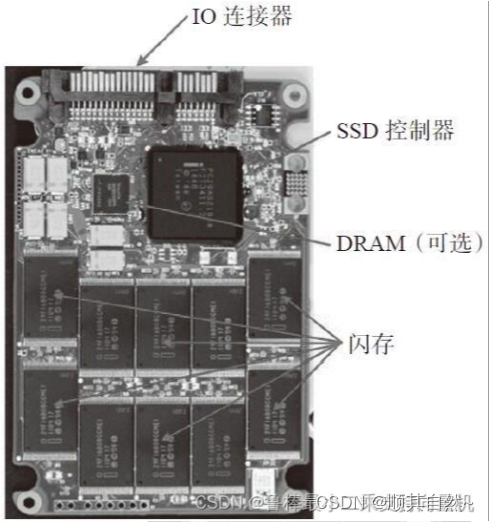

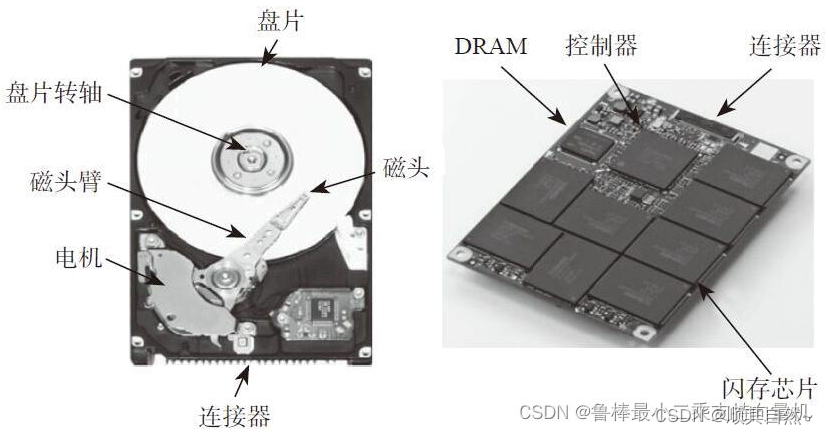

SSD是用固态电子存储芯片阵列制成的硬盘,主要部件为控制器和存储芯片,内部构造十分简单。详细来看,SSD硬件包括几大组成部分:主控、闪存、缓存芯片DRAM(可选,有些SSD上可能只有SRAM,并没有配置DRAM)、PCB(电源芯片、电阻、电容等)、接口(SATA、SAS、PCIe等),其主体就是一块PCB,如图1-3所示。软件角度,SSD内部运行固件(Firmware,FW)负责调度数据从接口端到介质端的读写,还包括嵌入核心的闪存介质寿命和可靠性管理调度算法,以及其他一些SSD内部算法。SSD控制器、闪存和固件是SSD的三大技术核心。

图1-3 SSD结构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

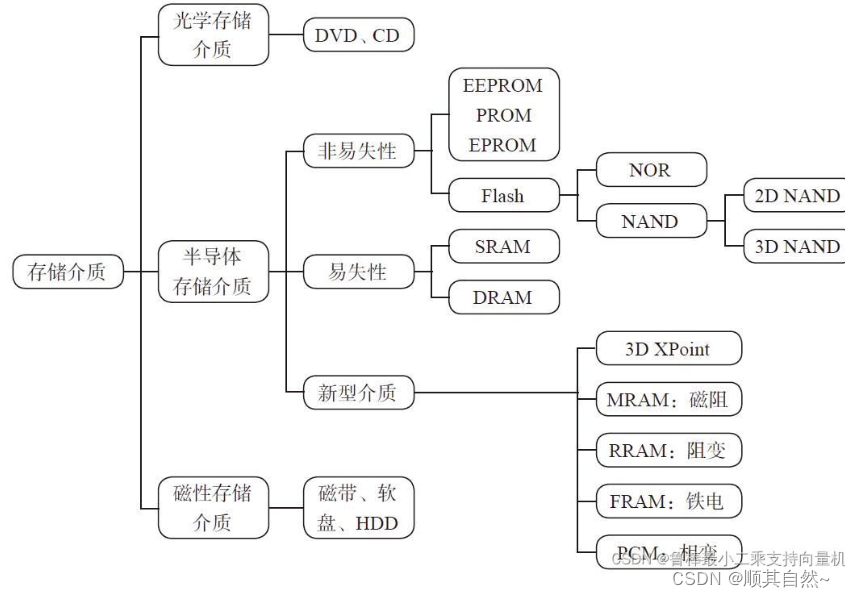

存储介质按物理材料的不同可分为三大类:光学存储介质、半导体存储介质和磁性存储介质。光学存储介质,就是大家之前都使用过的DVD、CD等光盘介质,靠光驱等主机读取或写入。在SSD出现之前,个人和企业的数据存储还是HDD的天下,HDD是以磁性存储介质来存储数据的;SSD出现以后,采取的是半导体芯片作为存储介质。现在及未来技术变革最快和主要方向还是半导体存储,从图1-4可以看出,半导体存储介质五花八门,目前可以看得出的主要方向还是闪存、3D XPoint、MRAM、RRAM等

图1-4 存储介质分类 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.2 SSD vs HDD

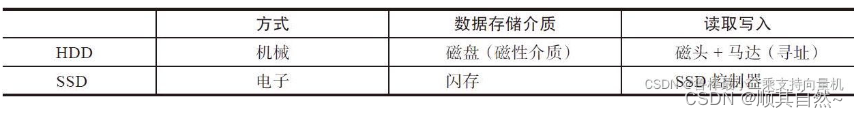

传统的HDD是“马达+磁头+磁盘”的机械结构,SSD则变成了“闪存介质+主控”的半导体存储芯片结构,两者有完全不同的数据存储介质和读写方式。对比如表1-1所示

表1-1 HDD vs SSD结构对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

SSD和HDD物理结构的不同,如图1-5所示

图1-5 SSD vs HDD结构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

SSD与HDD相比具有如下优点

性能好:表1-2所示某两款SSD和HDD的对比,读写速度有从几倍到几百倍的差异,随机读写性能差异最为明显。

功耗低:工作功耗HDD为6~8W,SATA SSD为5W,待机功耗SSD可降低到毫瓦(mW)级别。关于功耗,业界定义有几类:峰值功耗(Peak Power)、读写功耗(Active Power)、空闲功耗(Idle Power)、省电功耗(启动SSD内部休眠,尽可能多地关掉不工作的硬件模块,专业上定义为Standby/Sleep Power和DevSleep Power)。HDD与SSD的功耗对比如表1-3所示,从SSD功耗分解来看,读写功耗主要消耗在闪存上。数据读取和写入并发在后端的闪存,闪存的单位读写功耗是决定性的。

抗震防摔:SSD内部不存在任何机械部件,相比HDD更加抗震。HDD是机械式结构,磁头和磁片之间发生跌落时接触碰撞会产生物理损坏,无法复原。SSD是电子和PCB结构,PCB加半导体芯片,跌落时不存在机械损伤问题,因此更加抗震和可靠。另外SSD对环境的要求没有HDD那么苛刻,更适合作为便携式笔记本、平板电脑的存储设备。从可靠性角度来看,物理上的损伤以及带来数据损坏的概率,SSD比HDD更低。

噪声:客观上,由于结构上没有马达的高速运转,SSD是静音的。

身形小巧百变:HDD一般只有3.5寸和2.5寸两种形式,SSD除了这两种,还有更小的可以贴放在主板上的M.2形式,甚至可以小到芯片级,例如BGA SSD的大小只有16mm×30mm,甚至可做得更小

表1-2 HDD与SSD性能对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

表1-3 HDD与SSD功耗对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.3 固态存储及SSD技术发展史

StorageSearch是一家专门讲述各大固态存储公司产品的网站,本节中SSD发展史大部分内容来自于该网站的一篇文章:SSD Market History - Charting the Rise of the SSD Market (1970s to2019) the original article on StorageSearch.com

1 昂贵的RAM SSD时代

1976年,Dataram公司开始出售叫作Bulk Core的SSD,容量是2MB,使用了8块大电路板,每个板子有18个256KB的RAM。RAM的优点是可以随机寻址,就是每次可以只读写一个字节的数据,速度很快;缺点也很明显,掉电数据就没了,价格还巨贵。在以后的20多年时间里,TMS(Texas Memory Systems)、EMC、DEC等玩家不断推出各种RAM SSD。

2 机械硬盘(HDD)称霸世界

1988年费尔和格林贝格尔发现了巨磁阻效应,这个革命性的技术使得HDD容量变得很大,在各大企业的推广下,HDD进入千家万户。2013年全球卖出了5.7亿块HDD,市场为320亿美金。但是,HDD已经过了最鼎盛的时代。

3 闪存——源于华人科学家的发明

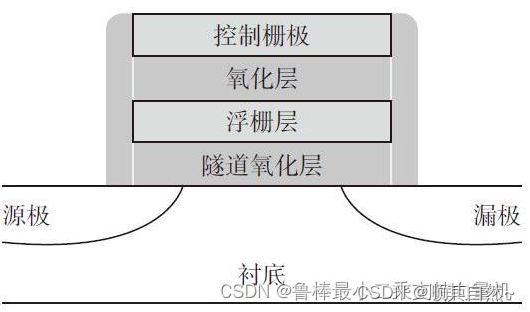

1967年,贝尔实验室的韩裔科学家姜大元和华裔科学家施敏一起发明了浮栅晶体管(Floating Gate Transistor),这是现在SSD基础——闪存的技术来源。图1-9所示,相比MOSFET多了Floating Gate,悬浮在中间,所以叫浮栅。它被高阻抗的材料包裹,和上下绝缘,能够保存电荷,而电荷通过量子隧道效应进入浮栅。

图1-9 浮栅晶体管结构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

4 闪存SSD异军突起

20世纪90年代末,终于有一些厂商开始尝试使用闪存制造SSD,进行艰难的市场探索。1997年,Altec Computer Systeme推出了一款并行SCSI闪存SSD,接着1999年BiTMICRO推出了18GB的闪存SSD,从此,闪存SSD逐渐取代RAM SSD,成为SSD市场的主流。从2003年开始,SSD的时代终于到来,SSD开始成为存储行业的一个热词,固态硬盘的概念开始为许多人所知晓。

5 2006年,SSD进入笔记本

2006年,NextCom制造的笔记本开始使用SSD。三星推出了32GB的SSD,并认为2007年SSD市场容量可达13亿美金,2010年将达到45亿美金。9月,三星推出了PRAM SSD,这另一种SSD技术,其采用了PRAM作为载体,三星希望能取代NOR闪存。

6 2007,革命之年

2007年,Mtron和Memoright公司开发了2.5寸和3.5寸的闪存SSD,读写带宽和随机IOPS性能终于达到了最快的企业级HDD水平,同时闪存SSD开始在某些领域替代原来的RAM SSD。硬盘大战的序幕从此拉开。

7 2008年,速度大战爆发

2008年,SSD厂商迅速达到了100家,就是说一年内新冒出了40家新的SSD厂商。这一年使用的闪存还是SLC。SLC虽然容量小、价格高,但是挡不住大家的热情,IOPS不断被打破。

8 2009年,SSD的容量赶上了HDD

PureSilicon公司的2.5寸SSD做到了1TB容量,由128片64Gb的MLC闪存组成。SSD终于在同样的空间内,实现了和HDD一样大的容量。

9 2010年,SSD市场开始繁荣

2010年,SSD市场达到了10亿美金。

10 2011~2012年,上市、收购,群雄并起

企业级市场也开始使用MLC。闪存阵列厂商Skyera推出了44TB的SSD,售价13.1万美金!IBM收购了老牌RAM SSD厂商TMS。

11 2013年,PCIe SSD进入消费者市场

台式机和笔记本觉得SATA已经不够用了,SATA是为HDD设计的接口,最大速度是6Gbps,只能达到最高600MB/s的带宽(扣除协议开销,实际速度可能只有560MB/s左右),同时命令队列不够深,不适合SSD使用。SSD开始在协议上引发存储技术的变革。

12 2014年,SSD软件平台重构企业级存储

SSD大放异彩需要整个生态链的支持,因为以前的软件和协议都是为慢速HDD设计的。现在它们需要适应快速的硬盘。

13 2015年,3D XPoint

Toshiba发布48层3D闪存样品,容量16GB。7月,Intel和Micron宣布开发出了新型存储器——3D XPoint。

14 2016年,NVDIMM开始供货,关键是怎么标准化

- Google经过测试认为不值得花那么多钱去买SLC,其实MLC性价比更高

- NVMdurance再次融资,号称能延长闪存寿命

- Cadence和Mellanox展示了PCIe 4.0技术,带宽达到16Gbps

- Pure Storage表示2016年第一季度全闪存阵列收入超过了机械硬盘阵列头号厂商

- Diablo的128GB DDR4Memory1开始供货

- 希捷展示60TB的3.5寸SAS SSD

- Nimbus在FMS上展示4PB 4U HA全闪存阵列

- Everspin(MRAM)启动上市IPO进程

- Rambus宣布了基于FPGA的数据加速卡项目

- SiliconMotion发布了世界上第一颗SD 5.1标准的SD卡控制器

- Violin破产保护

1.4 SSD基本工作原理

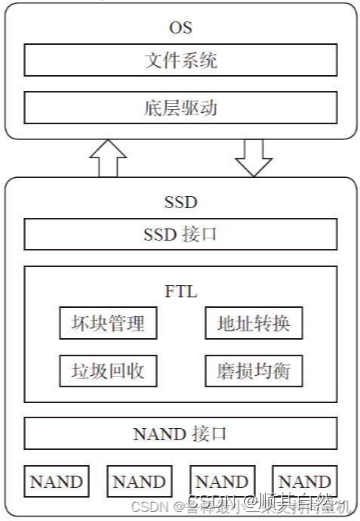

从主机PC端开始,用户从操作系统应用层面对SSD发出请求,文件系统将读写请求经驱动转化为相应的符合协议的读写和其他命令,SSD收到命令执行相应操作,然后输出结果,每个命令的输入和输出经协议标准组织标准化,这是标准的东西,和HDD无异,只不过HDD替换成SSD硬件存储数据,访问的对象变成SSD。

SSD的输入是命令(Command),输出是数据(Data)和命令状态(Command Status)。SSD前端(Front End)接收用户命令请求,经过内部计算和处理逻辑,输出用户所需要的数据或状态。从图1-13所示可以看出,SSD主要有三大功能模块组成:

1)前端接口和相关的协议模块

2)中间的FTL层(Flash Translation Layer)模块

3)后端和闪存通信模块

图1-13 SSD系统调用 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

SSD前端负责和主机直接通信,接收主机发来的命令和相关数据,命令经SSD处理后,最终交由前端返回命令状态或数据给主机。SSD通过诸如SATA、SAS和PCIe等接口与主机相连,实现对应的ATA、SCSI和NVMe等协议,如表1-5所示

表1-5 SATA/SAS/PCIe接口协议 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

SSD写操作:主机通过接口发送写命令给SSD,SSD接收到该命令后执行,并接收主机要写入的数据。数据一般会先缓存在SSD内部的RAM中,FTL会为每个逻辑数据块分配一个闪存地址,当数据凑到一定数量后,FTL便会发送写闪存请求给后端,然后后端根据写请求,把缓存中的数据写到对应的闪存空间。由于闪存不能覆盖写,闪存块需擦除才能写入。主机发来的某个数据块,它不是写在闪存固定位置,SSD可以为其分配任何可能的闪存空间写入。因此,SSD内部需要FTL这样一个东西,完成逻辑数据块到闪存物理空间的转换或者映射。

举例:假设SSD容量为128GB,逻辑数据块大小为4KB,所以该SSD一共有128GB/4KB=32M个逻辑数据块。每个逻辑块都有一个映射,即每个逻辑块在闪存空间都有一个存储位置。闪存地址大小如果用4字节表示,那么存储32M个逻辑数据块在闪存中的地址则需要32M×4B=128MB大小的映射表。

正因为SSD内部维护了一张逻辑地址到物理地址转换的映射表,当主机发来读命令时,SSD能根据需要读取的逻辑数据块查找该映射表,获取这些逻辑数据在闪存空间所在的位置,后端便能从闪存上把对应数据读到SSD内部缓存空间,然后前端负责把这些数据返回给主机。

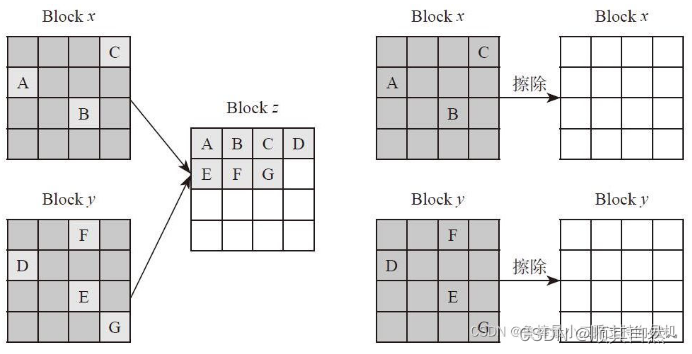

由于前端接口协议都是标准化的,后端和闪存的接口及操作也是标准化的(闪存遵循ONFI或者Toggle协议),因此,一个SSD在前端协议及闪存确定下来后,差异化就体现在FTL算法上了。FTL算法决定了性能、可靠性、功耗等SSD的核心参数。闪存不能覆盖写,因此随着用户数据的不断写入,闪存空间会产生垃圾(无效数据)。FTL需要做垃圾回收(Garbage Collection),以腾出可用闪存空间用以写用户数据

以图1-14所示为例,在Block x和Block y上有很多垃圾数据,其中Block x上的A、B、C为有效数据,Block y上的D、E、F、G为有效数据。垃圾回收就是把一个或者几个Block上的有效数据搬出来集中写到某个空闲Block上(比如Block z)。当这些Block上的有效数据都搬走后,FTL便能擦除这些Block,然后又能把这些Block拿出来供SSD写入新的数据了。

图1-14 垃圾数据回收 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

闪存都是有寿命的,每个闪存块不能一直写数据,因此,为保证最大的数据写入量,FTL必须尽量让每个闪存块均衡写入,这就是磨损平衡(Wear Leveling)。

1.5 SSD产品核心参数

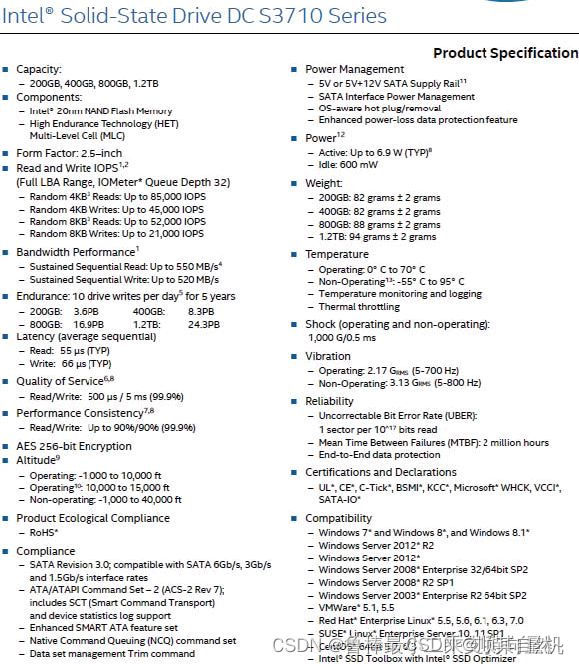

以Intel一款企业级SATA接口数据中心盘S3710SSD产品手册为例,如图1-15所示,解读SSD产品的核心参数。

图1-15 Intel DC S3700固态硬盘规格书截图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

从图1-15所示分类来看,这份文档给用户展示了SSD几大核心参数:

1)基本信息:包括容量配置(Capacity)、介质信息(Component)、外观尺寸(Form Factor)、重量(Weight)、环境温度(Temperature)、震动可靠性(Shock和Vibration)、认证(Certifications)、加密(Encryption)等信息

2)性能指标:连续读写带宽、随机读写IOPS、时延(Latency)、最大时延(Quality of Service)

3)数据可靠性和寿命:Reliability、Endurance

4)功耗:Power Management、Active Power和Idle Power

5)兼容性等:Compliance、Compatibility(与操作系统集成时参考)

1.5.1 基本信息剖析

1 SSD容量

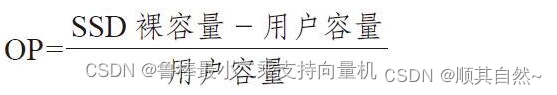

SSD容量是指提供给终端用户使用的最终容量大小,以字节(Byte)为单位。以二进制为单位的容量行业内称为裸容量,以十进制为单位的容量称为用户容量。裸容量比用户容量多出7%。这里指GB级,当进入到TB级时,数值差距更大。对于闪存本身,它是裸容量。SSD可以利用这多出来的7%空间管理和存储内部数据,比如把这部分额外的空间用作FTL映射表存储空间、垃圾回收所需的预留交换空间、闪存坏块的替代空间等。这里的7%多余空间也可以转换为OP概念(Over Provisioning),公式是

公式来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2 介质信息

当前SSD盘核心存储介质是闪存,闪存这种半导体介质有其自身物理参数,例如寿命(PE cycles,编程擦除次数)、Program(写编程)、Erase(擦除)和Read(读)时间、温度对读写擦的影响、闪存页的大小、闪存块的大小。这些都是介质的信息,介质的好坏直接影响数据存储的性能和完整性

闪存分SLC、MLC、TLC(甚至QLC),它指的是一个存储单元存储的比特数,见表1-6

表1-6 SLC、MLC和TLC参数比较 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1)SLC(Single-Level Cell)即单个存储单元存储1bit的数据。SLC速度快,寿命长(5万~10万次擦写寿命),但价格超贵(约是MLC 3倍以上的价格)。

2)MLC(Multi-Level Cell)即单个存储单元存储2bit的数据。MLC速度一般,寿命一般(约为3k~10k次擦写寿命),价格一般。

3)TLC(Trinary-Level Cell)即单个存储单元存储3bit的数据,也有闪存厂家叫8LC,速度慢,寿命短(约500~1500次擦写寿命),价格便宜。

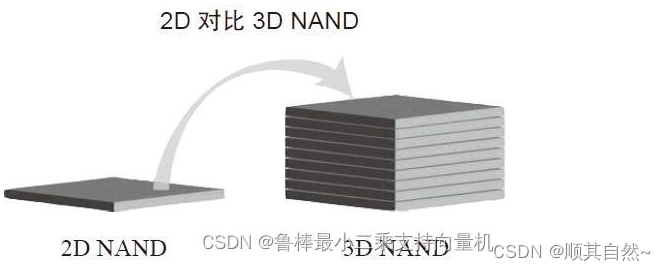

闪存发展到现在,经历了2D平面到现在的3D立体制程(Process)的大发展,目标只有一个:硅片单位面积(mm2 )能设计生产出更多的比特(bit),让每GB成本和价格更低。

2D与3D闪存结构示意图,如图1-16所示

图1-16 2D vs.3D闪存结构示意图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

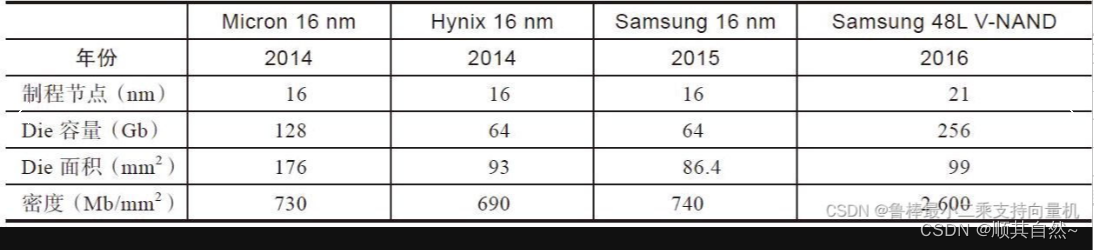

2D到3D的单位面积比特数的比较,见表1-7

表1-7 不同闪存密度对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

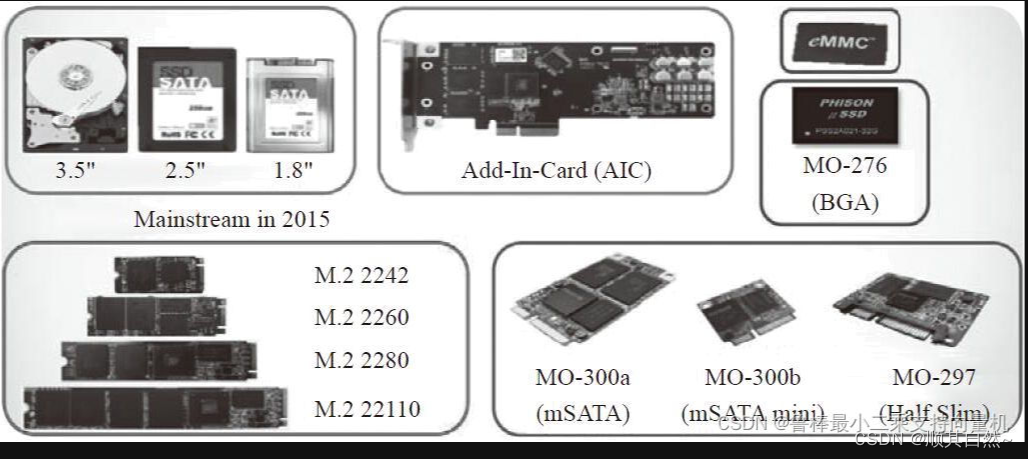

3 外观尺寸

SSD是标准件,外观尺寸需要满足一定的规定要求(长宽高和接口连接器),这又通常称为Form Factor。SSD细分为3.5寸、2.5寸、1.8寸、M.2、PCIe card、mSATA、U.2等Form Factor标准,见图1-18,每个Form Factor也都有三围大小、重量和接口引脚等明确规范

图1-18 SSD尺寸部分一览 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

4 其他

1)温度:所有工业品都有温度规范,SSD应在一定温度范围内使用。工作温度为0℃~70℃,说的是SSD在运行状态时的温度,超出这个温度范围SSD可能出现产品异常和数据异常。非工作温度为-50℃~90℃,这是SSD储存和运输期间的温度,也就是在非开机工作状态下,产品运输和仓库存储时的参考温度参考。超出-50℃~90℃,SSD可能会发生损坏

2)认证及兼容性信息:SSD硬件和软件都应通过一定认证测试来反映产品的标准测试情况,从而让客户明确是不是过了相应的测试。认证和兼容性是对应标准组织的测试集,标准组织属于第三方,独立客观,测试通过意味着可以免去客户一部分测试。

1.5.2 性能剖析

1 性能指标

硬盘性能指标一般包括IOPS(Input Output Operations Per Second,反映的是随机读写性能)、吞吐量(Throughput,单位MB/s,反映的是顺序读写性能)、Response Time/Latency(响应时间/时延,单位ms或μs)。

1)IOPS:单位IOPS,即设备每秒完成IO请求数,一般是小块数据读写命令的响应次数,比如4KB数据块尺寸。IOPS数字越大越好。

2)吞吐量:单位MB/s,即每秒读写命令完成的数据传输量,也叫带宽(Bandwidth),一般是大块数据读写命令,比如512KB数据块尺寸。吞吐量越大越好。

3)响应时间:也叫时延(Latency),即每个命令从发出到收到状态回复所需要的响应时间,时延指标有平均时延(Average Latency)和最大时延两项(Max Latency)。响应时间越小越好。

2 访问模式

性能测试设计上要考虑访问模式(Access Pattern),包括以下三部分:

1)Random/Sequential:随机(Random)和连续(Sequential)数据命令请求。何为随机和连续?指的是前后两条命令LBA地址是不是连续的,连续的地址称为Sequential,不连续的地址称为Random

2)Block Size:块大小,即单条命令传输的数据大小,性能测试从4KB~512KB不等。随机测试一般用小数据块,比如4KB;顺序测试一般用大块数据,比如512KB

3)Read/Write Ratio:读写命令数混合的比例

3 时延指标

时延有平均时延和最大时延,数值越低越好。平均时延计算公式是整个应用或者测试过程中所有命令响应时间总和除以命令的个数,反映的是SSD总体平均时延性能;最大时延取的是在测试周期内所有命令中响应时间最长的那笔,反映的是用户体验。

4 服务质量指标

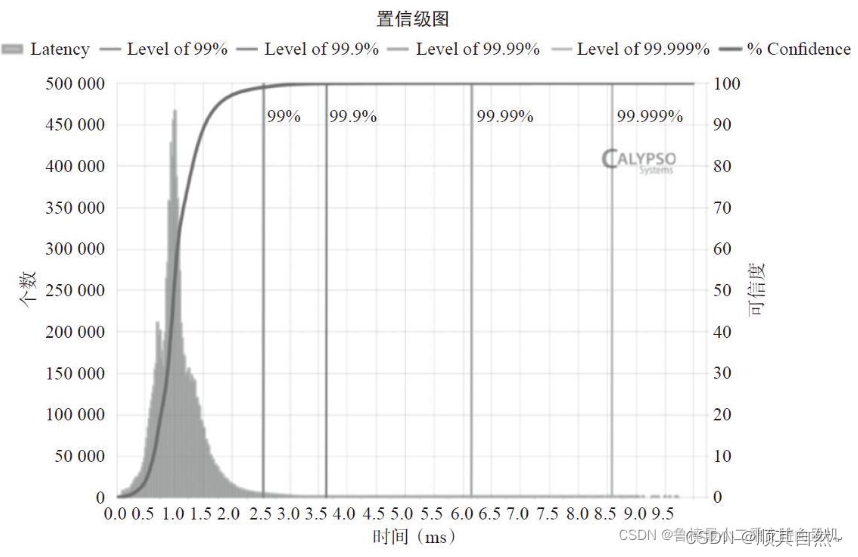

服务质量(Quality of Service,QoS)表达的是时延“置信级”(Confidence Level),如图1-20所示,在测试规定的时间内使用2个9(99%)到5个9(99.999%)的百分比的命令中最大的时延(Max Latency),也就是最慢的那条命令的响应时间。整体上看,一个SSD盘QoS时延分布整体越靠左越好,即时延越小越好

图1-20 SSD时延分布图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

5 性能数据一览

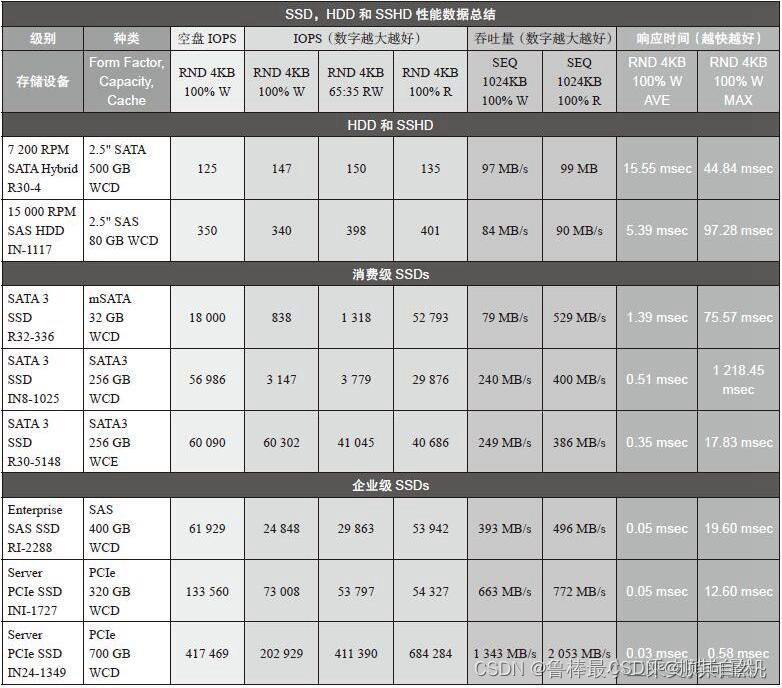

一组性能测试数据,包括SSD、HDD和SSHD(SSD和HDD混合硬盘)的性能数据,如图1-21所示:

图1-21 SSD、HDD和SSHD性能数据一览 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.5.3 寿命剖析

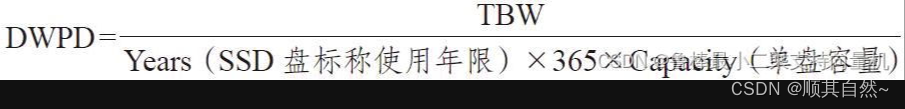

用户拿到一款SSD,除了关心其容量和性能参数外,还会关心它的寿命(Endurance)指标,也就是在SSD产品保质期内,总的寿命是多少,能写入多少字节的数据量。衡量SSD寿命主要有两个指标:

- DWPD(Drive Writes Per Day),即在SSD保质期内,用户每天可以把盘写满多少次

- TBW(Terabytes Written),在SSD的生命周期内可以写入的总的字节数

1 DWPD

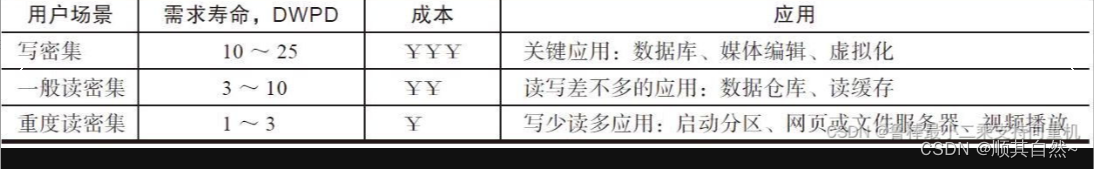

总的写入量可以换算成DWPD,一些SSD指标上更多使用DWPD作为寿命参数。从应用的角度出发,多数应用读多写少,少数应用写多读少,应用不同,对SSD的寿命要求也不同。可以将其归类为:写密集(Write Intensive)和读密集(Read Intensive)两种类型。表1-8比较好地归纳出应用场合和应用读写特点所需求的DWPD参数

表1-8 DWPD参数 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2 TBW

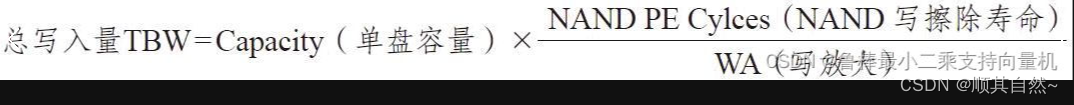

TBW就是在SSD的生命周期内可以写入的总的字节数,用来表达SSD的寿命指标,公式如下:

公式来源于《深入浅出SSD:固态存储核心技术、原理与实战》

上式中:

- NAND PE Cycles:SSD使用的闪存标称写擦除次数,如3K、5K

- Capacity:SSD单盘用户可使用容量

- WA:写入放大系数,这跟SSD FW的设计和用户的写入的数据类型(顺序写还是随机写)强相关

TBW和DWPD的计算公式:

公式来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.5.4 数据可靠性剖析

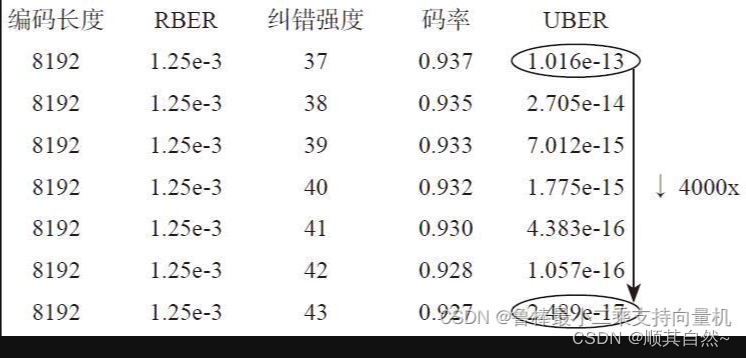

SSD有几个关键指标来衡量其可靠性:UBER、RBER和MTBF

- UBER:Uncorrectable Bit Error Rate,不可修复的错误比特率

- RBER:Raw Bit Error Rate,原始错误比特率

- MTBF:Mean Time Between Failure,平均故障间隔时间

1 数据可靠性

UBER是一种数据损坏率衡量标准,等于在应用了任意特定的错误纠正机制后依然产生的每比特读取的数据错误数量占总读取数量的比例(概率)

为什么会产生错误数据?SSD的存储介质是闪存,闪存有天然的数据比特翻转率。主要有以下几种原因导致:

- 擦写磨损(P/E Cycle)

- 读取干扰(Read Disturb)

- 编程干扰(Program Disturb)

- 数据保持(Data Retention)发生错误

虽然SSD主控和固件设计会用纠错码(ECC)的方式(可能还包括其他方式,如RAID)来修正错误数据,但错误数据在某种条件下依然有纠不回来的可能,所以需要用UBER让用户知道数据误码纠不回来的概率

闪存原始的数据比特翻转加上BCH码(一种ECC纠错算法)经ECC校验码保护后,可以计算转换到UBER。影响UBER最核心的因素是RBER。图1-24所示为从RBER、ECC编码长度(Code Length)和保护强度(Strength)换算到UBER,从中得出结论:相同的ECC编码长度,随着保护强度的增长,UBER在大幅度降低

图1-24 UBER和纠错强度的关系 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

在相同的ECC编码长度和保护强度下,RBER越低,UBER越低,并呈指数级降低,如图1-25所示

图1-25 UBER和RBER的关系 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

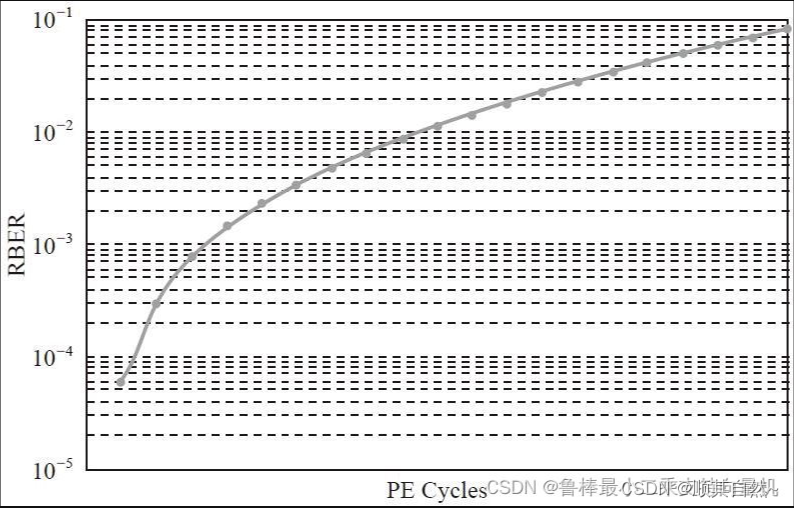

RBER反映的是闪存的质量。所有闪存出厂时都有一个RBER指标,企业级闪存和消费级闪存的RBER显然是不同的,价格当然也有所不同。RBER指标也不是固定不变的,如图1-26所示,闪存的数据错误率会随着使用寿命(PE Cycle)的增加而增加。为了挑战极限,必须准备好处理每100个bit就有1个坏bit的情况

图1-26 RBER和PE的关系 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

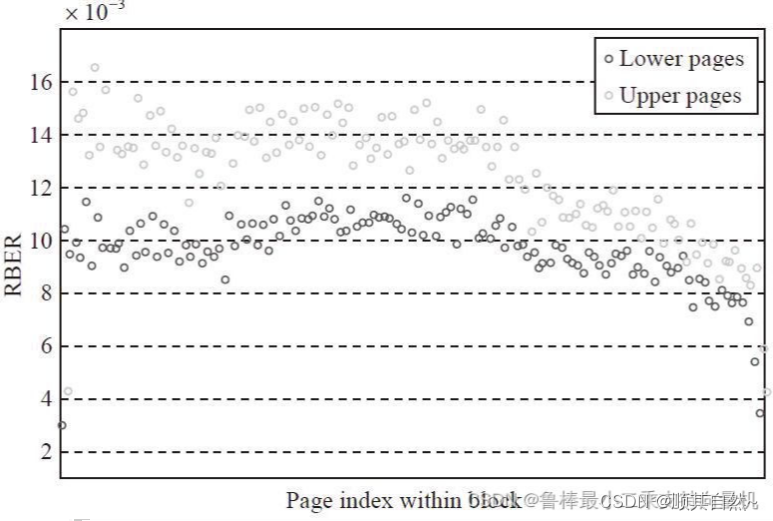

RBER还跟闪存内部结构也有关系。两个相邻闪存块的RBER有可能完全不同,图1-27是单个闪存块里面不同闪存页的RBER分布图。看得出来,Upper Page的RBER比Lower Page的RBER要高两个数量级

图1-27 Lower&Upper page RBER 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2 MTBF

工业界MTBF指标反映的是产品的无故障连续运行时间,也是产品的可靠性指标。MTBF计算有一些标准,目前最通用的权威性标准是MIL-HDBK-217、GJB/Z299B和Bellcore,分别用于军工产品和民用产品

MTBF主要考虑的是产品中每个器件的失效率。但由于器件在不同的环境、不同的使用条件下其失效率会有很大的区别,在计算可靠性指标时,必须考虑多种因素。所有这些因素几乎无法通过人工进行计算,但借助软件(如MTBFcal软件)和其庞大的参数库,能够轻松得出MTBF值

1.5.5 功耗和其他剖析

1 SSD产品功耗

SSD定义了以下几种功耗类型:

空闲(Idle)功耗:当主机无任何命令发给SSD,SSD处于空闲状态但也没有进入省电模式时,设备所消耗的功耗

Max active功耗:最大功耗是SSD处于最大工作负载下所消耗的功耗,SSD的最大工作负载条件一般是连续写,让闪存并发忙写和主控ASIC满负荷工作,这时的功耗值对应最大功耗

Standby/Sleep功耗:规范规定了SSD状态,包括:Active、Idle、Standby和Sleep,功耗值从Active到Sleep逐级递减,具体的实现由各商家自行定义。一般来讲,在Standby和Sleep状态下,设备应尽可能把不工作的硬件模块关闭,降低功耗。一般消费级SSD Standby和Sleep功耗为100~500mW

DevSleep功耗:这是SATA和PCIe新定义的一种功耗标准,目的是在Standby和Sleep基础上再降一级功耗,配合主机和操作系统完成系统在休眠状态下(如Hibernate),SSD关掉一切自身模块,处于极致低功耗模式,甚至是零功耗。一般是10mW以下

对于主机而言,它的功耗状态和SSD作为设备端是一一对应的,而功耗模式发起端是主机,SSD被动执行和切换对应功耗状态。系统Power State(SATA SSD作为OS盘):

S0:工作模式,OS可以管理SATA SSD的Power State,D0或者D3都可以

S1:是低唤醒延迟的状态,系统上下文不会丢失(CPU和Chipset),硬件负责维持所有的系统上下文

S2:与S1相似,不同的是处理器和系统Cache上下文会丢失(OS负责维护Cache和处理器上下文)。收到唤醒要求后,从处理器的reset vector开始执行

S3:睡眠模式(Sleep),CPU不运行指令,SATA SSD关闭,除了内存之外的所有上下文都会丢失。硬件会保存一部分处理器和L2cache配置上下文,从处理器的reset vector开始执行

S4:休眠模式(Hibernation),CPU不运行指令,SATA SSD关闭,DDR内容写入SSD中,所有的系统上下文都会丢失,OS负责上下文的保存与恢复

S5:Soft off state,与S4相似,但OS不会保存和恢复系统上下文。消耗很少的电能,可通过鼠标键盘等设备唤醒

进入功耗模式有一定的时延,当然退出功耗模式也需要一定的时延,通常恢复SSD到初始功耗模式所花费的时间更长,如表1-10所示

表1-10 各种功耗模式下SSD进入和退出的时间 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2 最大工作功耗与发热控制

前面已解释过最大工作功耗,单独把最大工作功耗拉出来讨论,是因为当SSD一直处于最大功耗工作负载下,器件会存在发热问题。为SSD功耗最大的是ASIC主控和闪存模块,因此二者也是发热大户,当热量积累到一定程度,器件会损坏掉,这是一定不能容忍的。当外界环境温度(Ambient Temperature)处在50℃或60℃时,不加以控制,发热的速度和损坏器件的概率也会随之增大。所以工作在最大负载下,控制SSD温度是固件设计要考虑的,就是设计降温处理算法

做法具体的原理:当SSD温度传感器侦测到温度达到阈值,如70℃,固件启动降温算法模块,限制闪存后端并发写的个数,由于SSD中发热大户是闪存芯片,故当写并发数减少后,温度自然下降。同时由于写并发下降,SSD写性能也会下降,这是性能和温度的一个折中

1.5.6 SSD系统兼容性

SSD的各项参数中,系统兼容性指标无法量化,最不直观,也最容易被忽视。但不可否认的是,实际应用场合中除了性能功耗和可靠性问题,最让人头疼的是系统兼容性问题,表现为各种场景下盘无法识别、不兼容某些型号主板、操作系统无法兼容等问题。站在用户角度,SSD盘的性能、功耗、可靠性设计得都不错,测试出来的成绩单很漂亮,但就是系统兼容性差,再好的盘放到电脑上就变砖,看上去就是漂亮的花瓶,中看不中用。所以渐渐地用户开始重视系统兼容性问题,在SSD引入前期用比较强的测试覆盖去验证和观察系统兼容性。从技术上系统兼容性问题归类为如下几类:

1 BIOS和操作系统的兼容性

SSD上电加载后,主机BIOS开始自检,主机中的BIOS作为第一层软件和SSD进行交互:第一步,和SSD发生链接,SATA和PCIe走不同的底层链路链接,协商(negotiate)到正确的速度上,自此主机端和SSD连接成功;第一步,发出识别盘的命令(如SATA Identify)来读取盘的基本信息,基本信息包括产品part number、FW版本号、产品版本号等,BIOS会验证信息的格式和数据的正确性,然后BIOS会走到第三步去读取盘其他信息,如SMART,直到BIOS找到硬盘上的主引导记录MBR,加载MBR;第四步,MBR开始读取硬盘分区表DPT,找到活动分区中的分区引导记录PBR,并且把控制权交给PBR,最后,SSD通过数据读写功能来完成最后的OS加载。完成以上所有这些步骤就标志着BIOS和OS在SSD上电加载成功。任何一步发生错误,都会导致SSD交互失败,进而导致系统启动失败,弹出Error window或蓝屏。

对SSD而言,其功能已经通过了白盒黑盒测试,但上述的加载初始化流程以及特定的BIOS和OS版本结合的相关功能测试并没有覆盖到,所以涉及这些功能有时可能会导致SSD设备加载失败。

由于现实世界中有太多的主板型号和版本号,一块兼容性良好的SSD需要在这些主机上都能正常运行。从测试角度来看,系统兼容性认证包括以下各个方面:

- OS种类(Windows、Linux)和各种版本的OS;

- 主板上CPU南北桥芯片组型号(Intel、AMD)和各个版本;

- BIOS的各个版本;

- 特殊应用程序类型和各个版本(性能BenchMark工具、Oracle数据库)

2 电信号兼容性和硬件兼容性

电信号兼容性和硬件兼容性指的是SSD工作时,主机提供的电信号处于非稳定状态,比如存在抖动、信号完整性差等情况,但依然在规范误差范围内,此时SSD通过自身的硬件设计和接口信号完整性设计依然能正常工作,数据也依然能正确收发。同理,在高低温、电磁干扰的环境下,SSD通过硬件设计要有足够的鲁棒性

3 容错处理

错误处理与硬件和软件相关。系统兼容性的容错特指在主机端发生错误的条件下,SSD盘即使不能正常和主机交互数据,至少不能变砖。当然,SSD盘若能容错并返回错误状态给主机,提供足够的日志来帮助主机软硬件开发人员调试就更好了。这里的错误包括接口总线上的数据CRC错误、丢包、数据命令格式错误、命令参数错误等

1.6 接口形态

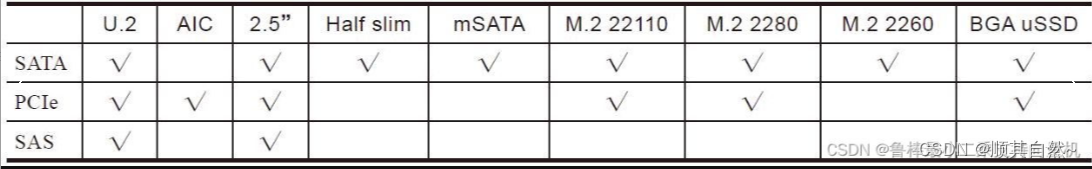

SSD接口形态和尺寸的英文是SSD Form Factor,不同应用场景下的SSD,其Form Factor尺寸也不一样,如图1-31所示。表1-11列出了当下SATA、PCIe、SAS接口和协议的SSD所使用的Form Factor

图1-31 各种类型的SSD示意图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

表1-11 SSD form Factor和接口 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.6.1 2.5寸

2.5寸是主流企业级SSD的尺寸,这类SSD包括SATA、SAS和PCIe三种不同接口和性能的企业级SSD,1U存储和服务器机架上可以放入20~30块硬盘,专为2.5寸尺寸设计。消费级SSD,尺寸主流包括2.5寸和更小尺寸的M.2,2.5寸多应用于桌面型PC,而轻薄型笔记本更多地使用M.2。

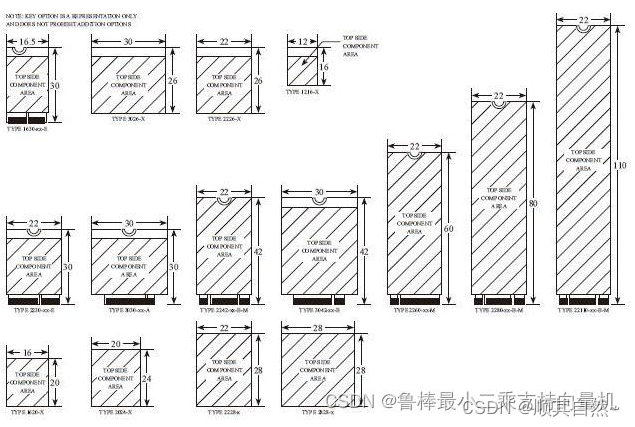

1.6.2 M.2

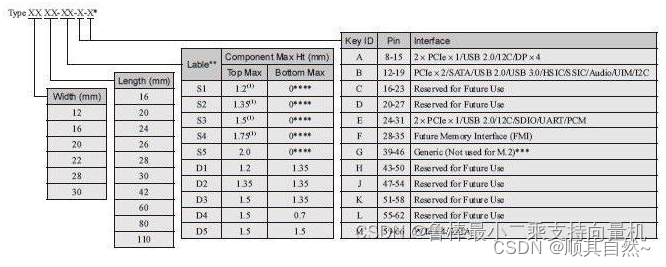

如图1-32所示,首先看看M.2Form Factor(包括M.2普通和BGA SSD)的三围标准:Type 1216、Type 1620、Type 1630、Type 2024、Type 2226、Type 2228、Type 2230、Type 2242、Type 2260、Type 2280、Type 2828、Type 3026、Type 3030、Type 3042、Type 22110,前两个数字为宽度,后两个(或三个)数字是高度

图1-32 各种不同M.2规格 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

参数定义参考图1-33,图中明确定义了宽、高、厚尺寸和接口总线形式,甚至可以支持USB/SD卡接口,同时又保留了一些总线接口

图1-33 M.2的命名规则 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.6.3 BGA SSD

早在几年前,Intel和几家公司就在讨论在消费级平板或笔记本市场推出M.2BGA SSD及其标准,如比较传统的M.22260/2280/22110SSD,它有几点技术优势:

- 节省了15%以上的平台空间;

- 增加了10%的电池寿命;

- 节省了0.5mm~1.5mm SSD本身的高度;

- 具有更好的散热性(由于是BGA封装,热可以由ball pin传导到PCB板散出)

1.6.4 SDP

SDPTM 就是SATA Disk in Package,是指将SSD主控芯片、闪存芯片在封装厂封装成一体化模块,经过开卡量产、测试后出厂。这种产品形态相当于SSD的半成品,只需要加上外壳就能成为完整的SSD产品。SDPTM 具有尺寸小、功耗低、质量轻等亮点,其尺寸大小仅为33.4×17.2×1.23mm,功耗低至1430mW,质量仅为1.9g

1.6.5 U.2

U.2俗称SFF-8639,这是新生产物,采用非AIC形式,以盘的形态存在。开发U.2的目的是统一SAS、SATA、PCIe三种接口,方便用户部署。其标准至本书完稿时还在不断更新和补充中。不可否认的是,在PCIe取代SATA甚至SAS的未来,U.2连接器和Form Factor会成为企业级SSD盘存在的主要形态,PCIe接口成为主要接口

1.7 固态存储市场

1.7.1 SSD正在取代HDD

从2000年年初SSD雏形诞生,到几大闪存原厂布局SSD产品,SSD经历了用户对闪存和数据可靠性的质疑,到实际产品的试水、铺开,一直到2015年才掀起SSD替换HDD的浪潮

1.7.2 SSD、HDD应用场合

数据按照热度的不同会采取不同的存储方式,这样可以平衡性能和成本的问题,俗称性价比。在HDD和SSD二分天下的今天,SSD主要用于存放和用户贴近的热数据,其对总容量需求较小,性能优先;HDD主要用于存放和用户较远的温(warm)数据或冷(cold)数据,其对总容量需求较大,价格优先。这是一种设计的平衡。具体来讲:

- 数据加速层:采用PCIe接口的高性能的SSD

- 热数据(频繁访问)层:采用普通SATA、SAS SSD

- 温数据层:采用高性能HDD

- 冷数据层:采用HDD

- 归档层:采用大容量价格低廉的HDD,甚至磁带

1.7.3 SSD市场情况

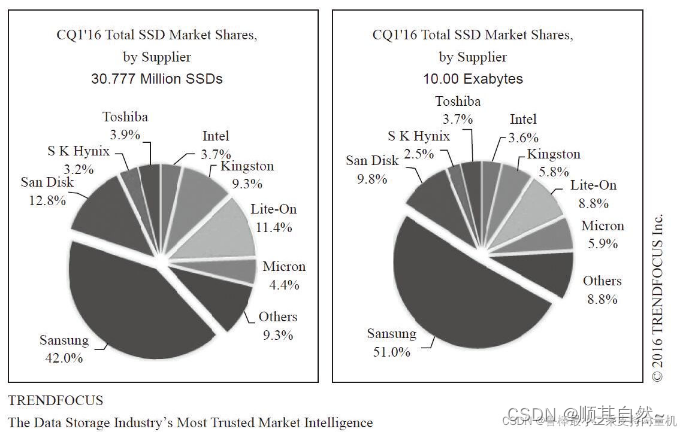

从2016年Trend Focus的SSD市场占有率调研来看,总体来说三星(Samsung)领跑整个市场,占据SSD市场的半壁江山如图1-43所示

图1-43 2016各家SSD厂商市占率 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

第2章 SSD主控和全闪存阵列

SSD主要由两大模块构成——主控和闪存介质。其实除了上述两大模块外,可选的还有缓存单元。主控是SSD的大脑,承担着指挥、运算和协调的作用,具体表现在

- 一是实现标准主机接口与主机通信

- 二是实现与闪存的通信

- 三是运行SSD内部FTL算法

可以说,一款主控芯片的好坏直接决定了SSD的性能、寿命和可靠性

2.1 SSD系统架构

SSD作为数据存储设备,其实是一种典型的(System on Chip)单机系统,有主控CPU、RAM、操作加速器、总线、数据编码译码等模块,见图2-1,操作对象为协议、数据命令、介质,操作目的是写入和读取用户数据

图2-1 SSD主控模块硬件图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图2-1所示仅是一个SSD系统架构的概略图,这款主控采用ARM CPU,主要分为前端和后端两大部分。前端(Host Interface Controller,主机接口控制器)跟主机打交道,接口可以是SATA、PCIe、SAS等。后端(Flash Controller,闪存控制器)跟闪存打交道并完成数据编解码和ECC。除此之外还有缓冲(Buffer)、DRAM。模块之间通过AXI高速和APB低速总线互联互通,完成信息和数据的通信。在此基础之上,由SSD固件开发者构筑固件(Firmware)统一完成SSD产品所需要的功能,调度各个硬件模块,完成数据从主机端到闪存端的写入和读取

2.1.1 前端

主机接口:与主机进行通信(数据交互)的标准协议接口,当前主要代表为SATA、SAS和PCIe等。表2-1所示是三者的接口速率

表2-1 SATA、SAS、PCIe接口速率 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

SATA的全称是Serial Advanced Technology Attachment(串行高级技术附件),是一种基于行业标准的串行硬件驱动器接口,如图2-2所示

图2-2 SATA接口 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

SAS(Serial Attached SCSI)即串行连接SCSI,是新一代的SCSI技术,和现在流行的Serial ATA(SATA)硬盘相同,都是采用串行技术以获得更高的传输速度,并通过缩短连接线改善内部空间等,如图2-3所示

图2-3 SAS接口 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,主要优势就是数据传输速率高,目前最高的4.0版本可达到2GB/s(单向单通道速率),如图2-4和2-5所示

图2-4 PCIe接口式插卡(AIC) 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图2-5 U.2接口 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

前端是负责主机和SSD设备通信的接口,命令和数据传输通过前端总线流向或流出SSD设备

1)从硬件模块上来看,前端有SATA/SAS/PCIe PHY层,俗称物理层,接收串行比特数据流,转化成数字信号给前端后续模块处理。这些模块处理NVMe/SATA/SAS命令,它们接收并处理一条条命令和数据信息,涉及数据搬移会使用到DMA。一般命令信息会排队放到队列中,数据会放到SRAM快速介质中。如果涉及加密和压缩功能,前端会有相应的硬件模块来做处理,若软件无法应对压缩和加密的快速需求,则会成为性能的瓶颈

2)从协议角度,以一条SATA Write FPDMA命令为例对上述内容进行说明。从主机端文件系统发出一条写命令请求,该请求到主板南桥AHCI寄存器后,AHCI寄存器执行请求,即进行写操作,忽略文件系统到AHCI路径的操作细节,从SSD前端总线上看会发出如下的写交互操作,如图图2-6

图2-6 SAT A Write FPDMA命令协议处理步骤 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

步骤1:主机在总线上发出Write FPDMA命令FIS(Frame Information Structure,帧信息结构,是SATA为了实现异步传输数据块而使用的封包)

步骤2:SSD收到命令后,判断自己内部写缓存(Write Buffer)是否有空间去接收新的数据。如果有,则发出DMA Setup FIS到主机端;否则什么也不发,主机端处于等待状态(这叫流控:数据流量控制)

步骤3:主机端收到DMA Setup FIS后,发送不大于8KB数据的Data FIS给设备

步骤4:重复步骤2和步骤3直到数据全部发送完毕

步骤5:设备(SSD)发送一个状态Status FIS给主机,表示从协议层面这条写命令完成全部操作。当然Status可以是一个good status或者一个bad/error status,表示这条Write FPDMA命令操作正常或者异常完成

SSD接收命令和数据并放到SSD内部缓冲区之后,前端固件模块还需要对命令进行解析,并分派任务给中端FTL。命令解析(Command Decoder)将命令FIS解析成固件和FTL(Flash Translation Layer)能理解的元素:

- 这是一条什么命令,命令属性是读还是写

- 这条写命令的起始LBA和数据长度

- 这条写命令的其他属性,如是否是FUA命令,和前一条命令LBA是否连续(是连续命令还是随机命令)

当命令解析完成后,放入命令队列里等待中端FTL排队去处理。由于已经有了起始LBA和数据长度两大主要信息元素,FTL可以准确地映射LBA空间到闪存的物理空间。至此,前端硬件和固件模块完成了它应该完成的任务

2.1.2 主控CPU

SSD控制器SoC模块和其他嵌入式系统SoC模块并没有什么本质的不同,一般由一颗或多颗CPU核组成,同时片上有I-RAM、D-RAM、PLL、IO、UART、高低速总线等外围电路模块。CPU负责运算、系统调度,IO完成必要的输入输出,总线连接前后端模块

通常所说的固件就运行在CPU核上,分别有代码存储区I-RAM和数据存储区D-RAM。如果是多核CPU,需要注意的是软件可以是对称多处理(SMP)和非对称多处理(AMP)。对称多处理多核共享OS和同一份执行代码,非对称多处理是多核分别执行不同代码。前者多核共享一份I-RAM和D-RAM,资源共享;后者每核对应一份I-RAM和D-RAM,每核独立运行,没有内存抢占导致代码速度执行变慢的问题。当SSD的CPU要求计算能力更高时,除增加核数和单核CPU频率外,AMP的设计方式更加适应计算和任务独立的要求,消除了代码和数据资源抢占导致执行速度过慢的问题

固件根据CPU的核数进行设计,充分发挥多核CPU的计算能力是固件设计考虑的一方面。另外,固件会考虑任务划分,会将任务分别加载到不同CPU上执行,在达到并行处理的同时让所有CPU有着合理且均衡的负载,不至于有的CPU忙死有的CPU闲死,这是固件架构设计要考虑的重要内容,目标是让SSD输出最大的读写性能

SSD的CPU外围模块包括UART、GPIO、JTAG,这些都是程序必不可少的调试端口,另外还有定时器模块Timer及其他内部模块,比如DMA、温度传感器、Power regulator模块等

2.1.3 后端

后端两大模块分别为ECC模块和闪存控制器,如图2-7

图2-7 SSD中的ECC模块和闪存控制器 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

ECC模块是数据编解码单元,由于闪存存储天生存在误码率,为了数据的正确性,在数据写入操作时应给原数据加入ECC校验保护,这是一个编码过程。读取数据时,同样需要通过解码来检错和纠错,如果错误的比特数超过ECC纠错能力,数据会以“不可纠错”的形式上传给主机。这里的ECC编码和解码的过程就是由ECC模块单元来完成的。SSD内的ECC算法主要有BCH和LDPC,其中LDPC正逐渐成为主流

闪存控制器使用符合闪存ONFI、Toggle标准的闪存命令,负责管理数据从缓存到闪存的读取和写入

从单个闪存角度看,一个Die/LUN是一个闪存命令执行的基本单元,闪存控制器和闪存连接引脚按照如下操作,如图2-8

图2-8 闪存芯片接口 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

- 外部接口:8个IO接口,5个使能信号(ALE、CLE、WE#、RE#、CE#),1个状态引脚(R/B#),1个写保护引脚(WP#)

- 命令、地址、数据都通过8个IO接口输入输出

- 写入命令、地址、数据时,都需要将WE#、CE#信号同时拉低,数据在WE#上升沿被锁存

- CLE、ALE用来区分IO引脚上传输的是数据还是地址

从闪存控制器角度看,为了性能需求需要并发多个闪存Die/LUN,通常配置有多个通道(channel)。一个通道挂多少个闪存Die/LUN,取决于SSD容量和性能需求,Die/LUN个数越多,并发的个数越多,性能越好

Die/LUN是闪存通信的最小基本管理单元,配有上述的一套总线,即8个I/O口,5个使能信号(ALE、CLE、WE#、RE#、CE#),1个状态引脚(R/B#),1个写保护引脚(WP#)

如果一个通道上挂了多个闪存Die/LUN,每个Die共用每个通道上的一套总线,闪存控制器通过选通信号CE#识别和哪个Die通信。在闪存控制器给特定地址的闪存Die发读写命令和数据前,先选通对应Die的CE#信号,然后进行读写命令和数据的发送。一个通道上可以有多个CE,SSD主控一般设计为4~8个,对于容量而言选择有一定的灵活度

2.2 SSD主控厂商

SSD主控是一个技术深度和市场广度都很大的芯片产品

2.2.1 Marvell主控

Marvell在高端SoC设计上处于领先地位,Marvell通过复杂的SoC架构、领先的纠错机制、接口技术、低功耗等多项优势建立起领先竞争对手的技术壁垒

2.2.2 三星主控

三星的主控基本上都是三星自己的SSD在用,830系列使用是MCX主控,而840及840Pro使用的则是MDX主控,850Pro/840EVO用的是MEX主控,850EVO 500GB以下的和750EVO用的是MGX主控,650用的是MFX主控

2.3 案例:硅格(SiliconGo)SG9081主控

本节以国产主控厂商硅格的SATA3.2SSD主控SG9081为例,剖析一下主控如何实现高性能。图2-14为SG9081主控的结构框图

图2-14 SG9081主控的结构框图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

1.HAM+GoCache加速随机读写的IOPS

HAM是硬件加速模块的简称,SSD主控中除了MCU以外,还有一个硬件加速模块HAM。该模块将部分算法处理的动作硬件化,一方面释放了MCU的资源,另外一个方面则加速了算法的实现,尤其是对小数据的处理。另外,主控中集成了GoCache(SiliconGo独有技术),可高效地实现映射关系的管理,从而更高效地提高对小数据的传输能力。两者的结合实现了SSD成品模组性能的提升

2.DMAC加速顺序读写

DMAC是Direct Memory Access Controller的缩写。该模块的存在使得SSD在进行连续大数据传输的时候,不用一直占据MCU的资源。当DMA请求被发起时,内部总线裁决逻辑将交由DMAC控制,接着数据高速传输动作开启。传输过程中,MCU可以去处理其他的事务,而当数据传输结束之后,DMAC又会将总线让给MCU。在这样的机制保证下,SSD进行读写操作时的效率极大地提高,从而表现出优秀的顺序读写性能

3.LDPC+RAID提高可靠性,增强闪存耐久度和数据留存能力

目前闪存正从2D转向3D架构,对闪存纠错处理的要求也越来越高,早期的BCH已经无法满足先进制程或先进工艺的闪存。SG9081主控采用LDPC实现ECC,LDPC码在相同的用户数据条件下,与BCH校验码相比能纠正更多的错误,同时也增强了闪存的使用寿命。而RAID功能的引进则给数据保护加上了一个双保险。主控中的RAID功能可以理解为给数据做了一层校验保护,必要的时候可以通过校验的内容恢复为原始数据。LDPC和RAID功能大大地提高了数据的稳定性

2.4 案例:企业级和消费级主控需求的归一化设计

SSD有企业级与消费级之分。企业级SSD产品更加注重随机性能、延迟、IO QoS的保证及稳定性;而消费级产品则更加注重顺序性能、功耗、价格等,如表2-3所示

表2-3 企业级和消费级SSD对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

是否有一款归一化的SSD控制器,能同时满足企业级和消费级需求?主要的问题在于能否在控制器硬件架构上实现成本、功耗和功能的统一

1)成本方面,企业级SSD对控制器成本较不敏感,归一化SSD控制器需要着重满足消费级SSD的成本预算。采用通用硬件架构并优化硬件资源开销来约束SSD控制器成本,通过差异化固件来满足企业级与消费级产品的不同性能需求

2)在性能方面,经过市场沉淀,NVMeU.2形态与M.2形态的SSD逐渐成为主流,两种形态的SSD产品性能需求也趋于一致。作为AIC形态的取代品,1U服务器普遍承载8块或更多U.2形态SSD,使得U.2形态SSD单盘4KB随机性能在300~400KIOPS,这已能满足大部分应用需求。反观消费级SSD市场,高端游戏平台NVMe M.2形态的SSD理论上性能已达3.5GB/s,这样的性能指标已与一些企业级SSD的顺序IO相近。一些互联网厂商已在IDC数据中心中应用M.2形态的SSD。在数据中心,上层对数据流做了大量优化,数据以顺序访问方式写入SSD,这降低了对企业级SSD随机性能的需求

3)在寿命上,企业级与消费级SSD需求差别较大。但影响SSD寿命的主要因素在于闪存的耐久能力。SSD控制器则确保加强对闪存的纠错能力。因此,企业级与消费级SSD控制器在寿命方面的设计目标是一致的

4)在容量上,企业级SSD与消费级SSD差异较大。SSD控制器需要以比较小的代价支持大容量闪存,以便同时覆盖企业级与消费级SSD的需求

5)可靠性方面,企业级SSD一般要求ECC与DIE-RAID两层数据保护能力。而随着3D闪存逐步普及,闪存厂商开始建议在消费级SSD上提供DIE-RAID能力。所以在可靠性方面,企业级与消费级SSD控制器的设计目标也趋于一致了

6)在功耗方面,消费级产品对功耗最为敏感,特别是像平板、笔记本电脑这种电池供电设备,对功耗有严格的限制。SSD控制器在设计时需要考虑复杂的低功耗需求,需要支持多种电源状态,以及快速唤醒。企业级SSD对功耗相对不敏感。然而对于整个数据中心,电力成本已占数据中心运营成本近20%。随着SSD的大规模部署,低功耗设计也成为企业级SSD控制器的追求目标

从上面几点不难看出,在企业级与消费级SSD设计指标趋于一致的趋势下,硬件规格实现统一是极有可能的。而SSD产品形态的差异化则由SSD控制器上的固件体现。忆芯科技的STAR1000芯片在设计中对此做了比较成功的尝试,如图2-15所示

图2-15 STAR1000关键技术 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2.5 案例:DERA(得瑞领新)NVMe控制器TAI和NVMe SSD产品

NVMe协议面向现代多核计算系统结构设计,充分发挥NVM介质高并发及低延迟的特性,为实现高吞吐量、低延迟的存储设备打下了良好的生态基础。DERA Storage遵循协议标准,面向企业计算市场,开发提供高性能、高可靠的NVMe SSD解决方案

控制器是NVMe SSD的核心部件,是连接主机总线和闪存单元的桥梁。本质上,一个NVMe SSD设备内部需要处理高并发的大量IO事务,每个IO事务都伴随多种硬件操作和事件处理,其中一些功能特性需要结合计算密集型的操作,比如用于数据错误检测的编解码,或者数据加密、解密,在完成这些处理的同时还要满足苛刻的功耗要求,因此不可避免地需要使用专用的硬件加速单元。综合考虑,NVMe SSD控制器一般是紧密结合NAND闪存管理软件进行高度定制化设计的ASIC(专用集成电路)。只有将数据通路、计算资源都经过合理安排调配,最终实现的NVMe SSD才能在可靠性、性能、功耗几个方面实现良好统一的目标

DERA NVMe控制器是DERA NVMe SSD产品的核心部件,TAI是DERA的第一款控制器,如图2-16。DERA TAI前端支持PCIe Gen3x8或x4接口,集成多个NAND接口通道和高强度ECC硬件编解码单元,所有数据通道均运用ECC和CRC多重硬件保护机制。在TAI控制器基础上,紧密协同设计的闪存转换层(FTL)算法负责调度管理,综合运用多种技术实现企业级的数据存储可靠性,充分发挥NAND闪存的高速存取特点,实现高可靠、低延时、高吞吐量的数据存储要求

图2-16 DERA TAI控制器 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

闪存ECC是SSD的核心功能。为了处理新结构、新工艺节点下闪存芯片的高原始误码率,以及满足高并发访问时的低延迟要求,DERA TAI控制器为每个闪存通道都配备了独立的ECC单元,纠错能力为100b/1KB,满足主流闪存器件对主控纠错能力的要求,即在复杂度、面积和功耗、解码延迟时间确定性和可控性等多个方面达到了良好的均衡。此外,DERA TAI对完整数据通道的ECC保护和CRC校验,也在不影响性能的前提下为数据可靠性提供了进一步的基础保障

DERA SSD提供完备的硬件手段持续监测供电情况,并在供电异常时触发保护策略,自动切换到后备电容或其他不间断电源供电,在整体的软件策略上予以充分配合,在发生意外掉电时最大限度保证用户数据的完整性

2.6 全闪存阵列AFA

2.6.1 整体解剖

1 结构

图2-17所示是一个标准的XtremIO全闪存阵列,含有两个X-Brick,之间用Infiniband互联。可以看出,X-Brick是核心

图2-17 XtremIO全闪存阵列结构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

一个X-Brick(阵列单元)包括:

- 1个高级UPS电源

- 2个存储控制器

- 磁盘阵列存储柜DAE,放有很多个SSD,每个SSD都用SAS连接到存储控制器

- 如果系统有多个X-Brick,那么需要2个Infiniband交换机来实现存储控制器高速互联

2 存储控制器

如图2-18所示,存储控制器其实就是个Intel服务器,配有2个电源,看起来是NUMA架构的2个独立CPU、2个Infiniband控制器、2个SAS HBA卡。Intel E5CPU,每个CPU配有256GB内存

图2-18 存储控制器机箱内部 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

如图2-19所示,其后面插有各种线缆,看着感觉乱糟糟的,如图2-19所示。设计的架构适用于集群,所以线缆有很多是冗余的

图2-19 X-Brick背面连线图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

阵列正面照,LCD显示的是UPS电源状态。图2-20所示是一个个竖着的就是SSD阵列

图2-20 Xtrem-IO全闪存阵列正面照片 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3 配置

如表2-5所示,一个X-Brick容量是10TB,可用容量7.5TB,但是考虑到数据去重和压缩大概为5∶1的比例,最终可用容量为37.5TB

表2-5 XtremIO配置表 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2.6.2 硬件架构

EMC XtremIO是EMC对全闪存阵列市场的突袭,它从底层开始完全根据闪存特性设计。如图2-23所示,1个X-Brick包含2个存储控制器,一个装了25个SSD的DAE,还有2个电池备用电源(Battery Backup Unit,BBU)。每个X-Brick包含25个400GB的SSD,原始容量10TB,使用的是高端的eMLC闪存,一般擦写寿命比普通的MLC长一个数量级。如果只买一个X-Brick,配有两个BBU,其中一个是为了冗余。如果继续增加X-Brick,那么其他的X-Brick只需要一个BBU

图2-23 X-Brick尺寸 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2.6.3 软件架构

存储行业发展到今天,硬件越来越标准化,所以已经很难靠硬件出彩了。若能够制造存储芯片,例如三星这种模式,从底层开始都自己做,则可靠巨大的出货量坐收硬件的利润

1 XIO软件几大杀器

- 去重:提升性能,同时因为写放大降低,延长了闪存的寿命,提高了可靠性

- Thin Provisioning:分区的容量可以随着使用而自动增长(直到用满阵列),这样关键时刻不会影响性能

- 镜像:先进的镜像架构保证了容量和性能不会受损

- XDP数据保护:用RAID6保护数据

- VAAI集成

2 XIO软件核心设计思想

1)一切为了随机性能:任何节点上访问任意数据块,都不会增加额外的成本,即必须公平访问所有的资源。这样的结果就是即使节点增加,性能也能够线性增长,扩展性也好

2)尽可能减少写放大:对SSD来讲写放大不仅会导致寿命缩短,还会因为闪存的擦写次数升高,导致质量下降,数据可靠性下降。XIO的设计目标就是让后台实际写入的数据尽量少,起到一种数据衰减的作用

3)不做全局垃圾回收:XIO使用的是SSD阵列,而SSD内部是有高性能企业级控制器芯片的,当前的SSD主控都非常强大,垃圾回收效率很高,所以XIO并没有再重复做一遍垃圾回收。这样做的效果是降低了写放大,毕竟后台搬移的数据量少了,同时,节省出时间和系统资源提供给其他软件功能、数据服务和VAAI等

4)按照内容存放数据:数据存放的地址用数据内容生成,跟逻辑地址无关。这样数据可以存放在任何位置,提升随机性能,同时还可以针对SSD做各种优化。数据可以平均放置在整个系统中

5)True Active/Active数据访问:LUN没有所有者一说,所有节点都可以为任何卷服务,这样就不会因为某一个节点出问题而使性能受损

6)扩展性好:性能、容量等都可以线性扩展

3 XIO软件为什么运行在Linux用户态

如图2-28所示,XIO的全闪存阵列软件架构,XIO OS和XIO的软件都运行在Linux的用户态。Linux系统分为内核态和用户态,我们的应用程序都在用户态运行,各种硬件接口等系统资源都通过内核态管理,用户态通过system call访问内核资源。XIO软件运行在用户态有几大优点:

- 避免了内核态的进程切换,速度快

- 开发简单,不需要借助各种内核接口,以及复杂的内存管理和异常处理

- 不必受到GPL的约束。Linux是开源系统,程序在内核运行必然要用到内核代码,按照GPL的规定,就得开源,在用户态自己开发的应用就不受此限制

图2-28 XIO软件架构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

在每个CPU上运行着一个XIOS程序:X-ENV,如果敲一下“top”命令,就会发现这个程序掌控所有的CPU和内存资源

- 第一个作用就是为了XIO能100%使用硬件资源

- 第二个作用是不给其他进程影响XIO性能的机会,保证性能的稳定

- 第三个作用是提供了一种可能性:未来可以简单修改就移植到UNIX或者Windows平台,或者从X86CPU移植到ARM、PowerPC等CPU架构,因为这都是上层程序,不涉及底层接口

XIO是完全脱离了硬件的软件,而且,XIO的硬件基本没有自己特殊的组件,不包含FPGA,没有自己开发的芯片、SSD卡、固件等,用的都是标准件。这样做的好处是可以使用最新、最强大的X86硬件,还有最新的互联技术,比如比Infiniband更快的技术

2.6.4 工作流程

1 6大模块

XIO软件分为6个模块,以实现复杂的功能,其中包括三个数据模块R、C、D,三个控制模块P、M、L

- P(Platform,平台模块):监控系统硬件,每个节点有个P模块在运行

- M(Management,管理模块):实现各种系统配置。通过和XMS管理服务器通信来执行任务,比如创建卷、LUN的掩码等从命令行或图形界面发过来的指令。有一个节点运行M模块,其他节点运行另一个备用M模块

- L(Cluster,集群模块):管理集群成员,每个节点运行一个L模块

- R(Routing,路由模块):把发过来的SCSI命令翻译成XIO内部的命令,负责来自两个FC和两个iSCSI接口的命令,把所有读写数据拆成4KB大小,计算每个4KB数据的Hash值,用的是SHA-1算法,每个节点运行一个R模块

- C(Control,控制模块):包含了一个映射表:A2H(数据块逻辑地址——Hash值),具备镜像、去重、自动扩容等高级数据服务

- D(Data,数据模块):包含了另一个映射表:H2P(Hash值——SSD物理存放地址)。可见,数据的存放地址跟逻辑地址无关,只跟数据有关,因为hash值是通过数据算出来的,负责对SSD的读写,负责RAID数据保护技术——XDP(XtremIO Data Protection)

2 读流程

读流程如下:

- 1)主机把读命令通过FC或iSCSI接口发送给R模块,命令包含数据块逻辑地址和大小

- 2)R模块把命令拆成4KB大小的数据块,转发给C模块

- 3)C模块查A2H表,得到数据块的Hash值,转发给D模块

- 4)D模块查H2P表,得到数据块在SSD中的物理地址,读出来

3 不重复的写流程

不重复的写流程如下,见图2-29:

- 1)主机把写命令通过FC或iSCSI接口发送给R模块,命令包含数据块逻辑地址和大小

- 2)R模块把命令拆成4KB大小的数据块,计算出Hash值,转发给C模块

- 3)C模块发现Hash值没有重复,所以插入自己的表,转发给D模块

- 4)D模块给数据块分配SSD中的物理地址,写下去

图2-29 不重复的写流程 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

4 可去重的写流程

可去重的写流程如下,见图2-30:

- 1)主机把写命令通过FC或iSCSI接口发送给R模块,命令包含数据块逻辑地址和大小

- 2)R模块把命令拆成4KB大小的数据块,计算出Hash值,转发给C模块

- 3)C模块查A2H表(估计还有个H2A表,或者是个树、Hash数组之类),发现有重复,转发给D模块

- 4)D模块知道数据块有重复,就不写了,只是把数据块的引用数加1

图2-30 可去重的写流程 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

5 ESXi和VAAI

ESXi内嵌在操作系统中,所以ESXi可以看成是虚拟机平台,上面运行着很多虚拟机

VAAI(vStorage APIs for Array Integration)是虚拟化领域的标准语言之一,其实就是ESXi等发送命令的协议

6 复制流程

图2-31所示是复制前的数据状态,复制流程见图2-32,如下:

- 1)ESXi上的虚拟主机用VAAI语言发了一个虚拟机(VM)复制的命令

- 2)R模块通过iSCSI或FC收到了命令,并选择一个C模块执行复制

- 3)C模块解析出命令内容,把原来VM的地址范围0~6复制到新的地址7~D,并把结果发送给D模块

- 4)D模块查询Hash表,发现数据是重复的,所以没写数据,只把引用数增加1

图2-31 复制前的数据状态 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图2-32 复制流程 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

7 回顾R、C、D模块

R和上层打交道,C是中间层,D和底层SSD打交道,1个X-Brick的控制服务器有2个CPU,每个CPU运行一个XIOS软件。如图2-33所示,R、C模块运行在一个CPU上,D则运行在另一个CPU上

图2-33 X-Brick内部互联图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

因为Intel Sandy Bridge CPU集成了PCIe控制器(Sandy Bridge企业版CPU集成了PCIe 3.0接口,不需要通过南桥转接)。所以,在多CPU的架构中,让设备直连CPU的PCIe接口,性能就会很高,而R、C、D的分布也是按照这个需求来设计的。例如SAS转接卡插到了CPU 2的PCIe插槽上,所以D模块就要运行在CPU 2上,这样性能才能达到最优。从这里,我们又可以看出XIO的架构上的优点,就是软件完全可以按照标准化硬件来配置,通过布局达到最优的性能。如果CPU的分布变化了,也会根据新的架构简单调整软件分布来提升性能

8 模块间通信:扩展性极佳

模块间如何通信?其实并不要求模块必须在同一个CPU上,就像图2-33所示一样,R和C并不一定要在一个CPU上才行。所有模块之间的通信通过Infiniband实现,数据通路使用RDMA,控制通路通过RPC实现。XIO的IO总共延时是600~700μs,其中Infiniband只占了7~16μs。使用Infiniband来互联的优点是为了扩展性,X-Brick即使增加,延迟也不会增加,因为通信路径没变化。任意两个模块之间还是通过Infiniband通信,如果系统里面有很多R、C、D模块,当一个4KB数据块发到一个前端R模块上,它会计算Hash值,Hash会随机落在任意一个C上,没有谁特殊。这样一切都是线性的,X-Brick的增减会线性地导致性能增减

2.7 带计算功能的固态硬盘

支撑巨大数据网络的根基是IT基础设施,主要包括网络、计算和存储三大部分。如图2-34所示,IT基础架构的功能就跟加工贸易差不多,网络是数据的搬运工,计算是数据的加工商,存储就是数据的窝。自从有了固态硬盘之后,存储就不是事儿了,最新的PCIe 3.0x8SSD,读写带宽能达到4GB/s以上!一方面存储进步快,而另一方面CPU又受摩尔定律失效限制,工艺进展缓慢,所以,计算成了瓶颈,尤其是在图像和视频处理、深度学习等方面。海量数据能够从PCIe SSD高速读写,但就是CPU处理不过来

图2-34 IT基础架构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

带FPGA的SSD——CFS(Computing Flash System,计算闪存系统)。它采用PCIe 3.0x8高速接口,性能可达5GB/s。SSD提供高速数据存储,FPGA能提供计算加速,这样数据从SSD出来就由FPGA顺带算好,释放了CPU。一切回归原位,CPU做控制,FPGA做计算,SSD做存储

它的优势主要体现在海量数据高速存储和人工智能计算方面。想一想就会有很多场景,比如无人驾驶汽车,目前一般的无人驾驶汽车配备了毫米波雷达、激光雷达、高速摄像头等各类传感器。每秒会产生1GB数据,要分析这么多数据需要强大的计算能力。很多无人驾驶汽车还在使用GPU进行计算。目前市场上在卖的一个CPU+GPU计算盒,功耗能达到5000W,对于汽车来说,这个小火罐的散热会带来很大的安全风险,同时也很耗电。但是,如果换用了FPGA方案,功耗就可以降下来,根据无人驾驶的应用场景对算法进行优化之后,计算性能也能满足需求。例如,奥迪公司的无人驾驶汽车就采用了FPGA计算平台。这些传感器产生的数据目前都是丢掉,非常可惜,未来商用之后,不管是政府还是厂商都有存储宝贵的行驶数据并备份到云端的需求。这些数据对于完善无人驾驶、分析车祸现场都非常有用。要保存这些数据,只有PCIe SSD才能达到1GB/s以上的写速度。所以,FPGA SSD一方面能够快速存储行驶数据,一方面又可以提供FPGA进行数据分析,完美满足无人驾驶的计算与存储需求

自从人工智能开始新一轮的热潮之后,很多公司都开始用FPGA做人工智能计算,用了CFS,就可以直接用FPGA里的人工智能硬件算法对SSD内部的海量数据进行高速分析,最后把分析结果发送给主机

第3章 SSD存储介质:闪存

3.1 闪存物理结构

3.1.1 闪存器件原理

1978年诞生的世界上第一块固态硬盘就是基于DRAM的。但由于保存在DRAM中的数据有掉电易失性,当然还有成本因素,所以现在的固态硬盘一般都不采用DRAM,而是使用闪存作为存储介质,并且是NAND闪存

固态硬盘的工作原理很多也都是基于闪存特性的。比如,闪存在写之前必须先擦除,不能覆盖写,于是固态硬盘才需要垃圾回收(Garbage Collection,或者叫Recycle);闪存每个块(Block)擦写次数达到一定值后,这个块要么变成坏块,要么存储在上面的数据不可靠,所以固态硬盘固件必须做磨损平衡,让数据平均写在所有块上,而不是盯着几个块拼命写。还有很多类似的例子,固态硬盘内部很多算法都是在为闪存服务的。所以,欲攻固态硬盘,闪存首当其冲

闪存是一种非易失性存储器,也就是说,掉电了数据也不会丢失。闪存基本存储单元(Cell)是一种类NMOS的双层浮栅(Floating Gate)MOS管,如图3-1所示

图3-1 浮栅晶体管结构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

在源极(Source)和漏极(Drain)之间电流单向传导的半导体上形成存储电子的浮栅,浮栅上下被绝缘层包围,存储在里面的电子不会因为掉电而消失,所以闪存是非易失性存储器

写操作是在控制极加正电压,使电子通过绝缘层进入浮栅极。擦除操作正好相反,是在衬底加正电压,把电子从浮栅极中吸出来,如图3-2所示

图3-2 左:写原理;右:擦除原理 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.1.2 SLC、MLC和TLC

一个存储单元存储1bit数据的闪存,叫它为SLC(Single Level Cell),存储2bit数据的闪存为MLC(Multiple Level Cell),存储3bit数据的闪存为TLC(Triple Level Cell),如表3-1所示。现在已经有厂商在研发QLC,即一个存储单元存储4bit数据

表3-1 SLC、MLC、TLC原理 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

对SLC来说,一个存储单元存储两种状态,浮栅极里面的电子多于某个参考值的时候,把它采样为0,否则就判为1

图3-3是闪存芯片里面存储单元的阈值电压分布函数,横轴是阈值电压,纵轴是存储单元数量。其实在0或1的时候,并非所有的存储单元都是同样的阈值电压,而是以这个电压为中心的一个分布。读的时候采样电压值落在1范围里面,就认为是1;落在0范围里面,就认为是0

图3-3 SLC电压分布 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

擦除之后,闪存读出来的值为1,充过电之后,就是0。所以,如果需要写1,就什么都不用干;写0,就需要充电到0

对MLC来说,如果一个存储单元存储4个状态,那么它只能存储2bit的数据,如图3-4所示。通俗来说就是把浮栅极里面的电子个数进行一个划分,比如低于10个电子判为0;11~20个电子判为1;21~30个电子判为2;多于30个电子判为3

图3-4 MLC电压分布 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

依此类推,TLC若是一个存储单元有8个状态,那么它可以存储3bit的数据,它在MLC的基础上对浮栅极里面的电子数又进一步进行了划分,如图3-5所示

图3-5 TLC电压分布 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

同样面积的一个存储单元,SLC、MLC和TLC分别可以存储1bit、2bit、3bit的数据,所以在同样面积的DIE上,闪存容量依次变大

但同时,一个存储单元电子划分得越多,那么在写入的时候,控制进入浮栅极的电子个数就要越精细,所以写耗费的时间就越长;同样的,读的时候,需要尝试用不同的参考电压去读取,一定程度上加长了读取时间。所以会看到在性能上,TLC不如MLC,MLC不如SLC

如表3-2所示是SLC、MLC和TLC在性能和寿命(Endurance)上的一个直观对比

表3-2 SLC、MLC、TLC参数比较 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.1.3 闪存芯片架构

闪存芯片就是由成千上万这样的存储单元按照一定的组织结构组成的。图3-6所示是一个闪存块(Block)的组织架构。一个Wordline对应着一个或若干个Page,具体是多少取决于是SLC、MLC或者TLC。对SLC来说,一个Wordline对应一个Page;MLC则对应2个Page,这两个Page是一对(Lower Page和Upper Page);TLC对应3个Page(Lower Page、Upper Page和Extra Page,不同闪存厂家叫法不一样)。一个Page有多大,那么Wordline上面就有多少个存储单元,就有多少个Bitline。一个Block当中的所有这些存储单元都是共用一个衬底的

图3-6 闪存Block组织架构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

一个闪存内部的存储组织结构如图3-7所示:

- 一个闪存芯片有若干个DIE(或者叫LUN)

- 每个DIE有若干个Plane

每个Plane有若干个Block- 每个Block有若干个Page

每个Page对应着一个Wordline- Wordline由成千上万个存储单元构成

图3-7 闪存内部组织架构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

DIE/LUN是接收和执行闪存命令的基本单元。如图3-7所示,LUN0和LUN1可以同时接收和执行不同的命令(但还是有一定限制的,不同厂家的闪存限制不同)。但在一个LUN当中,一次只能独立执行一个命令,不能对其中某个Page写的同时,又对其他Page进行读访问

一个LUN又分为若干个Plane,常见的是1个或者2个Plane,现在也有4个Plane的闪存了。每个Plane都有自己独立的Cache Register和Page Register,其大小等于一个Page的大小。固态硬盘主控在写某个Page的时候,先把数据从主控传输到该Page所对应Plane的Cache Register当中,然后再把整个Cache Register当中的数据写到闪存阵列;读的时候则相反,先把这个Page的数据从闪存介质读取到Cache Register,然后再按需传给主控。按需就是我们读取数据的时候,没有必要把整个Page的数据都传给主控,而是按需选择数据传输。但要记住,无论是从闪存介质读数据到Cache Register,还是把Cache Register的数据写入闪存介质,都以Page为单位,如图3-8所示

图3-8 Page缓存的用法 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

为什么需要Cache Register和Page Register两个缓存?主要目的是优化闪存的访问速度。闪存支持Cache读、写操作,如图3-8所示。Cache读支持在传输前一个Page数据给主控的时候(Cache Register→主控),可以从闪存介质读取下一个主控需要读的Page的数据到Page Register(闪存介质→Page Register),这样数据在闪存总线传输的时间就可以隐藏在读闪存介质的时间里(或者相反,取决于哪个时间更长);Cache Program也是如此,它支持闪存写前一个Page数据的同时(Page Register→闪存介质),传输下一个要写的数据到Cache Register(主控→Cache Register),这样数据在闪存总线传输可以隐藏在前一个Page的写时间里

当然,有两个Register的闪存也支持正常的读写模式,这时候,用户可以把Cache Register和Page Register看成是一个缓存

我们通常所说的闪存读写时间,并不包含数据从闪存到主控之间的数据传输时间,也不包括数据在Cache Register和Page Register之间的传输时间

- 闪存写入时间:是指一个Page的数据从Page Register当中写入闪存介质的时间

- 闪存读取时间:是指一个Page的数据从闪存介质读取到Page Register的时间

闪存一般都支持Multi-Plane(或者Dual-Plane)操作。那么什么是Multi-Plane操作呢?

- 对写来说,主控先把数据写入第一个Plane的Cache Register当中,数据保持在那里,并不立即写入闪存介质,等主控把同一个LUN上的另外一个或者几个Plane上的数据传输到相应的Cache Register当中,再统一写入闪存介质。假设写入一个Page的时间为1.5ms,传输一个Page的时间为50μs:如果按原始的Single Plane操作,写两个Page需要至少(1.5ms+50μs)×2;但如果按照Dual-Plane操作,由于隐藏了一个Page的写入时间,写入两个Page只要1.5ms+50×2μs,缩减了几乎一半的时间,写入速度几乎翻番

- 对读来说,使用Dual-Plane操作,两个不同Plane上的Page数据会在一个闪存读取时间加载到各自的Cache Register当中,这样用一个读取时间读取到两个Page的数据,读取速度加快。假设读取时间和数据传输时间相当,都是50μs,Single Plane读取传输两个Page需要50μs×4=200μs,Dual-Plane则需要50μs×2+50μs=150μs,时间为前者的75%,读取速度也有很大的提升

闪存的擦除是以Block为单位的。因为在组织结构上,一个Block当中的所有存储单元是共用一个衬底的(Substrate)。当你对某衬底施加强电压,那么上面所有浮栅极的电子都会被吸出来。每个闪存Block都有擦写次数的限制,这个最大擦写次数按SLC、MLC、TLC依次递减:SLC的擦写次数可达10万次,MLC一般为几千到几万次,TLC降到几百到几千次。随着闪存工艺的不断进步(现在已进入1Xnm时代),闪存容量不断加大,但性能与可靠性却在变差。要克服闪存的这些不利因素,固态硬盘固件算法需要面对更多、更大的挑战

3.1.4 读、写、擦原理

1 擦除

如图3-9所示,擦除前,浮栅上有可能有电子,Pwell加20V电压,经过足够时间后,由于量子隧道效应,电子从浮栅到沟道里面,完成一个Block的擦除,阈值电压都变成了-VT ,状态为“1”。一个LUN上的MOS管共用一个Pwell,但是其他不用擦除的Block的栅极电压是悬空,不会有隧道效应

图3-9 擦除操作电压示例 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2 写

如图3-10所示,擦除后所有的单元阈值电压为-VT ,写电压如下:要写的单元Wordline为高电压,Bitline=0V;由于量子隧道效应,电子从沟道到浮栅,成为“0”。不写的单元Bitline为2V,在沟道里的效应阻碍了量子隧道效应发生

图3-10 写入操作电压示例 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3 读

不读的Wordline=5V,管子保持导通;要读的单元Wordline=0V,-VT 的管子导通,Bitline端的传感器能够检测到,所以读到“1”,而经过写的+VT的管子不导通,传感器读为“0”

图3-11 读操作电压示例 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.1.5 三维闪存

因为集成密度高、单位比特成本低和可靠性高等众多优点,闪存占据了手机、平板、固态硬盘等绝大部分的非易失性存储市场。可是因为技术上的限制,这些优势越来越难以维持下去

即使2次曝光技术(Double Patterning Technology)和4次曝光技术(Quadruple Patterning Technology)的引入提高了制造工艺,但随着一代又一代半导体制造技术的演进,二维平面单元尺寸逐渐减小,单元间的相互干扰却在逐渐增加。基于二维平面单元结构的尺寸缩小已经无法进一步降低比特成本了,即达到了技术上的瓶颈

图3-12为过去十年的单元尺寸与单元相互干扰的变化趋势图。从上半部分可以看出,二维闪存单元尺寸不断下降,对应到下半部分就是单元间的相互干扰不断增加,但到了三维闪存后,尺寸居然又再次变大了,所以,单元间相互干扰大幅度减小

图3-12 过去十年的单元尺寸(左)与单元相互干扰(右)的变化趋势 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

为了克服二维平面单元结构的技术瓶颈,自2006年以来,各种三维闪存结构陆续被提出来。其中一种叫作TCAT,已经于2013年开始了规模化量产。三维闪存结构并不是利用传统的缩小单元的方法,而是以提高堆叠栅极结构(WL)的数目来提高芯片的集成密度

图3-14是《Inside NAND Flash Memories》一书提供的某一类三维闪存的结构示意图,在这种三维闪存中,沟道是竖起来的,一层一层盖楼的是连接到栅极的Wordline

图3-14 三维闪存立体图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

与二维平面闪存相比,TCAT更加稳定、可靠而且性能水平更加优越。如图3-16所示,

- 单元间相互干扰降低了84%

- 擦写寿命却提高了10倍以上

- 编程时间(tPROG)也减少了一半

- 阈值电压Vth 随着擦写增多带来的偏移也减小了67%

图3-16 二维闪存和TCAT三维闪存特性对比 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

自从24层堆叠的三维闪存可大规模生产以来,32层、48层及64层堆叠的三维闪存也接连投产。如图3-17所示,三维闪存的存储密度在每一代几乎都实现了翻倍

图3-17 三维闪存存储密度增长图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

不过三维闪存也面临下面两个挑战:

- 1)堆叠栅极层数目增加带来的问题。 正如前面所说,三维闪存通过增加堆叠栅极层的数目来提高比特密度,而且每一代堆叠栅极层数目都会增加30%~50%,这会带来许多困难,比如串电流的减小,高层与低层单元特征的差异性增大

- 2)单元模具厚度减小带来的问题。 跟二维闪存类似,随着工艺一代一代迭代,最小尺寸也在不断减小,所以单元模具厚度不断减小,单元间的干扰也得到了增强

如图3-18所示,随着堆叠栅极层数目的增加,每个Block的Page数目不断增加。在读的过程中,对一个Block来说,累积的读取数目增加,导致读干扰会变严重。为了降低读干扰,需要降低读参考电压Vread ,这样就会导致串电流减小,使得提供给传感运放的信号更微弱

图3-18 层数越多,串电流变小,读次数增加 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

如图3-19所示,高层与低层之间的单元会存在差异。通道孔的尺寸大小和栅极厚度也存在差异,这些结构上的差异会带来编程/擦除速度的差异、单元间干扰的差异以及数据保存的差异等

图3-19 高层和底层单元差异 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

底层单元的通道孔小,所以耦合率更高,擦写速度更快。但是,底层单元的栅极更薄,所以数据保存期更短

3.1.6 Charge Trap型闪存

闪存的一种技术——Charge Trap,闪存不只有Floating Gate,还有Charge Trap。中文可以翻译成电阱,CT像个陷阱一样,把电荷困在里面存起来,如图3-20所示

图3-20 浮栅晶体管与CT晶体管对比 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

CT与浮栅最大的不同是存储电荷的元素不同,后者是用导体存储电荷,而前者是用高电荷捕捉(Trap)密度的绝缘材料(一般为氮化硅,SI3N4)来存储电荷。CT的绝缘材料上面就像布了很多陷阱,电子一旦陷入其中,就难以逃脱,而浮栅是导体材料,电子可以在里面自由移动。有人是这样来形容两者区别的:浮栅就像水,电子可在里面自由移动;而CT就像是奶酪,电子在里面移动是非常困难的,如图3-21所示

图3-21 浮栅像水,CT就像奶酪 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

为什么要强调电子不容易移动?

要知道,浮栅晶体管对浮栅极下面的绝缘层很敏感,该氧化物厚度变薄(制程不断减小导致的)或者老化(Degradation,擦写次数多了),浮栅极里面存储的电子进出变得容易。浮栅极里面的电子可以自由移动,因此对氧化层变得敏感。如果里面的电子本来就深陷其中,行动困难,即使绝缘层老化,电子还是不容易出来。因此,相对浮栅晶体管来说,CT的一个优势就是:对隧道氧化层不敏感,当厚度变薄或者擦除导致老化时,CT表示压力不大

浮栅晶体管的浮栅极材料是导体,任何两个彼此绝缘且相隔很近的导体间都会构成一个电容器。因此,任何两个存储单元的浮栅极都构成一个电容器,一个浮栅极里面电荷的变化都会引起别的存储单元浮栅极电荷的变化

一个浮栅极与其附近的浮栅极之间,都存在耦合电容,如图3-22所示,这个电容大小与彼此之间距离成反比:距离越短,电容越大,彼此影响越大。随着闪存制程减小,存储单元之间影响越来越大。因此,存储单元间距也是影响制程继续往前的一个因素。CT对存储单元间距表示压力不大,因为存储电荷的是绝缘体,而非导体

图3-22 浮栅晶体管之间耦合电容 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

与浮栅晶体管相比,CT擦写电压可以更小。为什么?

CT和浮栅晶体管对比图如图3-23所示,虽然这只是个示意图,但CT实际上确实比浮栅晶体管更矮:控制极到衬底之间的距离短。因此,要产生相同的隧道电场,加在控制极的电压可以更小(E=U/d)。更小的写电压,使得隧道氧化层压力更小,因此绝缘氧化层损耗也慢。当然,还会更省电

图3-23 CT和浮栅晶体管对比 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

CT相比浮栅晶体管有很多优势:

- 对隧道氧化层要求不是那么苛刻

- 更小的存储单元间距

- 隧道氧化层磨损更慢

- 更节能

- 工艺实现容易

- 可以在更小的尺寸上实现

- 但是,CT也不能完胜。在Read Disturb和Data Retention方面,CT闪存就不如浮栅极闪存

CT技术现在主要是应用在3D闪存上。如今除了美光使用浮栅极技术外,其他主流闪存商家都是用CT技术来制造3D闪存

3.1.7 3D XPoint

闪存用在固态硬盘上,使用SATA接口,要想更快可用SAS接口,甚至PCIe接口。其实最快的还是DRAM,可以支持字节级别的访问,但是DRAM上的数据如果不通电,马上就丢了。所以现代计算机同时使用DRAM和闪存存储数据

图3-24 新型存储器容量增长 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图3-24所示是各种新型存储器的容量成长之路,目前比较成熟的是相变存储器PCM——PRAM

- 忆阻器:ReRAM

- 铁电存储器:FeRAM

- 磁阻RAM:MRAM

- 相变存储器:PRAM,PCM

- 导电桥接RAM:cbRAM,又称可编程金属元存储器PMC

- SONOS RAM:Silicon-Oxide-Nitride-Oxide-Silicon

- 导电金属氧化物存储器:CMOx

所谓的相变存储器,就是在原子级别发生了相变,利用这个来存储数据。就像是玻璃经过相变成了晶体。这还是很好理解的,想想我们最常见的水,液体的时候形状不定,但是温度降低后,就发生相变,成为了固体——雪,雪就是晶体,有着稳定的晶体结构。如图3-25所示,左边是玻璃态,右边是晶体态,明显,晶体态更整齐

图3-25 相变晶体原理 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

物理原理讲完了,下面开始讲电气原理。不像DRAM里面有晶体管,PCM其实是通过一种微小的电阻作用使得玻璃融化,相变为晶体。技术日新月异,现在人类已经能高效地控制这种物理作用了,曾经写需要几微秒,读需要几纳秒,现在PCM已经能到皮秒的量级了,也就是纳秒的1000分之一,即10-12 秒

表3-3 几种存储器特性对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

来看看PCM和常见存储器的对比。表3-3中PCM的数据还在优化,最新的器件读写速度比表格里面快多了,里面的速度不是总线数据传输速度,而是存储介质的读写速度。这个表格的数据比较旧,主要还是对存储器在功耗、寿命、功能等方面进行比较。可以看出,PCM的特点:

- 掉电数据不丢失

- 可以按照字节访问

- 软件简单

- 写之前不需要擦除操作

- 功耗低,和闪存差不多

- 读写速度快

- 寿命远长于闪存

图3-27所示是一个PCM存储单元,读的时候只要测量GST上面金属节点的电压就知道了,晶体态时电阻低、电压低,无定形态时电阻高、电压高。其实测电阻就是测电压,假如底部接地,那么低阻时顶点电压低(和底部导通),可以表示“0”;高阻时隔断,顶点电压高,可以表示“1”

图3-27 PCM存储单元 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图3-27所示中,柱子就是加热器,通过电流之后加热GST,导致它发生相变,不过在不同的温度下,经过一定时间,相变的结果不一样。如图3-28所示,高温Tm下短脉冲加热从晶体态变成无定形态,较高温Tx长脉冲加热时从无定形态变成晶体态。图3-29所示是读写的温度时间控制波形

图3-28 不同温度脉冲对相变的影响 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图3-29 读写操作通过温度时间控制完成功能 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

闪存里面有Bitline和WordLine,通过这两个组成的矩阵来管理上亿个存储单元。图3-30所示是PCM的Bitline和WordLine结构,通过两条线可以精确控制每一个单元。写的时候控制电流的大小来加热完成相变;读的时候通过测量Bitline的电压值就能知道是低阻还是高阻,从而获得0、1值

图3-30 PCM组织结构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.2 闪存实战指南

3.2.1 异步时序

闪存接口有同步异步之分,一般来说,异步传输速率慢,同步传输速率快

- 异步接口没有时钟,每个数据读由一次RE_n信号触发,每个数据写由一次WE_n信号触发

- 同步接口有一个时钟信号,数据读写和时钟同步

ONFI2.3协议规定的一个典型的闪存芯片管脚图,见图3-31。这个芯片对外输出数据位宽为8bit,Ssync是同步,Async是异步

图3-31 闪存芯片管脚图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

比较一下两种接口下的管脚定义,大部分都是一样的,区别就是表3-4中所示的四类信号

表3-4 同步异步管脚定义对比 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

先来看看异步数据写入的时序图,见图3-32

图3-32 异步写数据时序图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

上图中有5个信号:

- CLE:Command Latch Enable,CLE有效时IOx发送命令

- CE_n:Chip Enable,这个信号用来选通一个逻辑上的芯片——Target。为什么说是逻辑上的芯片?因为物理芯片里面封装了很多Target,每个Target都是完全独立的,只是有可能共享数据信号,所以通过CE_n来选择当前数据传输的是哪个Target,业内一般把Target叫作CE

- WE_n:Write Enable,写使能,这个信号是用户发给闪存的,有效时意味着用户发过来的写数据可以采样了

- ALE:Address Latch Enable,ALE有效时IOx发送地址

- IOx:数据总线

同时有很多时间参数,这里只介绍几个关键的参数:

- tWP :WE_n低电平脉冲的宽度

- tWH :WE_n高电平保持时间

- tWC :tWP与tWH合起来一个周期的时间

- tDS :数据建立时间,意思就是8bit数据要都达到稳定状态,最多这么长时间

- tDH :数据稳定时间,这段时间里数据信号稳定,可以来采样

时序图3-32,数据写入的时候,数据总线不能传输地址和命令,所以ALE和CLE无效。这个Target有数据传输,所以CE_n有效。每一个WE_n周期对应一次有效的数据传输

图3-33 异步读数据时序图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图3-33所示的异步数据读出时序,其中多了两个信号

- RE_n:读使能。这个信号是用户发给闪存的,每发一个读使能,闪存就在数据总线上准备好数据,等用户采样

- R/B_n:Ready/Busy。闪存正在进行内部读的时候,Busy_n有效,当操作完成且数据准备好之后,Ready有效,用户可以来读了

所以,用户向闪存发了读命令之后,Ready信号拉高,意味着数据准备好了。接着,用户发RE_n信号去读数据,每个RE_n周期,闪存发送一个有效数据到数据总线上,供用户采样,如图3-33所示

3.2.2 同步时序

同步时序最重要的两个信号是时钟CLK和DQS。现在的闪存基本都采用了DDR(Double Data Rate)技术,就是说每个时钟周期传输两拨数据。图3-34是同步模式下的数据写入时序图,介绍一下几个信号

- CLK:时钟。时钟信号由用户产生,在时钟信号的上升沿和下降沿都有数据被触发,实现DDR,意味着100MHz的时钟频率数据传输速率是200MT/s

- W/R_n:Write/Read_n。写的时候高电平,读的时候低电平

- DQS:Data Strobe。DQS用来区分出每个数据传输周期,便于接收方准确接收数据。读数据时,DQS由闪存产生,DQS上下沿和数据对齐。写数据时,DQS由用户产生,DQS中间对应数据的中间稳定区域。所以,DQS可以看成数据的同步信号

- DQ[7:0]:数据总线

图3-34 同步写数据时序图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

几个关键的时间参数:

- tCALS :CLE、W/R_n和ALE的建立时间

- tDQSS :数据输入到第一个DQS跳变沿的时间

了解了各种信号和时间参数,我们就能看懂上面的数据写入时序图。CLE和ALE同时有效之后的第一个CLK上升沿,数据开始准备并输出。经过tDQSS时间后,DQS开始跳变,并且跳变沿位于DQ数据信号的稳定位置。之后每半个时钟周期,输出一组数据

再来看看下面的读数据时序图图3-35,和写入差不多,只不过W/R_n信号是低电平,同时DQS跳变沿和数据上升沿同步

图3-35 同步读数据时序图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.2.3 闪存命令集

固态硬盘主控是通过一系列闪存命令与闪存进行通信的。每款闪存芯片都定义了其支持的命令,以ONFI 2.3协议为例,它定义的命令如表3-5所示。用户要使用这些功能时发送命令即可,比如读数据,就发送00h~30h,不过具体命令时序和使用方式要看专门的定义

表3-5 闪存命令集 表格来源于《深入浅出SSD:固态存储核心技术、原理与实战》

下面介绍一下几个比较常用的命令:

- Read:00~30h,读数据。读一个Page数据用这个命令

- Read Multi-plane:00~32h,同时读多个Plane的数据。多个Plane各读1个Page

- Change Read Column:05h~E0h,修改读列地址。Read命令从闪存介质读出一个Page的数据到闪存芯片里面的缓存,一个Page一般是8KB或者16KB,但是用户不一定需要所有数据,所以通过这个命令来修改传输数据的偏移地址。从某个Page内偏移地址开始进行数据传输

- Block Erase:60h~D0h,擦除一个Block

- Read Status:70h,查看最近一次操作的结果是成功还是失败

- Read Status Enhanced:78h,它和70h有什么区别?它是用在Multi-LUN操作的状态查看,可以指定查看哪个LUN的状态

- Page Program:80h~10h,写一个Page数据

- Page Program Multi-plane:80h~11h,同时写多个Plane的数据,写性能可以翻几倍

- Read ID:90h,可以读到在JEDEC注册的Manufacturer ID和Device ID

- Read Parameter Page:ECh,可以读到这个CE的各种配置参数,比如支持ONFI的哪个版本,是否支持Multi-plane,异步或同步时序模式是哪一种等

- Get Features/Set Features:EEh/EFh,这两个命令给用户提供设定一些参数的接口,比如设置同步异步或者选择传输速率

3.2.4 闪存寻址

图3-36所示是一个Target,就是之前说的一个可以独立工作的逻辑芯片。它包含2个LUN,每个LUN有2个Plane,每个Plane有很多Block,每个Block又有很多Page

图3-36 闪存内部架构 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

为了访问这些资源,闪存里面使用了行地址(Row Address)和列地址(Column Address)。列地址就是Page内部的偏移地址。ONFI协议中,行地址的定义如图3-37所示,从高位到低位依次为LUN、Block和Page地址,至于具体位宽,则和每个芯片的容量有关

图3-37 闪存地址划分 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

如图3-38所示,Plane是在Block地址的最低位。ONFI要求Multi-plane操作的时候,每个Plane的Page地址必须相同,Block地址不同的闪存要求不一样。比如Intel/Micron和东芝的闪存,在Multi-plane操作时,可以是不同的Block,但是三星的闪存,要求几个Plane操作的Block地址要相同。因为占的是Block地址的最低几位,所以进行Multi-Plane的时候,Plane一般有奇偶之分

图3-38 Plane地址位 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.2.5 读、写、擦时序

读时序 如图3-39所示,在用户发送命令00~30h之间传输了所读的地址,包括2个列地址和3个行地址。发完命令后,SR[6](Status Register,状态寄存器,bit 6)状态转为Busy,经过一段时间之后SR[6]状态转为Ready,数据就可以读了

图3-39 读时序 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

写时序 如图3-40所示,用户发了80h命令之后,发送写地址,一般列地址是0,因为要把一个Page写满,如果不从头开始写满一个Page,往往会导致数据出错。发完地址tADL时间之后,开始传输数据到闪存的缓存。数据传完,发送命令10h,闪存芯片开始向介质写入数据,SR[6]状态为Busy,在写操作完成后状态转为Ready

图3-40 写时序 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

擦除比较简单,如图3-41所示,在命令60h和D0h之间发送LUN和Block行地址即可,因为擦除是以Block为单位

图3-41 擦除时序 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3.2.6 ONFI与Toggle协议之争

前面讲的主要都是ONFI。事实上,闪存不只涉及ONFI协议,还有Toggle协议,对比一下管脚定义,其实区别也没那么大,见图3-42

图3-42 ONFI和Toggle管脚定义对比 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

Toggle同步模式下不用时钟,写数据用DQS差分信号跳变沿触发,读数据根据主控发的REN差分信号跳变沿发送读请求,DQS跳变沿输出数据

3.3 闪存特性

3.3.1 闪存存在的问题

1 闪存坏块

闪存块(Block)具有一定的寿命,当一个闪存块接近或者超出其最大擦写次数时,可能导致存储单元永久性损伤,如图3-43,不能再使用。随着闪存工艺不断向前发展,晶体管的尺寸越来越小,擦写次数也变得越来越少

图3-43 闪存损坏状态 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

闪存中的存储单元先天就有一些是坏的,或者说是不稳定的。并且随着闪存的不断使用,坏的存储单元越来越多。所以,用户写入闪存的数据,必须要有ECC纠错码保护,这样即使其中的一些比特发生反转,读取的时候也能通过ECC纠正过来。但若出错的比特数超过纠错能力范围,数据就会丢失,对这样的闪存块,应该弃之不再使用

闪存先天有坏块,也就是说有出厂坏块。并且,用户在使用过程中会新添坏块,所以必须有坏块管理机制

2 读干扰

另外,还应注意读干扰(Read Disturb)问题。从闪存读取原理来看,当你读取一个闪存页(Page)的时候,闪存块当中未被选取的闪存页的控制极都会加一个正电压,以保证未被选中的MOS管是导通的。这样问题就来了,频繁地在一个MOS管控制极加正电压,就可能导致电子被吸进浮栅极,形成轻微写,从而最终导致比特翻转,如图3-44所示。但是,这不是永久性损伤,重新擦除闪存块还能正常使用。要注意的是,读干扰影响的是同一个闪存块中的其他闪存页,而非读取的闪存页本身

图3-44 读干扰原理 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3 写干扰

除了读干扰会导致比特翻转,写干扰(Program Disturb)也会导致比特翻转。还是要回到闪存内部的写原理上来,如图3-45所示

图3-45 写干扰原理 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

写一个闪存页的时候,数据是0和1混合的。由于擦除过的闪存块所有的存储单元初始值是1,只有写0的时候才真正需要操作。如图3-45所示,方框里的单元是写0,即需要写的,圆圈里的单元的代表写1,并不需要写操作。这里把方框里的单元称为Programmed Cells,圆圈里的单元称为Stressed Cells。写某个闪存页的时候,我们是在其Wordline控制极加一个正电压,图3-47中是20V。Programmed Cells所在的String是接地的;不需要写的单元所在的String接一个正电压,图3-47中为10V。这样最终产生的后果是,Stressed Cell也会被轻微写。与读干扰不同的是,写干扰影响的不仅是同一个闪存块当中的其他闪存页,自身闪存页也会受到影响。相同的是,都会因不期望的轻微写导致比特翻转,都会产生非永久性损伤,经擦除后,闪存块还能再次使用

4 存储单元间的耦合

还有一个问题,就是存储单元之间的耦合影响(Cell-to-Cell interference)。前面提到,浮栅极闪存存储电荷的是导体,因此存储单元之间存在耦合电容,这会使存储单元内的电荷发生意外变化,最终导致数据读取错误。

5 电荷泄漏

存储在闪存存储单元的电荷,如果长期不使用,会发生电荷泄漏。这同样会导致非永久性损伤,擦除后闪存块还能使用

3.3.2 寿命

图3-46这张0和1的分布图,横轴是电压,纵轴是存储单元的数量。0的区域表示被写过的那些单元电压分布区间,1的区域是被擦过的那些单元电压分布区间。所以说,如果要正确地读到数据,0和1这两个区间要尽量分割清楚,保证它们的主峰之间有足够远的距离。除此之外,阈值电压也不能太偏

图3-46 SLC电压分布 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

要读的单元栅极加0V电压,这时擦过的晶体管阈值电压是-Vt ,导通,沟道有电流,Bitline端的传感器能够检测到,读到“1”。而经过写的晶体管阈值电压是+Vt ,不导通,沟道电流很小,读为“0”。随着擦写次数的增加,会发生3种故障:

- 擦过的晶体管阈值电压变大,从-Vt 向0V靠近,这样读的时候沟道电流变小,传感器检测不到,读出错

- 写过的晶体管阈值电压变小,从+Vt 向0V靠近,有可能会被误检测为擦过的状态

- 写过的晶体管阈值电压变大,如图3-47所示,>5V,即使控制极加5V电压,它也是截止的,有可能在其他的单元读的时候,把整个Bitline都给关了

图3-47 读操作电压示例 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

浮栅晶体管对浮栅极下面的绝缘层(Tunnel氧化物)很敏感,该氧化物厚度变薄(制程不断减小导致的)或者老化(Degradation,擦写次数多了)对浮栅极里面的电荷影响很大。我们之前介绍了Charge Trap晶体管,其实随着擦写次数增多,浮栅晶体管的氧化层渐渐老化,产生不少Charge Trap,这些陷阱会吃掉电子,导致写之后,进入浮栅的电子数量会减少,最终的结局就是0和1两个区间不断靠近

如图3-48所示,上面是写后的阈值电压,下面是擦除后的阈值电压,很明显,擦除后的阈值电压在擦很多次之后显著变高。所以,一般擦除之后会做校验,方法是把所有的Wordline设为0V,再去检测每个Bitline的电流。如果某个Bitline电流是0,就意味着有个单元的擦除阈值电压接近0V,导致晶体管关断。所以这个闪存块应该标为坏块

图3-48 阈值电压变化图 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

了解了闪存寿命的原理之后,看看固态硬盘设计实践中怎么解决这个问题。一般有以下方法:

- Wear Leveling:通过磨损平衡算法,让所有的闪存块均衡擦写,避免少数闪存块先挂掉,导致固态硬盘容量下降

- 降低写放大:写放大越低,固态硬盘的磨损速度越慢

- 用更好的纠错算法:纠错能力越强,容许的出错率越高,故采用更好的纠错算法可以延长硬盘使用寿命

3.3.3 闪存测试

固态硬盘内部需要对闪存做测试,原因是:

- 闪存厂商卖给你的闪存不一定都是好的,总是有概率存在故障芯片

- 固态硬盘制造过程中有合格率问题,不能保证每个闪存芯片都焊接得完美无缺

- 固态硬盘制造商为了降低成本,会从各种渠道获得低价闪存芯片,这些芯片质量没有保障,需要固态硬盘制造商自己筛选

图3-49 BGA焊接空洞 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

图3-49所示是BGA封装的焊球X光片,可以看出里面有个空洞,导致电路信号故障。所以,固态硬盘出厂前要对每一块闪存进行测试,测试方法如下:

- 测试每个CE是否可以正常操作,比如Reset、Read ID等

- 对每个LUN、Plane进行读写测试,要考虑到一定的比特翻转率,看看写入的数据和读出差距有多大。写入数据要选择不同的数据类型,比如连续的0或者连续的1。存储器件测试有很多专用数据格式,有兴趣的读者可翻看各种论文,也可以参考著名的内存测试软件memtest的测试方法

3.3.4 MLC使用特性

对MLC来说,擦除一个闪存块的时间大概是几毫秒。闪存的读写则是以闪存页为基本单元的。一个闪存页大小主要有4KB、8KB、16KB几种。对MLC或者TLC来说,写一个闪存块当中的闪存页,应该顺序写Page0、Page1、Page2、Page3……禁止随机写入,比如Page2、Page3、Page5、Page0……为什么?原因主要有二:

- 一个存储单元包含两个闪存页数据,要先写Lower Page,再写Upper Page

- 相邻单元之间有耦合电容,工艺上要求后面的闪存页写操作时前面的闪存页已经写过

但对读来说,没有这个限制。SLC也没有这个限制

MLC有其特有的一些问题:

- 正如前面提到的,MLC最大擦写次数会变小。这样,就更需要Wear Leveling技术来保证整个存储介质的使用寿命

- 对MLC来说,一个存储单元存储了2bit的数据,对应着两个Page:Lower Page和Upper Page。假设Lower Page先写,然后在写Upper Page的过程中,由于改变了整个单元的状态,如果这个时候掉电,那么之前写入的Lower Page数据也会丢失。也就是说,写一个闪存页失败,可能会导致另外一个闪存页的数据损坏

- 前面说到,不能随机写。不能先写Upper Page,然后再写Lower Page,这点就限制了我们不能随意地写

- 写Lower Page时间短,写Upper Page时间长,所以会看到有些闪存页写入速度快,有些闪存页写入速度慢

两条存储行业的规矩:

- 一般在没有盘内缓存的情况下,我们认为写到硬盘的数据如果已经返回写成功,那么这个数据就是安全的。数据写到物理介质上就可以放心了

- 如果数据在写的过程中发生了异常掉电,那么该数据即使丢了也可以接受,毕竟用户认为数据还没写完

但是Lower Page数据损坏打破了这个常识:尽管已经成功写到了盘里,但是假如该数据位于Lower Page上,很不幸的是,恰好过了不久,后面有数据写对应的Upper Page时发生了异常掉电,那就会导致Lower Page上已经写好的数据也被破坏。也就是说,固态硬盘正在写的时候,如果发生了异常掉电,有可能会丢失之前写入的数据

消费级固态硬盘研发工程师采用了很多技术来防止这种情况发生

- 只写Lower Page:成本比较高,只适合关键数据和土豪

- Lower Page和Upper Page打包写:每次数据量多凑点,争取Lower Page和Upper Page都写(需要闪存支持One Pass Programming)

- 定期填充Upper Page:消费级固态硬盘要求省电,所以会频繁进入省电模式,可能安静个几百毫秒就自动休眠了。休眠之前检查是不是有Lower Page写过了,有Upper Page还没写的情况,就把Upper Page也写一下

- 写Lower Page数据时,备份该数据到别的闪存块上,直到它对应的Upper Page数据写完。这样即使掉电导致Lower Page数据丢失,也可使用备份数据进行还原

- MLC闪存块当SLC块使用,强迫用户数据写到SLC块,随后以垃圾回收的方式把数据从SLC闪存块搬到MLC闪存块

3.3.5 读干扰

读干扰为什么会导致性能下降?下面将解释原因。

读干扰会导致浮栅极进入电子。由于有额外的电子进入,会导致晶体管阈值电压右移(Data Retention问题导致阈值电压左移),如图3-50所示

图3-50 阈值电压偏移 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

由于晶体管阈值电压偷偷发生了变化(变大了),闪存内部逻辑如果还是按照之前的参考电压加在控制极上然后去判断数据,肯定会发生误判,也就是读到错误的数据

阈值电压右移的速度,也就是读干扰影响数据的程度,一方面与读该闪存块上数据的次数有关,读得越多,右移越多,影响越大;一方面还跟闪存块的擦除次数有关,擦写次数越多,绝缘效果越差,电子进入浮栅极就越容易,读干扰的影响也就越大

闪存使用者如何应对读干扰呢?

一般做法是记录每个闪存块读的次数,赶在这个数值达到阈值(闪存厂家提供)之前,把闪存块上所有的数据刷新一遍(读出来,擦除,然后写回),或者把数据搬到别的地方。回到开头那个问题,读干扰为什么会导致固态硬盘性能下降?就是因为一个闪存块上的数据读的次数太多了,固件需要赶在数据出错前,把整个闪存块数据刷新或者搬移,避免数据出错,但这会占用底层带宽,导致主控读写性能下降

有人研究发现,减小Vpass (加在没有被读的那个Wordline上的电压)可以缓解读干扰。因为Vpass 变小,电场减弱,吸入电子的能力减弱,自然能缓解读干扰的影响。但是,一方面,现在闪存厂商都没有开放调Vpass 电压的接口给用户;另一方面,过低的Vpass 可能导致读失败。该方法只能起到缓解作用,不能从源头上杜绝读干扰的影响

3.3.6 闪存数据保存期

无论用任何存储技术,存储的数据都不能永远保存,都会有个保存时间。闪存中,数据保存时间的问题叫作Data Retention。到了期限,数据就会出错,标志就是从闪存读出来的数据无法用ECC纠错成功。我们知道闪存一般有以下错误:

电气问题:比如虚焊或者芯片故障,导致正常命令无法执行或者数据错误率异常高。这种问题在闪存或固态硬盘出厂测试时就会被发现读、写、擦失败:基本命令执行失败,通过状态位可以读到结果。这些问题在芯片使用过程中也有可能发生,但是概率非常小ECC纠错失败:其实就是数据错误率太高,超过了纠错算法的纠错能力。Data Retention是其中一个元凶

闪存存储的机理是通过量子隧道效应,电子跃迁到浮栅层并停留在那里。随着时间的流逝,电子还是有一定概率离开浮栅层,回到沟道里面,离开的电子多了就有可能导致写过的单元读出来的结果跟擦除过的一样,也就是说数据出错了。Data Retention和浮栅层下面的氧化层厚度有关,毕竟氧化层越厚,电子离开的概率越小。有研究表明,氧化层厚度如果是4.5nm,那么理论上数据可以保存10年

图3-52是闪存基本单元浮栅晶体管的截面图。最上面是控制层,中间是浮栅层,浮栅上面是多晶硅氧化层,下面是隧道氧化层。控制电压很高的时候,会产生量子隧穿效应,电子从衬底Substrate出发,穿过隧道氧化层,进入浮栅保存起来,就完成了写操作。反之,在控制层加很强的负电压,电子就从浮栅量子隧穿,回到衬底,这个操作叫作擦除。不过,控制层不加电压的时候,氧化层依然会产生一个电场,叫作本征电场,它是由浮栅里面的电子产生的。在这个电场的作用下,电子会从浮栅慢慢泄露,泄漏的多了,数据就会发生错误。从写入操作到电子慢慢泄漏,直到数据出错,这个期限叫作数据保存期,在SLC时代,这个时间很久,有好几年,但是到了TLC时代,不到一年,有的只有几个月

图3-52 浮栅晶体管的本征电场和TAT效应 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

那为什么闪存用得越久,数据保存时间越短呢?这要怪一个效应:Trap-assisted tunneling(TAT)。如图3-52(b)所示,我们知道隧道氧化层是绝缘的,但是随着闪存的使用,历经很多次的擦写,氧化层和浮栅层的爱情终于要走到终点了,因为经过这么年风风雨雨,氧化层老了,有不少通过它的电荷被滞留下来,绝缘体有了导电性。这样,电荷从浮栅跑得就更快了。所以,闪存擦写次数越多,数据保存时间就越短。到最后快到额定擦写次数的时候,比如3000次,刚写的数据就很容易出错

不过,氧化层并不总是在截留电荷,有时候它拦截的电荷也会离开,叫作Charge de-trapping。只不过离开的既有正电荷,也有负电荷,所以对阈值电压的影响是双向的

怎样解决Data Retention的问题呢?一般固态硬盘会采用Read Scrub技术,或者叫数据巡检、扫描重写技术等

Sun公司开发的大名鼎鼎的ZFS(Zettabyte File System)文件系统。ZFS的设计者发现,有很多用户的数据长期没有读过,更别说被重写了。即使是数据读取频繁的数据库应用,也存在长期不被访问的数据,它们寂寞地躲在角落里,长期无人问津。但是,不管什么类型的磁盘,总是会有概率发生比特翻转,导致数据出错,等你需要这份数据的时候,错误有可能比较严重,根本恢复不出原样。在ZFS文件系统中,每个数据块都有自己的校验码Checksum,只要被读了,就可以通过Checksum发现数据是否出错,提前对出错的数据块进行纠错。所以,ZFS提供了一个功能叫Scrub,对文件系统进行扫描,提前发现那些出错的数据,并纠错重写

固态硬盘的Read Scrub技术跟ZFS类似,在固态硬盘不忙的时候,按照一定的算法,扫描全盘,如果发现某个闪存页翻转比特数量超过一定阈值,就重写数据到新的地方。这样做的好处是避免数据放太久从而导致比特翻转数量超过ECC算法的纠错能力,这样能减少ECC不可纠错误

3.4 闪存数据完整性

闪存的一个特性就是随着闪存的使用以及数据存储时间的变长,存储在闪存里面的数据容易发生比特翻转,出现随机性错误。这个问题随着闪存制程的变小越发严重。因此,使用闪存作为存储介质的固态硬盘,需要采用一些数据完整性的技术来确保用户数据可靠不丢失。常见的技术有:

- ECC纠错

- RAID数据恢复

- 重读(Read Retry)

- 扫描重写技术(Read Scrub)

- 数据随机化

3.4.1 读错误来源

闪存数据发生错误,主要有以下几个原因:

1 擦写次数增多

随着闪存块擦写次数增多,氧化层逐渐老化,电子进出存储单元越来越容易,因此存储在存储单元的电荷容易发生异常,导致数据读错误,如图3-53所示

图3-53 同一个闪存芯片内不同闪存块在不同寿命时的RBER 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

2 Data Retention

随着时间的推移,存储在存储单元的电子会流失,整个阈值电压分布向左移动,导致读数据的时候发生误判,如图3-54所示

图3-54 阈值电压分布随着时间偏移 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

3 读干扰

读一个Wordline数据时,需要施加Vpass 电压在其他Wordline上,导致其他闪存页发生轻微写。如果读的次数过多,轻微写累积起来就会使阈值电压分布发生右移,导致读数据时候发生误判,即读数据错误,如图3-55所示

图3-55 读干扰后阈值电压偏移 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

4 存储单元之间干扰

由于存储电子的浮栅极是导体,两个导体之间构成电容,一个存储单元电荷的变化会导致其他存储单元电荷变化,而受影响最大的就是与它相邻的存储单元。周围的单元是不同的状态时,中心单元的阈值电压是不一样的,如图3-56所示

图3-56 周围单元不同状态时的阈值电压分布 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

5 写错误

写错误一般发生在MLC或者TLC 2-pass(先写Lower Page,然后再写Upper Page)写过程中。写Upper Page的时候,它是基于之前Lower Page的状态,然后再写每个存储单元到目标状态。如果写Upper Page的时候,Lower Page数据已经出错(注意写Upper的时候,Lower Page的数据是不会经过控制器ECC纠错的,写过程发生在闪存内部),就会导致存储单元写到一个不期望的状态,即发生写错误

TLC 1-pass program则没有这个问题,因为Lower Page和Upper Page是一次性同时写入,写Upper Page不依赖于Lower Page数据。当然,如果一开始擦除状态就不对,那么还是会发生写错误

3.4.2 重读

闪存有几种缺陷,对于电压分布平移的问题尚可想办法恢复,因为数据之间还是清楚隔离的

图3-57以MLC为例,每个存储单元存储两个比特的数据,一共有四种状态。当四种状态的电压分布发生平移后,如果还是采用之前的参考电压去读取的话,就可能会出现读取数据失败的情况。使用重读技术后,我们可以不断改变参考电压,来尝试找到可以读出数据的电压点,直到正确读出数据。理论上,只要这四种状态的电压分布没有发生重叠,就可以通过重读恢复数据

图3-57 平移后电压分布 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

还有更复杂的重读,叫作Advanced Read Retry。先读附近的单元确定状态,再用不同参考电压读两次要读的单元,根据附近单元数据决定选择哪一个

3.4.3 ECC纠错码

固态硬盘控制器上面都有ECC纠错模块,有些闪存内部也集成了ECC纠错模块。常用闪存ECC纠错算法有:

- BCH(Bose、Ray-Chaudhuri与Hocquenghem三位大神名字的首字母)

- LDPC(Low Density Parity Check Code)

- 目前市面上很多固态硬盘控制器上采用的是BCH,但采用LDPC正成为一种趋势

用户数据最终都是写在闪存页(Page)上面,闪存页空间除了用户空间,还有额外的预留空间,这部分空间可以用来写ECC校验数据。用户数据大小固定,需要更强的纠错能力,这就需要更多的ECC空间。因此,纠错强度受限于闪存页的预留空间。越多的预留空间就能提供越强的ECC纠错能力

目前绝大多数固态硬盘都采用静态ECC纠错方案,ECC纠错单元(用户数据)和ECC校验数据大小在整个固态硬盘生命周期都是固定的,也就是说纠错能力始终保持不变。由于闪存在使用初期内部发生比特翻转的概率小,而随着闪存的使用,出错概率逐渐变大,因此有些固态硬盘开始采用动态ECC纠错方案:开始使用更少的纠错码,这样在闪存的页里面可以存储更多的用户数据;随着固态硬盘的使用,纠错能力需要加强,用户数据在闪存页里面占的比例变小,纠错码所占比例变大。动态ECC纠错方案就是随着固态硬盘的使用,动态调整其ECC纠错能力。动态ECC纠错有什么好处?如果开始使用更少的ECC校验数据,那么每个页能写入的用户数据就更多,相当于固态硬盘拥有更多的OP(Over Provisioning,预留空间),减小了写放大;同时,在数据从控制器写入或者读取闪存的通道上,用户数据越多,ECC校验数据越小,带宽利用率高

其实,动态ECC的优势不仅体现在随着时间的推移ECC纠错能力会发生变化,而且体现在固态硬盘的闪存位置上每个Die甚至每个闪存页有不同的纠错能力。在固态硬盘闪存阵列里,有些Die可能质量好点,有些Die可能质量差点,好的Die可以用更少的ECC纠错代码;相反,差的Die就需要更强的ECC纠错。对MLC来说,Lower Page相对Upper Page更稳定一些,因此可以使用弱一些的ECC保护;相反,Upper Page则需要更强的ECC保护

3.4.4 RAID

当闪存中数据比特发生翻转的个数超出ECC纠错能力范围后,ECC纠错就无能为力了。在一些企业级,以及越来越多的消费级固态硬盘上,都在使用RAID(Redundant Arrays of Independent Disks)纠错技术。类似磁盘阵列,固态硬盘内部本质就是一个闪存阵列,所以可以借鉴磁盘阵列技术来确保数据的完整性。固态硬盘的RAID一般采用RAID 5

以图3-58所示为例,某个固态硬盘的闪存阵列由5个Die构成,Die 0~3存储的是用户数据,Die P则存储校验数据,为Die 0、Die 1、Die 2和Die 3数据之“异或”。假设Die 1上出现ECC不可纠的错误,那么可以通过读取Die 0、Die 2、Die 3和Die P对应位置上的数据,然后做“异或”,就能恢复出Die 1上的数据

图3-58 RAID 5 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

采用RAID 5的固态硬盘只能恢复单个ECC不可纠的数据,如果出现多个ECC不可纠的错误,它也无能为力

由于采用了冗余纠错技术,它需要额外的空间来存储冗余数据(校验数据),因此必然会牺牲用户空间

图3-59 传统RAID 5 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

如图3-59所示,对传统磁盘RAID 5来说,数据按照条带来写。比如一个磁盘组有4个磁盘,其中一个是校验盘,条带大小为48KB,被拆成三个16KB写到三个盘上,最后一盘是校验数据——三个16KB数据的“异或”值。修改任何一个16KB数据块,都需要重新生成校验数据,并更新校验数据块

一般固态硬盘内部的RAID是由不同Die上的Block组成的阵列,绑定在一起:同时被写,同时被垃圾回收,同时被擦除。好处是稳定,缺点是不够灵活。固态硬盘内部的RAID Block太大了,不太灵活,使得空间被浪费。比如进入休眠之前必须把没写完的条带剩余空间用随机数填满,增加写放大。RAID Block个头大,效率就降低了,有时RAID阵列中某个Block有效数据还很多,但是因为整个阵列有效数据少,不得不整体垃圾回收

3.4.5 数据随机化

在写闪存的时候,如果只是简单地把数据加纠错码写进去,那会遇到很多错误,有时候是写失败,有时候是读出来的数据错误率太高。为什么?因为数据没有随机化。闪存是通过控制栅施加电压来存储数据的,对某些写入的数据样式很敏感,不断地输入全0或者全1,很容易导致闪存内部电量不均衡,从而造成信号抗干扰性下降,导致这些数据在闪存中可靠性变差

图3-60 没有随机化(虚线)和随机化(实线)电压分布对比 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

从物理原理上看,闪存写入数据需要做随机化有两个原因:

- 1)

让0和1的分布充分隔离。 图3-60是MLC内部的各个存储状态电压分布图,实线是随机化后的分布,每个状态都充分隔离;虚线是没有随机化的分布,有些状态的分布明显变宽了,随着时间流逝或者寿命缩短,这些分布会和周边发生交集,导致读数据出错 - 2)

降低相邻单元之间的耦合电压产生的影响。 如3-61所示,对一个单元影响最大的是其周围的4个直接相邻的单元,这些单元的状态直接影响到中间单元的阈值电压

图3-61 周围单元对中心单元的影响 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

因此,固态硬盘控制器或者闪存内部都有数据随机化模块,它对用户写入的数据加入扰码,使最终写入闪存的数据0和1基本保持均衡,减小数据发生比特翻转的概率。一般闪存厂商会推荐使用AES加密算法实现数据随机化

数据随机化在数据最终写到闪存之前,ECC加校验数据之后,数据流如图3-62所示,数据随机化也可以在ECC校验之前做,两者顺序可交换

图3-62 数据随机化数据流 图片来源于《深入浅出SSD:固态存储核心技术、原理与实战》

致谢《深入浅出SSD:固态存储核心技术、原理与实战》

转自:

《深入浅出SSD:固态存储核心技术、原理与实战》----学习记录(一)-CSDN博客

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?