前言

本文是对S5PV210芯片手册中启动部分的翻译,原文位于《S5PV210 RISC Microprocessor User's Manual, Revision 1.10》第二部分“系统”中的第三章“时钟控制器”。

本章讲述S5PV210支持的时钟管理单元(CMU)。系统控制器(SYSCON)管理S5PV210中的CMU和电源管理单元(PMU)。

1.1 时钟域

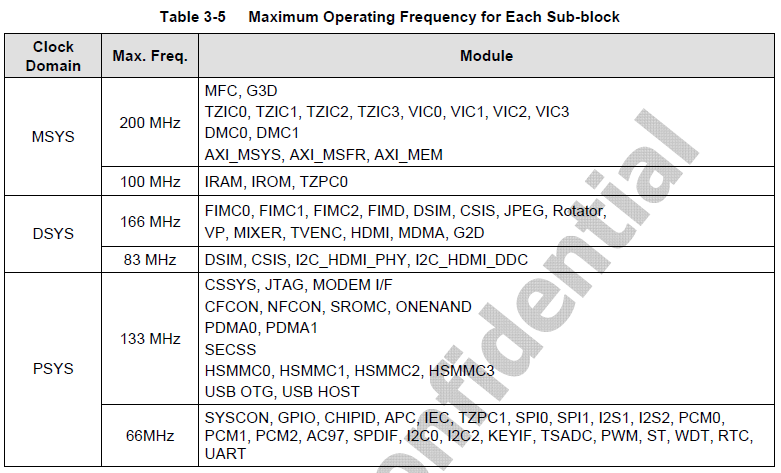

S5PV210由三个时钟域组成,称为主系统(main system, MSYS),显示系统(display system, DSYS),和外设系统(peripheral system, PSYS),如图3-1所示。

•MSYS域由Cortex A8处理器, DRAM内存控制器(DMC0 and DMC1), 3D, 内部SRAM (IRAM和IROM), INTC, 和 配置接口(SPERI)组成。Cortex A8仅支持同步模式,因此必须与200MHz AXI总线同步运行。

• DSYS域由显示相关的模块组成,包括FIMC, FIMD, JPEG, 和多媒体IP (所有在X, L和T模块中提到的其它IP),如图3-1所示。

• PSYS域用于安全、I/O外设,和低功耗音频播放。

• 每个总线系统分别以200 MHz(最大),166 MHz和133 MHz运行。两个不同的域之间有异步总线桥(BRG)。

1.2 时钟声明

图3-2显示了S5PV210中的时钟分类。S5PV210中的顶层时钟包括:

•来自时钟管脚的时钟:XRTCXTI, XXTI, XUSBXTI和XHDMIXTI;

•来自CMU的时钟(例如,ARMCLK, HCLK, PCLK等等);

•来自USB PHY的时钟;

•来自GPIO管脚的时钟。

1.2.1 来自时钟管脚的时钟

下面的时钟由时钟管脚提供。但是,你可以禁止时钟管脚。

•XRTCXTI:指定一个来自由XRTCXTI和XRTCXTO管脚提供的32,768 KHz晶振pad的时钟。RTC使用这个时钟作为实时时钟的源。

•XXTI:指定一个来自由XXTI和XXTO管脚提供的晶振pad的时钟。当USB PHY不是用于商业集 (译者注:commercial set, 不确定这么翻译是否正确) 时,CMU和PLL使用这个时钟来产生其它时钟模块(APLL, MPLL, VPLL, 和EPLL)。输入频率范围12 ~ 50 MHz。推荐使用24 MHz晶振,因为iROM被设计成基于24MHz输入时钟。

•XUSBXTI:指定一个来自由XUSBXTI和XUSBXTO管脚提供的晶振pad的时钟。这个时钟供应给APLL, MPLL, VPLL, ELL, 和USB PHY。关于USB PHY时钟的跟多信息,参考8.4章节 “USB控制器”和8.5章节“USB HS OTG”。推荐使用24 MHz晶振,因为iROM被设计成基于24MHz输入时钟。

•XHDMIXTI:指定一个来自由XHDMIXTI和XHDMIXTO管脚提供的27 MHz晶振pad的时钟。VPLL或HDMI PHY 产生54MHz时钟用于TV编码。

• XXTI和XXTO使用宽范围OSC pads;

• XUSBXTI和XUSBXTO使用宽范围OSC pads;

• XHDMIXTI和XHDMIXTO使用宽范围OSC pads;

• XRTCXTI和XRTCXTO使用OSC pads用于RTC;

• ARMCLK指定Cortex A8的时钟 (最高达1GHz);

• HCLK_MSYS指定MSYS时钟域的AXI时钟,如图3-1所示。最高运行频率为200 MHz。

• PCLK_MSYS指定MSYS时钟域的APB时钟,如图3-1所示。最高运行频率为100 MHz。

• HCLK_DSYS指定DSYS时钟域的AXI/AHB时钟,如图3-1所示。最高运行频率为166 MHz。

• PCLK_DSYS指定DSYS时钟域的APB时钟,如图3-1所示。最高运行频率为83 MHz。

• HCLK_PSYS指定PSYS时钟域的AXI/AHB时钟,如图3-1所示。最高运行频率为133 MHz。

• PCLK_PSYS指定PSYS时钟域的APB时钟,如图3-1所示。最高运行频率为66 MHz。

• 特定时钟制定了所有除了总线时钟和处理器核时钟之外的所有时钟。

1.2.2 来自CMU的时钟

CMU使用来自时钟pads (XRTCXTI, XXTI, XUSBXTI和XHDMIXTI),四个PLL(APLL, MPLL, EPLL和VPLL),USB PHY和HDMI PHY时钟产生内部中频时钟。这些时钟中,有些可以被选择,预分频,提供给相应的模块。推荐为APLL, MPLL, EPLL 和VPLL使用24 MHz的输入时钟源。

为了产生内部时钟,使用了下列的组件:

• APLL使用FINPLL(参考图3-1)作为输入,产生30 MHz ~ 1 GHz;

• MPLL使用FINPLL作为输入,产生50 MHz ~ 2 GHz;

• EPLL使用FINPLL作为输入,产生10 MHz ~ 600 MHz;

• VPLL使用FINPLL或SCLK_HDMI27M作为输入,产生10 MHz ~ 600 MHz,这个PLL产生54 MHz的视频时钟;

•USB OTG PHY使用XUSBXTI,产生30 MHz和48 MHz;

•HDMI PHY使用XUSBXTI或XHDMIXTI,产生54MHz;

在典型的S5PV210用用中,

• Cortex A8和MSYS时钟域使用APLL(ARMCLK, HCLK_MSYS和PCLK_MSYS);

• DSYS和PSYS时钟域 (HCLK_DSYS, HCLK_PSYS, PCLK_DSYS和PCLK_PSYS)和其它外设时钟域 (audio IPs, SPI等等)使用MPLL和EPLL;

• 视频时钟使用VPLL;

时钟控制器允许绕过PLL用于低速时钟。它同时使用软件连接/断开来自各个模块的时钟,以降低功耗。

1.3 时钟关系

时钟具有下列关系:

•MSYS时钟域

− freq(ARMCLK) = freq(MOUT_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_MSYS) = freq(ARMCLK) / n, where n = 1 ~ 8

− freq(PCLK_MSYS) = freq(HCLK_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_IMEM) = freq(HCLK_MSYS) / 2

• DSYS时钟域

− freq(HCLK_DSYS) = freq(MOUT_DSYS) / n, where n = 1 ~ 16

− freq(PCLK_DSYS) = freq(HCLK_DSYS) / n, where n = 1 ~ 8

• PSYS时钟域

− freq(HCLK_PSYS) = freq(MOUT_PSYS) / n, where n = 1 ~ 16

− freq(PCLK_PSYS) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

− freq(SCLK_ONENAND) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

高性能运行时的值:

• freq(ARMCLK) = 1000 MHz

• freq(HCLK_MSYS) = 200 MHz

• freq(HCLK_IMEM) = 100 MHz

• freq(PCLK_MSYS) = 100 MHz

• freq(HCLK_DSYS) = 166 MHz

• freq(PCLK_DSYS) = 83 MHz

• freq(HCLK_PSYS) = 133 MHz

• freq(PCLK_PSYS) = 66 MHz

• freq(SCLK_ONENAND) = 133 MHz, 166 MHz

• PLL

−APLL可以驱动MSYS域和DSYS域。它可产生高达1 GHz的时钟,49:51占空比;

−MPLL可以驱动MSYS域和DSYS域。它可供应的时钟,高达2 GHz,40:60占空比;

−EPLL主要用于产生音频时钟;

−VPLL主要用于产生视频系统运行时钟,54 MHz;

−典型地,APLL驱动MSYS域,MPLL驱动DSYS域。

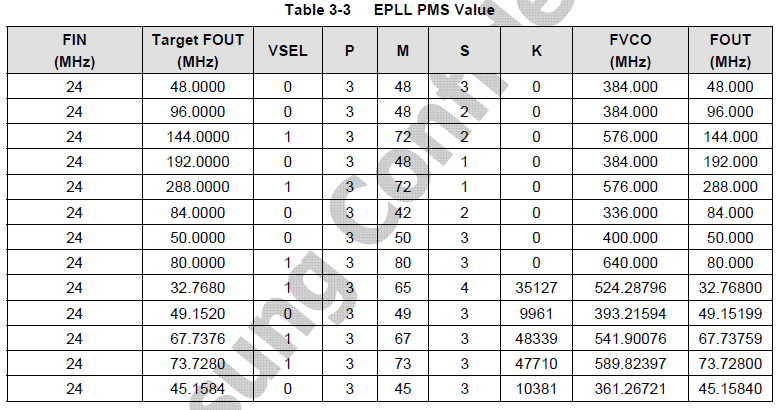

注意:尽管有方程可以用于选择PLL的值,我们强烈推荐只使用PLL值推荐表中的值。如果你必须使用其它值,请联系我们。

1.3.1 APLL PLL PMS推荐值

1.3.2 MPLL PLL PMS推荐值

1.3.3 EPLL PLL PMS推荐值

1.3.4 VPLL PLL PMS推荐值

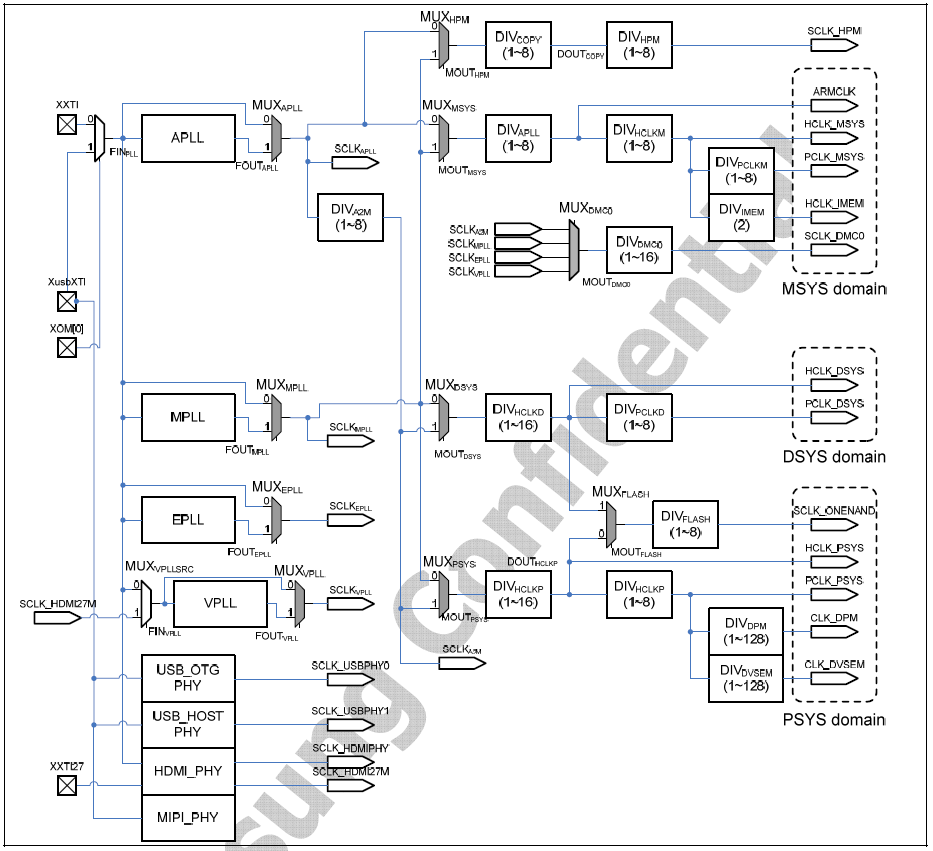

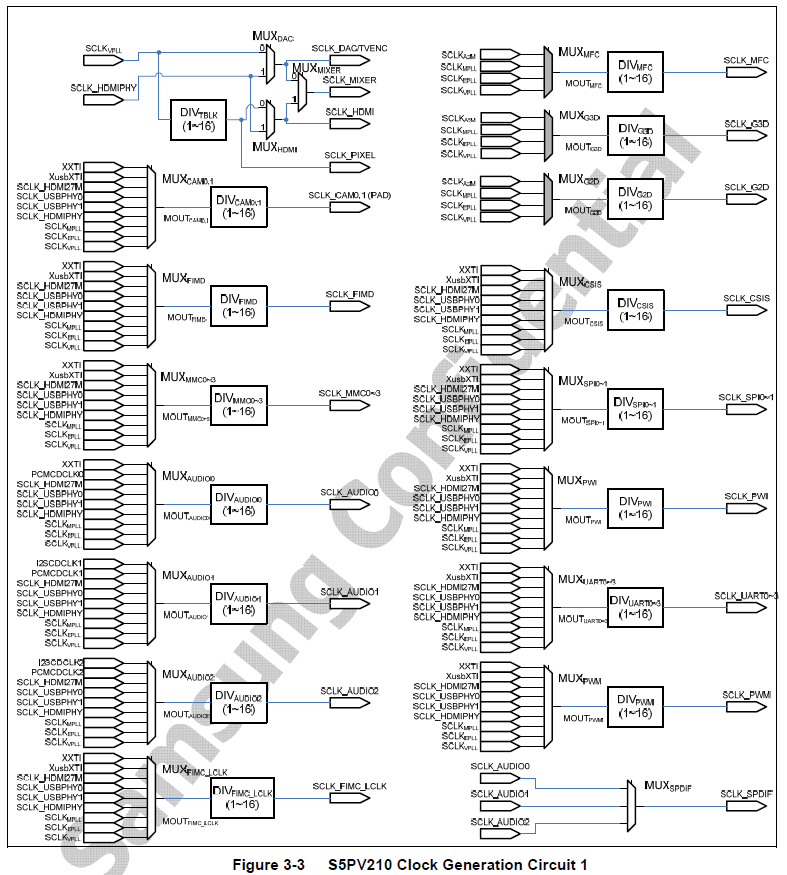

1.4 时钟产生

图3-3显示了时钟产生逻辑的框图。一个外部晶振时钟连接到振荡放大器。PLL将输入低频转换为S5PV210要求的高频时钟。时钟产生模块也包括一个内建逻辑来稳定每个系统复位后的时钟频率,因此在时钟稳定之前需要一些时间。

图3-3也显示了两类时钟多路复用器。灰色的时钟多路复用器代表无干扰时钟多路复用器,如果时钟选择改变它不会产生毛刺。白色的时钟多路复用器代表非无干扰时钟多路复用器,当时钟源改变时会有毛刺。在使用每个时钟多路复用器时,必须特别小心。

对于无干扰多路复用器,应该保证当时钟选择从一个改到另一个时,两个时钟源都在运行。如果不是这样,时钟改变并不能完全完成,导致时钟输出会有未知状态。

对于非无干扰多路复用器,当时钟选择改变时会可能有一个毛刺。为避免毛刺信号,在改变时钟源之前,推荐禁止非无干扰多路复用器的输出。在时钟修改完成之后,用户可以重新使能非无干扰时钟多路复用器的输出,从而不会有因为时钟改变而产生的毛刺。屏蔽非无干扰多路复用器的输出由时钟源控制寄存器处理。

图3-3中显示的时钟分频器在括号中说明了可能的分频值。这些分频值可以由时钟分频寄存器在运行时决定。一些时钟分频器只有一个分频值,用户无法改变它们,在时钟分频寄存器中无相应的域。

1.5 时钟配置过程

当时钟配置改变时须遵循下述规则:

•无干扰多路复用器的所有输入必须在运行;

•当一个PLL断电,不应选择这个PLL的输出。

基本的SFR配置流程:

a.打开一个PLL(一旦打开任何PLL,别去关闭它)

(1). (A,M,E,V)PLL_CON[31] = 1; // PLL上电 (参考(A, M, E, V) PLL_CON SFR)

(2). wait_lock_time; // 等待直到PLL锁定

(3). (A, M, E, V)PLL_SEL = 1; // 在PLL输出时钟稳定之后,选择PLL输出时钟代替输入参考时钟(参考CLK_SRC0 SFR第0, 4, 8, 12位)

b.修改PLL PMS值

Set PMS values; // 设置PDIV, MDIV和SDIV的值(参考(A, M, E, V) PLL_CON SFR)

c. 修改系统时钟分频器的值

CLK_DIV0 [31:0] = target value0;

d. 为特殊时钟修改分频器的值

CLK_DIV1 [31:0] = target value1;

CLK_DIV2 [31:0] = target value2;

时钟门控 S5PV210可以禁止每个不需要IP的时钟运行。这降低了动态功耗。

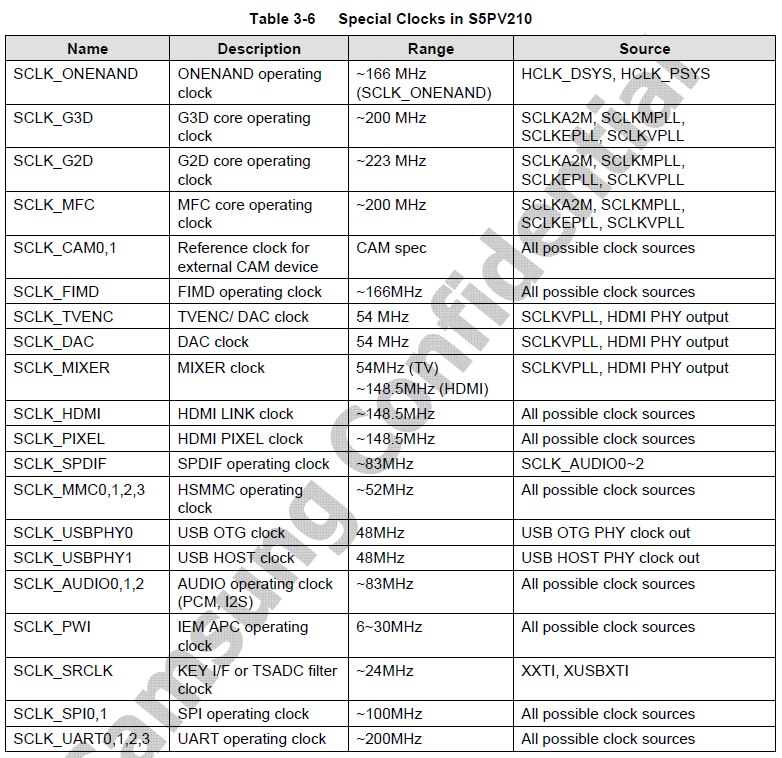

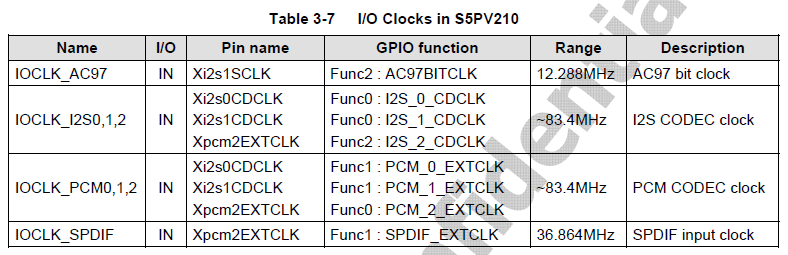

1.6 特殊时钟描述

1.6.1 特殊时钟表

所有可能的时钟源包括XXTI, XUSBXTI, SCLK_HDMI27M, SCLK_USBPHY, SCLK_HDMIPHY, SCLKMPLL, SCLKEPLL和SCLKVPLL。

a. XXTI和XUSBXTI分别表示外部晶振;

b. SCLK_USBPHY表示USB PHY 48 MHz输出时钟;

c. SCLK_HDMI27M表示HDMI PHY (HDMI 27 MHz参考时钟)输出;

d. SCLK_HDMIPHY表示HDMI PHY (PIXEL_CLKO)输出时钟;

e. SCLKMPLL, SCLKEPLL和SCLKVPLL分别表示MPLL, EPLL和VPLL的输出时钟。

1.7 寄存器描述

系统控制器控制PLL,时钟发生器,电源管理单元(PMU),和其它系统独立单元。这部分讲述使用系统控制器内部的特殊功能寄存器(SFR)如何控制这些部分。别去修改任何保留区域。保留区域的值修改会导致未定义行为。

1.7.1 寄存器映射

寄存器映射表详见手册P367 ~ 370。

特殊功能寄存器有几个部分组成。

> 地址为0xE010_0XXX的SFR控制时钟相关逻辑。它们控制三个PLL的输出频率,时钟源选择,时钟分频比,和时钟门控;

> 地址为0xE010_2XXX的SFR控制软件复位;

> 地址为0xE010_3XXX的SFR控制IEM模块;

> 地址为0xE010_6XXX的SFR控制S5PV210系统;

> 地址为0xE010_7XXX的SFR包含杂项寄存器;

> 地址为0xE010_8XXX的SFR控制电源管理模块;

详细的寄存器描述参见手册的P371 ~ 416。

432

432

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?