来自 ARM Cortex-M3处理器体系结构.PPT

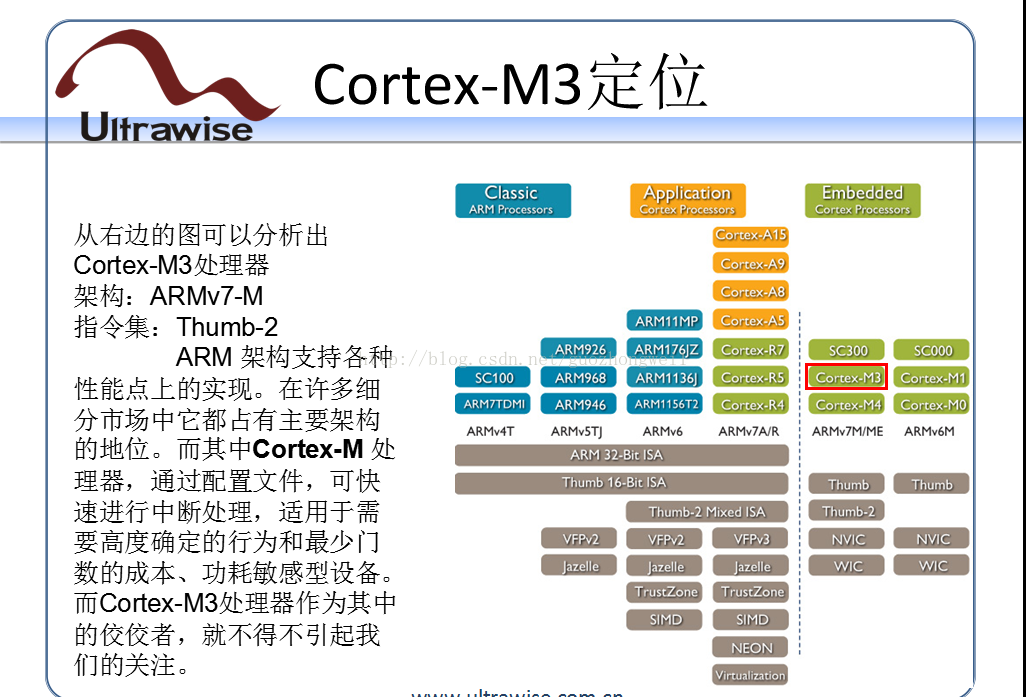

定位:

概况:

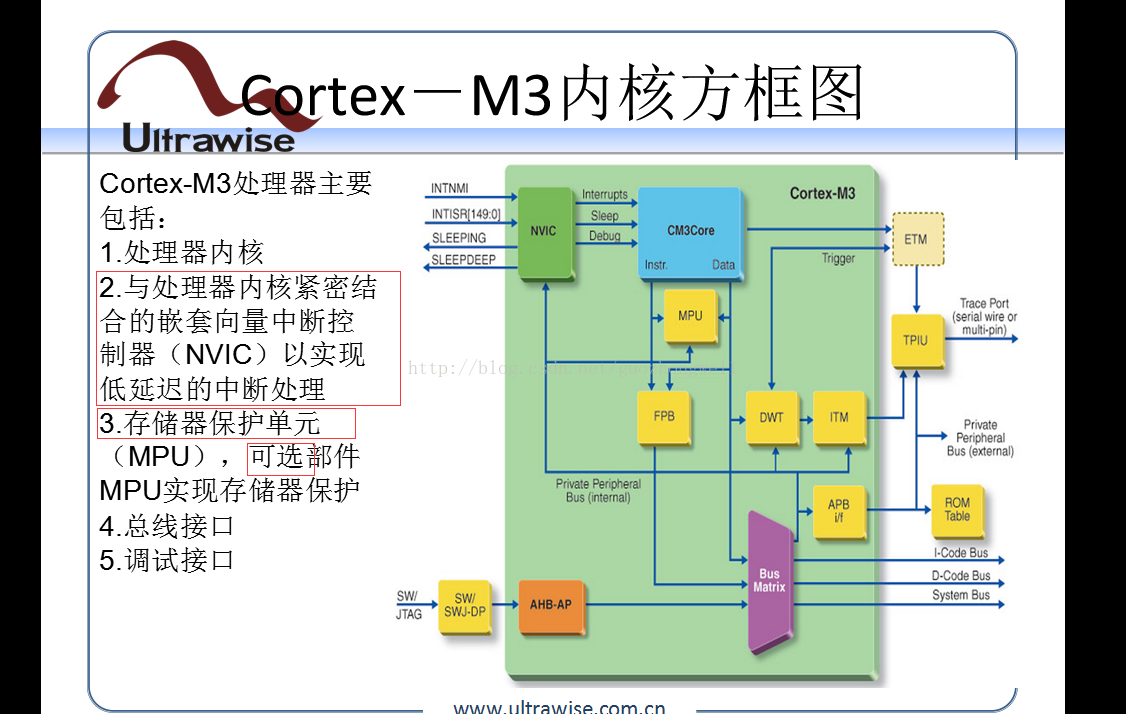

- Cortex-M3处理器内核

- Cortex-M3处理器指令集Thumb-2

- Cortex-M3嵌套向量中断控制器NVIC

- Cortex-M3存储器管理

- 存储器保护单元MPU

- 总线接口

- 调试跟踪接口

- 开发软件和RTOS

Cortex-M3内核:

内核流水线分3个阶段:

取指、译码和执行。当遇到

分支指令时,

译码阶段也包含预测的指令取指,这提高了执行的速度。处理器在译码阶段期间自行对分支目的地指令进行取指。在稍后的执行过程中,处理完分支指令后便知道下一条要执行的指令。如果分支不跳转,那么紧跟着的下一条指令随时可供使用。如果分支跳转,那么在跳转的同时分支指令可供使用,空闲时间限制为一个周期。

Cortex-M3 处理器是一个 32 位处理器,带有 32 位宽的数据路径,寄存器库和存储器接口。其中有 13 个通用寄存器,两个堆栈指针,一个链接寄存器,一个程序计数器和一系列包含编程状态寄存器的特殊寄存器。

Cortex-M3 处理器支持两种工作模式(线程(Thread)和处理器(Handler))和两个等级的访问形式(有特权或无特权),在不牺牲应用程序安全的前提下实现了对复杂的开放式系统的执行。

Cortex-M3 处理器是一个 32 位处理器,带有 32 位宽的数据路径,寄存器库和存储器接口。其中有 13 个通用寄存器,两个堆栈指针,一个链接寄存器,一个程序计数器和一系列包含编程状态寄存器的特殊寄存器。

Cortex-M3 处理器支持两种工作模式(线程(Thread)和处理器(Handler))和两个等级的访问形式(有特权或无特权),在不牺牲应用程序安全的前提下实现了对复杂的开放式系统的执行。

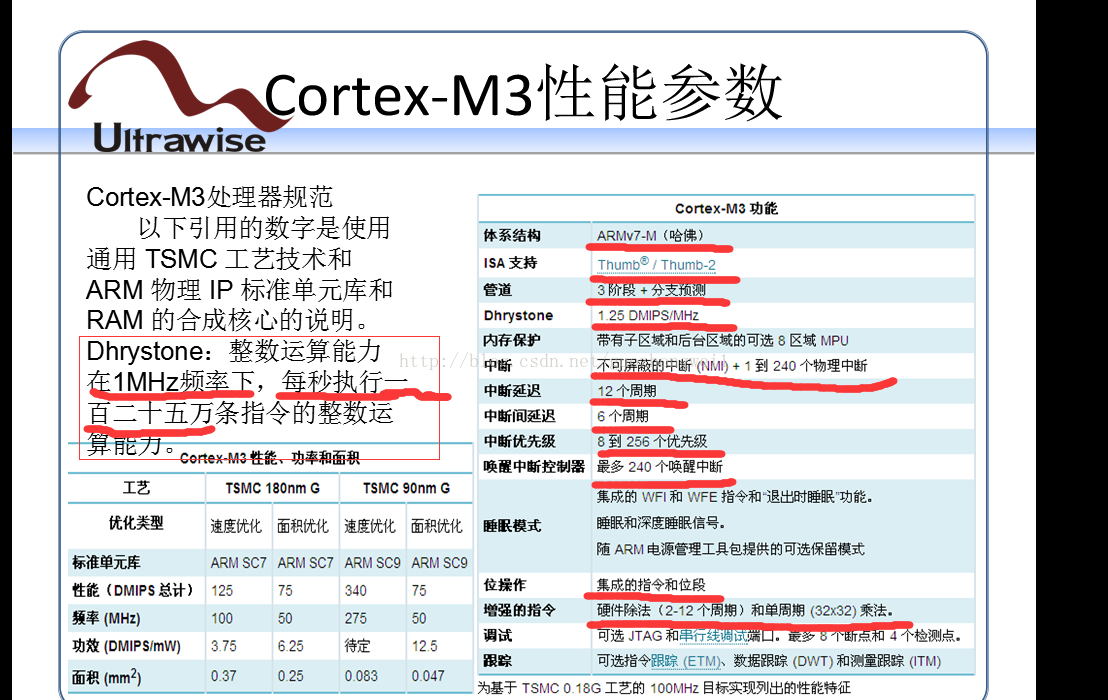

性能参数:

Cortex-M3处理器指令集Thumb-2:

好处:

- 可以实现ARM指令的所有功能。

- 增加了12条新指令,可以改进代码性能和代码密度之间的平衡。

- 代码性能达到了纯ARM代码性能的98%。

- 相对ARM代码,Thumb-2代码的大小仅有其74%

- 代码密度比现有的Thumb指令集更高。(代码大小平均降低5%;代码速度平均提高2-3%。)

注:Cortex-M3不支持ARM指令集。

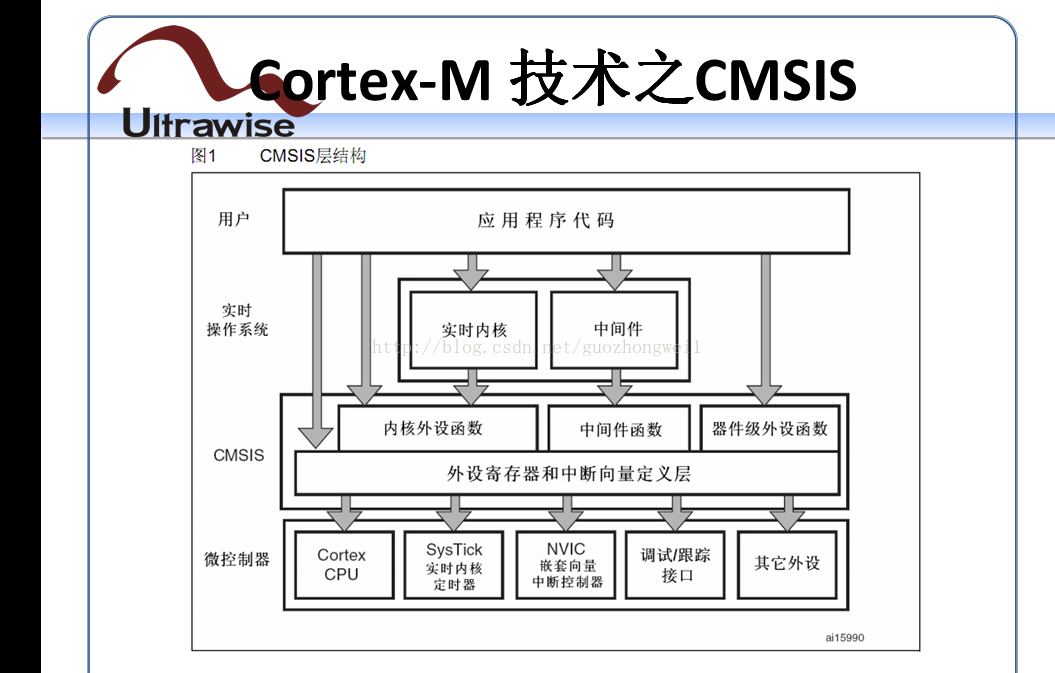

Cortex-M 技术之CMSIS:

Cortex-M 技术之NVIC:

- NVIC 为处理器提供了卓越的中断处理能力。

- Cortex-M 处理器使用一个矢量表,其中包含要为特定中断处理程序执行的函数的地址。接受中断时,处理器会从该矢量表中提取地址。为了减少门数并增强系统灵活性,Cortex-M 处理器使用一个基于堆栈的异常模型。出现异常时,系统会将关键通用寄存器推送到堆栈上。完成入栈和指令提取后,将执行中断服务例程或故障处理程序,然后自动还原寄存器以使中断的程序恢复正常执行。使用此方法,便无需编写汇编器包装器了(而这是对基于 C 语言的传统中断服务例程执行堆栈操作所必需的),从而使得应用程序的开发变得非常容易。 NVIC 支持中断嵌套(入栈),从而允许通过运用较高的优先级来较早地为某个中断提供服务。

- 在硬件中完成对中断的响应

Cortex-M 系列处理器的中断响应是从发出中断信号到执行中断服务例程的周期数。它包括:

1、检测中断

2、背对背或迟到中断的最佳处理

3、提取矢量地址

4、将易损坏的寄存器入栈

5、跳转到中断处理程序

---这些任务在硬件中执行,并且包含在为 Cortex-M 处理器报出的中断响应周期时间中。在其他许多体系结构中,这些任务必须在软件的中断处理程序中执行,从而引起延迟并使得过程十分复杂

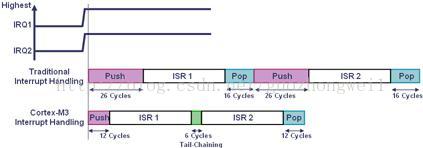

- NVIC 中的尾链

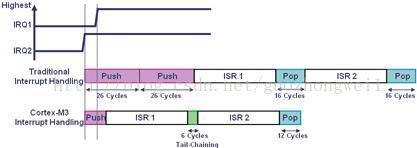

在背对背中断的情况下,传统系统会重复完整的状态保存和还原周期两次,从而导致更高的延迟。Cortex-M 处理器通过在 NVIC 硬件中实现尾链技术简化了活动中断和挂起的中断之间的转换。处理器状态会在比软件实现时间更少的周期内自动保存在中断条目上并在中断退出时还原,从而显著提升低 MHz 系统的性能。 - NVIC 对迟到的较高优先级中断的响应

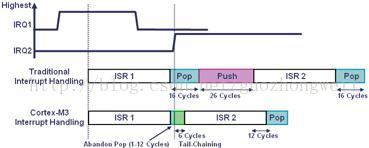

如果在为上一个中断执行堆栈推送期间较高优先级的中断迟到,NVIC 会立即提取新的矢量地址来为挂起的中断提供服务,如上所示。Cortex-M NVIC 对这些可能性提供具有确定性的响应并支持迟到和抢占。 - NVIC 进行的堆栈弹出抢占

同样,如果异常到达,NVIC 将放弃堆栈弹出并立即为新的中断提供服务,如上所示。通过抢占并切换到第二个中断而不完成状态还原和保存,NVIC 以具有确定性的方式实现了缩短延迟。

其他,略过......

........................................

.....................................

可以到我的网盘下载资料--

Cortex-M3处理器体系结构.PPT

4409

4409

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?