经过了一段时间的Android下wm8960驱动的调试,终于实现录音和播放功能了,在调试过程中有了一些心得,与大家分享一

下,由于能力有限,错误之处还望海涵和指教。

一、总述

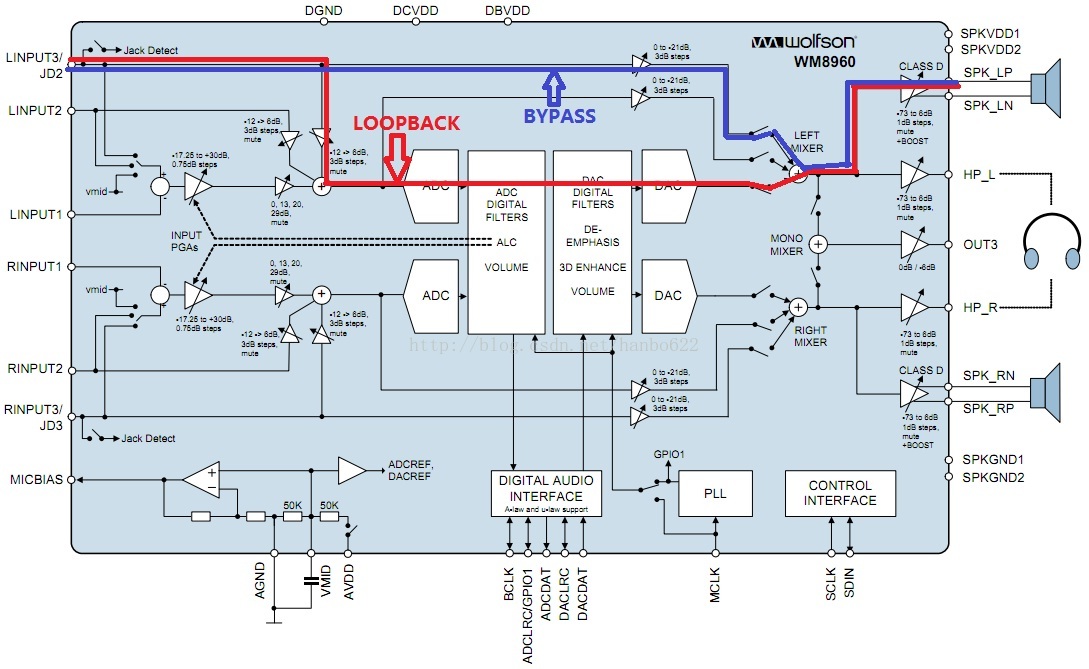

wm8960芯片的使用其实就是对该芯片寄存器的设置,要实现的每个功能在芯片内部都是每一个通道,也就是数据从输入端

流进沿着你设置的通道从输出端流出,如下图的芯片内部图和通道事例。

二、PLL功能介绍

wm8960支持使用DSP时钟和PLL功能,PLL可以更灵活的得到在芯片内部所需要的时钟,所以为了不改DSP的时钟频率,

一般采用PLL功能。采用PLL功能后Codec要为主模式,设置寄存器是R07的bit6(MS)置1。

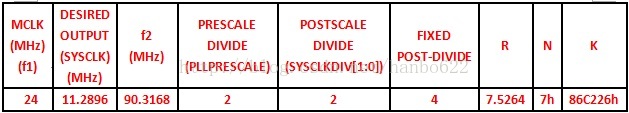

PLL的频率是通过寄存器位PLLN和PLLK进行设置的,计算关系和芯片内部PLL图如下:

f2=4×2×11.2896MHz的=90.3168MHz

R = 90.3168 / 12 = 7.5264

PLLN = int R = 7

K = int ( 2^24 x (7.5264 – 7)) = 8831526 = 86C226h

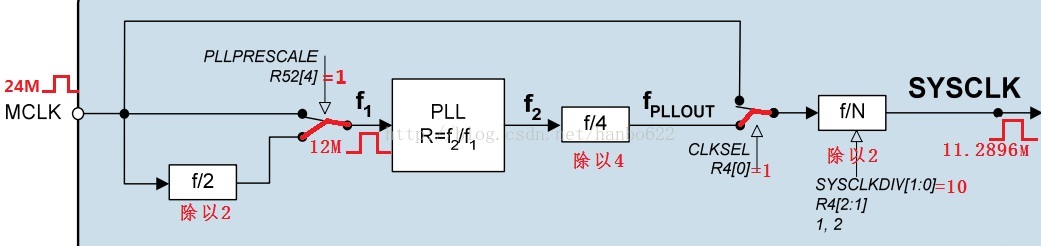

通过上述分析计算可以设置PLL功能的输出频率为11.2896MHz,实现如下:

R26的bit0(DACL)置1:给PLL功能使能;

R52的bit4(PLLPRESCALE)置1:预分频,如果MCLK=12M就不用设置该位了;

R52的bit[3:0](PLLN)置0111:设置PLLN的值;

R52的bit5(SDM)置1:选择为小数模式;

R53的bit[8:0](PLLK)置01000 0110:设置PLLK的值;

R54的bit[8:0](PLLK)置01100 0010:设置PLLK的值;

R55的bit[8:0](PLLK)置00010 0110:设置PLLK的值;

R04的bit[0](CLKSEL)置1:选择PLL输出的时钟(置0表示选择MCLK时钟);

R04的bit[2:1](SYSCLKDIV)置10:分频(除以2)。

这里说一下,如果DSP输出是11.2896MHz可以直接使用,就不用设置PLL了。为什要输11.2896MHz在《I2S音频通信》

已经介绍了。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?