1.一个工程所在的文件夹,从开始路径到最终路径都要以英文命名,否则会编译出错;

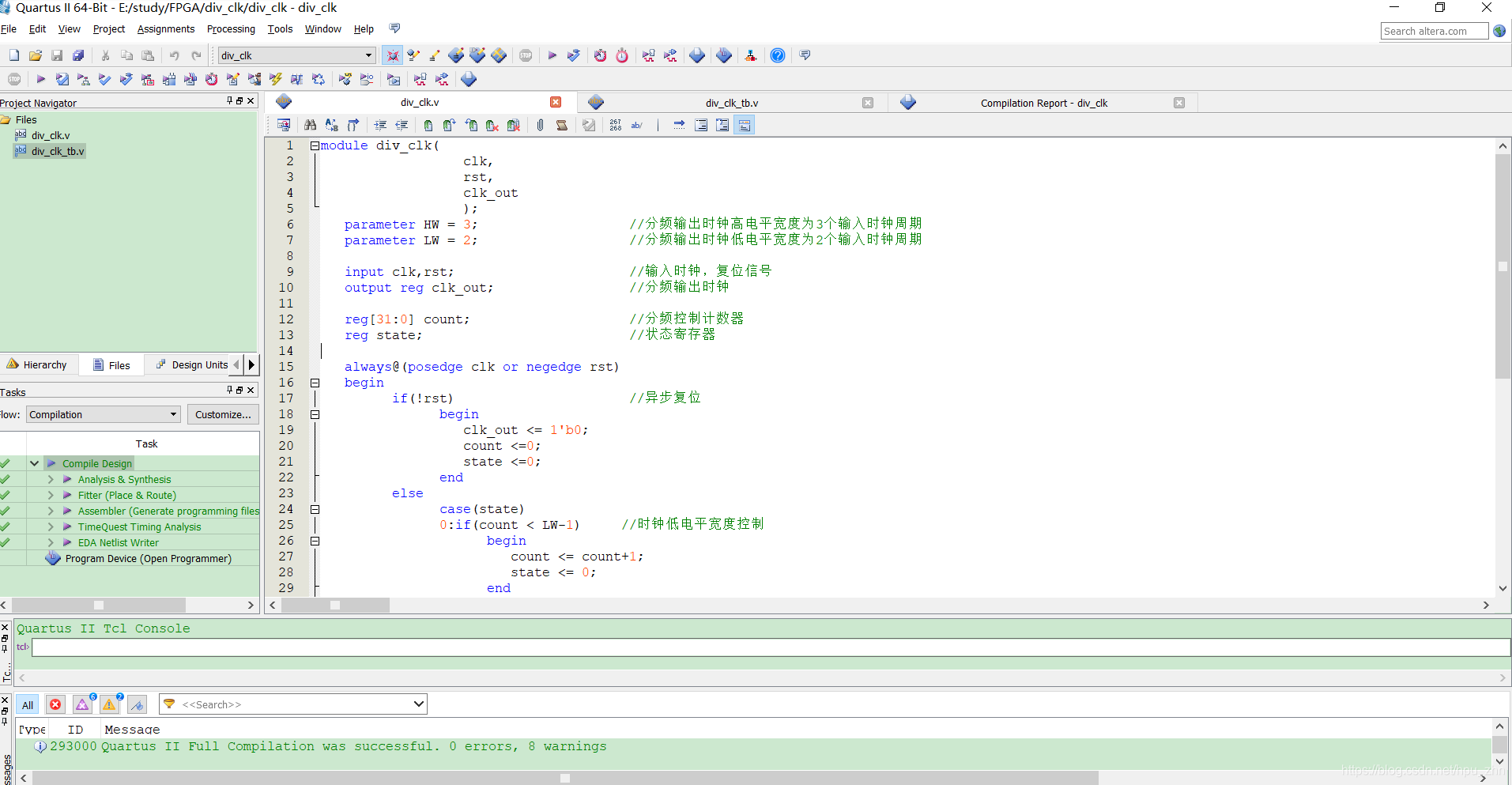

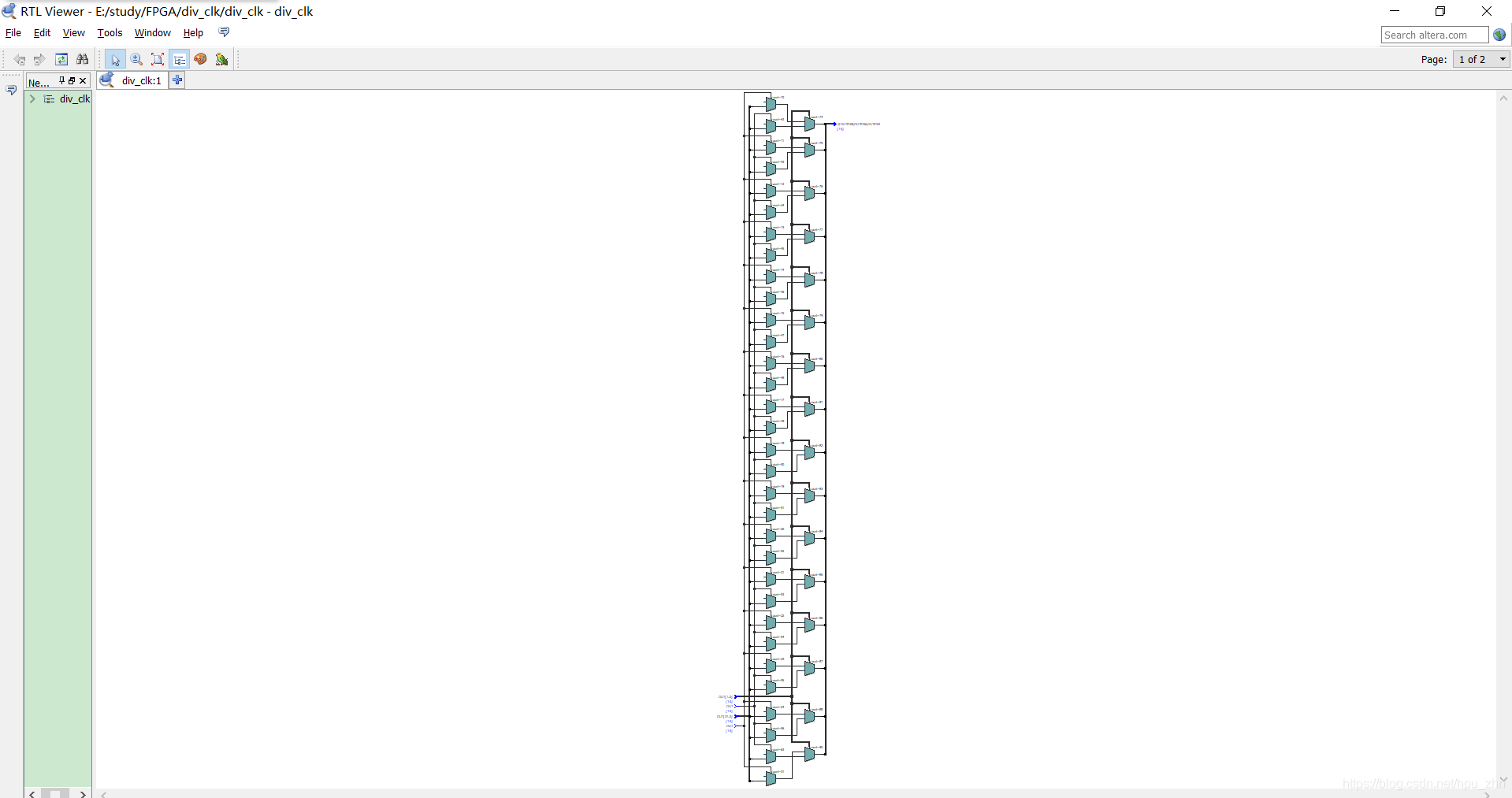

2.如何在Quartus中查看用硬件描述语言生成的模块图? 具体操作为:Tools > Netlist Viewers > RTL Viewer;这便是硬件描述语言的精妙之处:用语言来描述硬件,甚至生成硬件;(这里我们举一个分频器的例子)

代码如下:(粘贴过来供大家参考),生成的模块图如下所示:

module div_clk(

clk,

rst,

clk_out

);

parameter HW = 3; //分频输出时钟高电平宽度为3个输入时钟周期

parameter LW = 2; //分频输出时钟低电平宽度为2个输入时钟周期

input clk,rst; //输入时钟,复位信号

output reg clk_out; //分频输出时钟

reg[31:0] count; //分频控制计数器

reg state; //状态寄存器

always@(posedge clk or negedge rst)

begin

if(!rst) //异步复位

begin

clk_out <= 1'b0;

count <=0;

state <=0;

end

else

case(state)

0:if(count < LW-1) //时钟低电平宽度控制

begin

count <= count+1;

state <= 0;

end

else

begin //当计数值等于LW时状态转移,同时输出反转

count <= 0;

clk_out <= 1;

state <= 1;

end

1:if(count < HW-1) //时钟高电平宽度控制

begin

count <= count+1;

state <= 1;

end

else

begin //当计数值等于HW时状态转移,同时输出反转

count <= 0;

clk_out <= 0;

state <= 0;

end

default:state <= 0;

endcase

end

endmodule

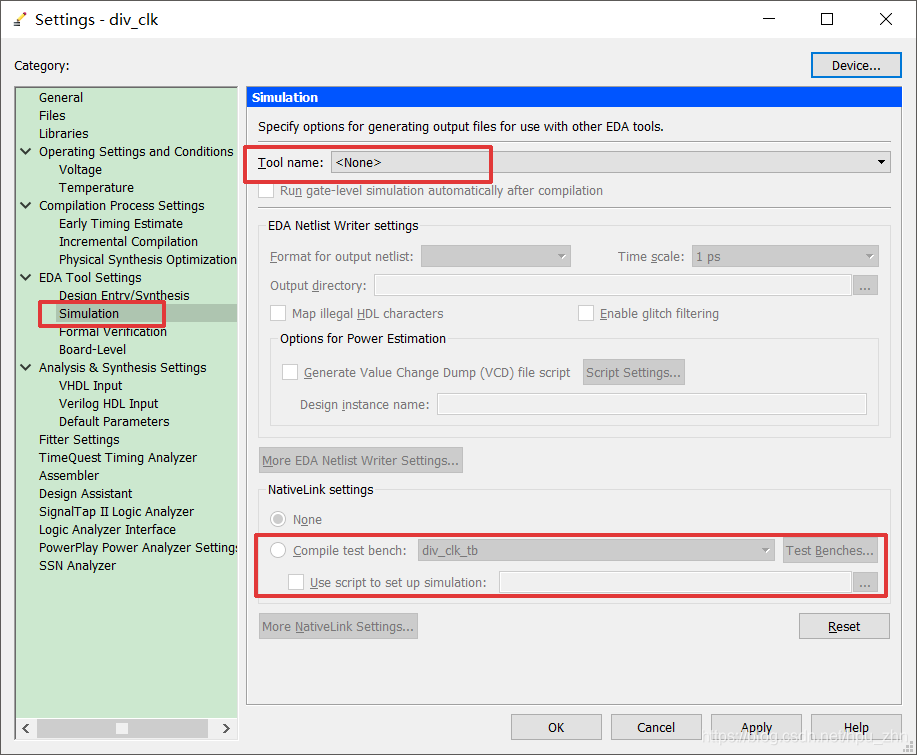

3.代码编译通过,测试代码写完后,如何自动仿真? 具体操作有些麻烦,这里我们用图示的形式:(确定测试代码是xx_tb)

①.Assignments > Settings >

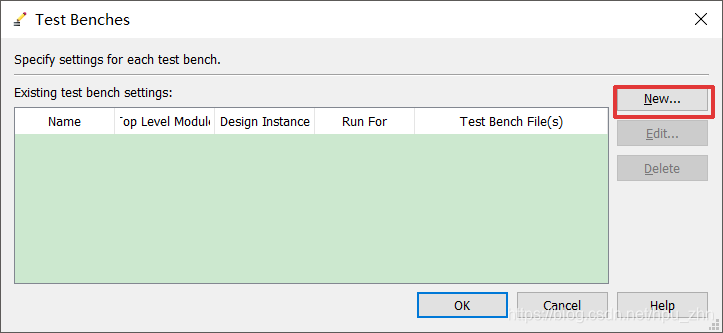

②.开始进去是这样的:(注意画框的地方)

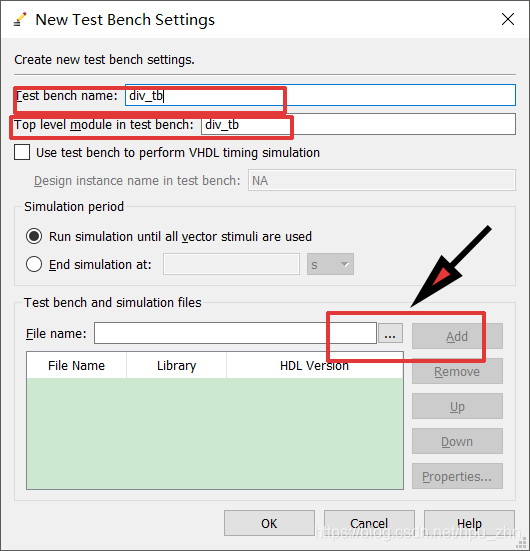

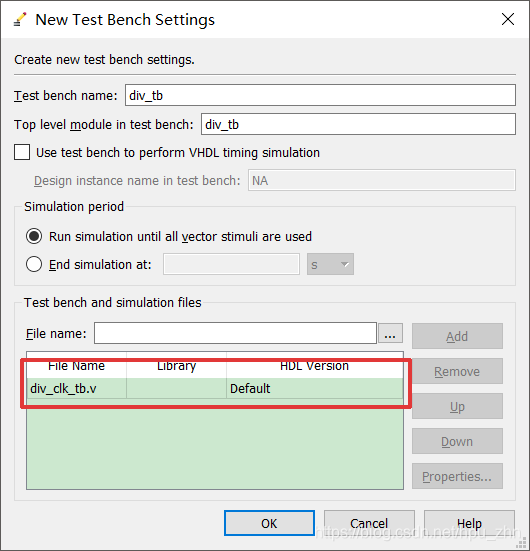

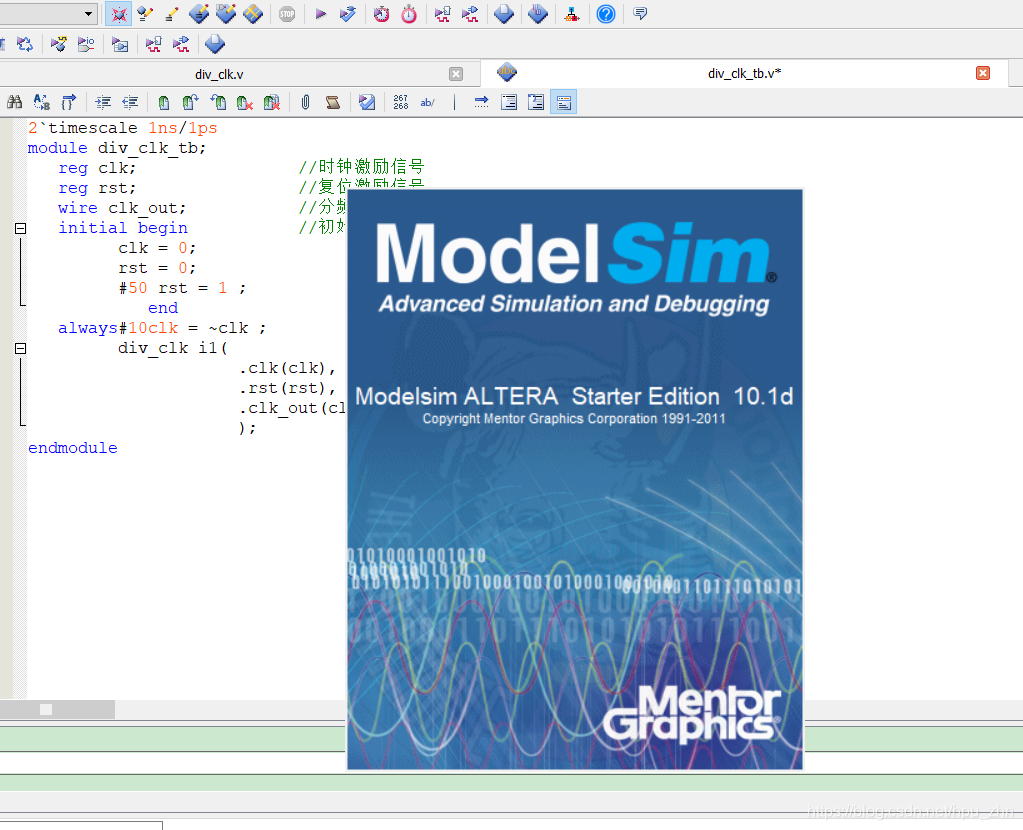

③.Simulation > 之后前两处对应修改,在NativeLink setting 中选择Coplile test bench > Test Benches…>New > 对应下图填写 (具体的测试文件,一定要是xx_tb,tb结尾),>> 点击 箭头执行的添加测试文件进来;>>注意最后点add;完成页面如下图所示:紧接着一路ok;

④.Tools > Run Simulation Tools > RTL Simulation ,即可实现自动调用Modelsim 仿真。

4.占空比如何理解? 占空比的定义:在一段连续工作时间内脉冲占用的时间与总时间的比值;也就是指在一个脉冲循环内,通电时间相对于总时间所占的比例。占空比(Duty RaTIo)在电信领域中有如下含义:例如:脉冲宽度1μs,信号周期4μs的脉冲序列占空比为0.25。

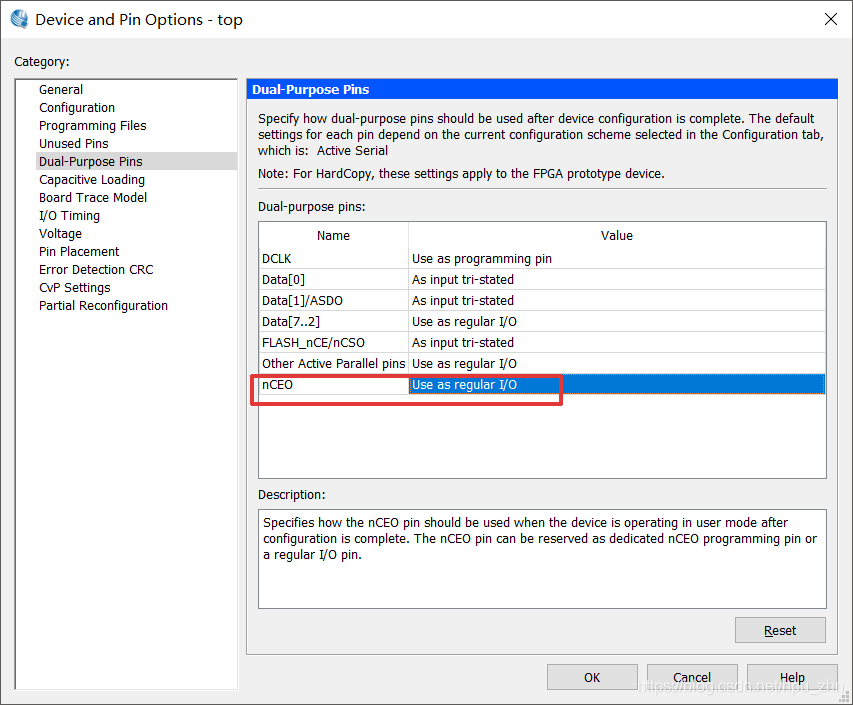

5.做VGA实验,分配完管脚后全编译出现以下错误:

{Error (176310): Can’t place multiple pins assigned to pin location Pin_101 (IOPAD_X34_Y18_N21)

Info (176311): Pin vga_b[0] is assigned to pin location Pin_101 (IOPAD_X34_Y18_N21)

Info (176311): Pin ALTERA_nCEO is assigned to pin location Pin_101 (IOPAD_X34_Y18_N21)}

出现这样错误的原因是:由于Pin_101是一个多功能管脚,还有一个功能是nCEO,也是默认的功能。如果要用它作普通I/O口,需要提前设置以下;具体解决方法为:assignments>device>device and pin options>dual-purpose pins里面把nCEO设置成use as regular i/o就可以了。

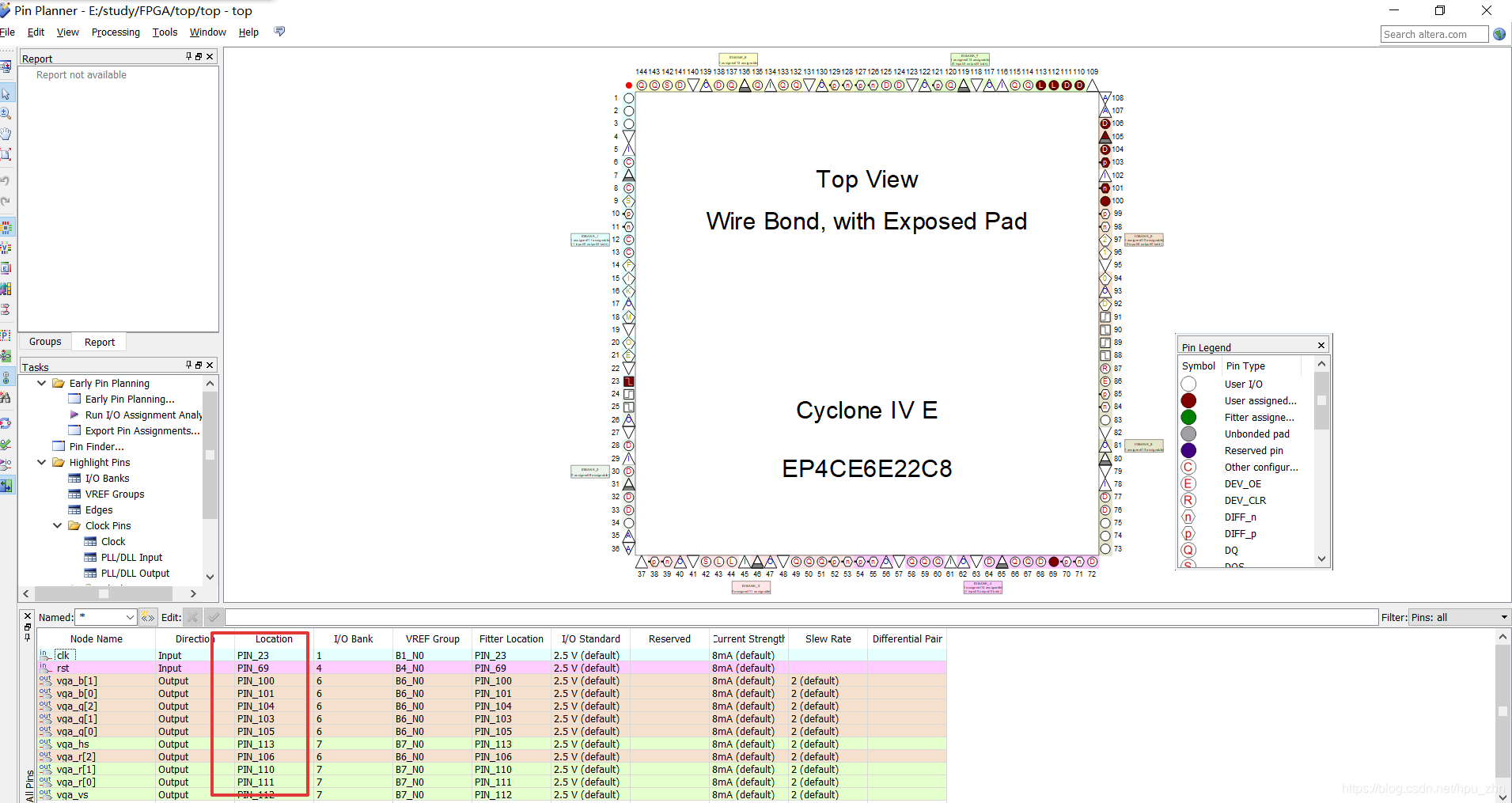

6.编译完成后,如何分配管脚?具体操作为:Assignments>Pin Planner,之后进去下图页面

画框的地方也就是Location这一列,就是我们要分配管脚的地方,具体的板子对应的I/O口引脚我们可以查看板子的脚本文件获得,对应填入即可,完成之后,重新全编译,具体的下载固化流程详见上篇文章FPGA之固化程序(注意在分配管脚之前,一定要选正确芯片的型号!)

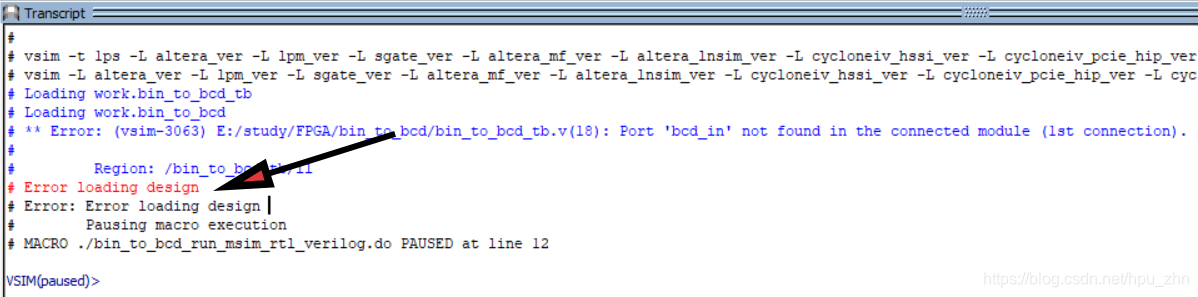

7.调用Modelsim,出现error loading design错误,明明每一个设计文件都编译通过,就是无法仿真,出不来波形,很是愁人。好在经过一番摸索,找到了解决办法,出现这种错误我们可以从以下几个方面去找错误:

1.检查文件是否未被包含且未加入工程。

2.检查设计文件的端口声明与实例化时的端口是否一致。

3.检查设计文件的模块名是否与实例化时的模块名一致。

4.检查未在顶层文件中修改的端口是否为wire

2051

2051

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?