工作电压2-6V,推荐5V。

14脚串行输入:595的数据来源只有这一个口,一次只能输入一个位,那么连续输入8次,就可以积攒为一个字节了。

13脚OE 输出使能控制脚:如果它不工作,那么595的输出就是高阻态,595就不受我们程序控制了,这显然违背我们的意愿。OE的上面画了一条线,表示他是低电平有效。于是我们将他接GND。

10脚SRCLR 位移寄存器清空脚:他的作用就是将位移寄存器中的数据全部清空,这个很少用到,所以我们一般不让他起作用,也是低电平有效,于是我们给他接VCC。

12脚RCLK存储寄存器:数据从位移寄存器转移到存储寄存器,也是需要时钟脉冲驱动的,这就是12脚的作用。它也是上升沿有效。

分析下数据输入和输出过程:

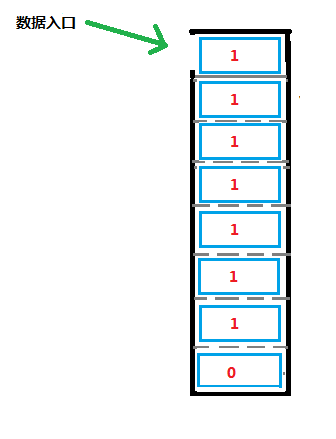

假如,我们要将二进制数据0111 1111 输入到595的移位寄存器中,下面来上一张动态图,模拟了前2个位输入的情景。 第一个从SER送入的bit将会从Q7出去。

数据传输完毕后是这样的。

存储寄存器:

存储寄存器是直接和8个输出引脚相通的,将移位寄存器的数据转移到存储寄存器后,Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 就可以接受带到我们开始输入的一个字节的数据。所谓存储寄存器,就是数据可以存在这个寄存器中,并不会随着一次输出就消失,只要595不断电,也没有新的数据从移位寄存器中过来,数据就一直不变且有效。新的数据过来后,存储寄存器中的数据就会被覆盖更新。

在上面的程序中没用到9脚,如果要让2个595串联起来的话,就需要它了。

想一下,我们将移位寄存器的8个位填满后,再往移位寄存器中塞一个会怎么样?也许你想到了。

对!移位寄存器的最后一个位数据会被挤出去,从哪里出去?就是从9脚输出的(第一个595移位寄存器需要8个脉冲,级联的下一个595第一位Q0实际需要第9个脉冲...以此类推)。如果我们把第一个595的

9脚连接到第二个的串行数据输入脚SER,那么,就形成了595的级联。这样,如果我们用2个595组合成了一个新的超级595,

4008

4008

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?