对于高速设计,我们通常关注两个方面。第一个是信号完整性 (SI),以及与走线间距引起的串扰、阻抗不匹配引起的反射、信号衰减以及振铃等问题相关的问题。当然,我们希望尽最大努力将这些问题最小化。其次,我们关注电磁干扰 (EMI)。

什么是“高速”PCB设计?

在我们了解这些 高速PCB设计和布局技巧之前,让我们先来看看什么时候我们真正需要关心所有这些!

举例来说,假设我们的设计中有一个 100 MHz 的时钟信号,并天真地认为这是我们系统中最高的频率。结果发现,问题实际上不是时钟信号的基频为 100 MHz,而是我们的设计问题来自这个近方波时钟信号的上升和下降时间。

这些从数字低到数字高(或反之亦然)的急剧转变包含远高于基频的频率内容。给定信号的上升和下降时间(取决于其中哪个更快),我们可以使用以下公式大致计算信号内的最大频率(或带宽):

例如,对于具有 1 ns 上升时间的 100 MHz 时钟信号,该信号的带宽为 500 MHz — 差异相当大!

当 PCB 走线长度超过电介质波长的 1/12 时,我们需要开始更详细地考虑 PCB 设计。此时我们的走线开始看起来像分布式长度传输线,而不再像集总元件。我们将这个长度称为“临界长度”。

提示1:参考平面

我们总是希望在信号平面旁边有一个接地平面或相关电源平面,直接位于带有走线的层的下面(或上面)。在某些情况下,您可以使用相关电源平面而不是接地平面作为参考。这里的相关是指参考平面电压与信号来源的电压相同。参考平面不仅对于保持正确的返回路径和最大限度地减少电磁场扩散很重要,而且在需要受控阻抗走线时也很重要。

对于交流信号,任何高于几 kHz 的信号,返回路径实际上都位于参考平面下方信号迹线的正下方。一个非常重要的规则是,迹线下方的参考平面不应有裂缝。

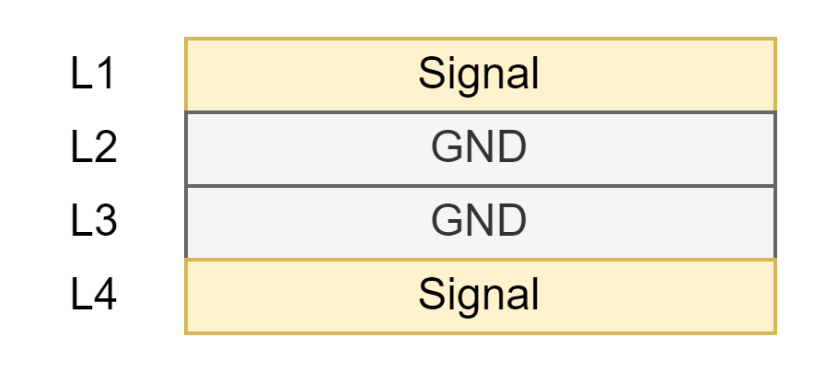

技巧#2:电路板堆叠

我们希望接地平面不仅与信号平面相邻,还与电源平面相邻。在平面之间使用薄电介质也是一个好主意,这反过来又能提供紧密耦合,并允许我们使用更细的走线来实现更密集的设计。

更细的走线还能给我们提供更多的工作空间,以及更多的走线间距。但是,请记住,制造细走线可能会更加困难。

技巧 3:受控阻抗走线

一旦我们的走线长度超过本文介绍中讨论的临界长度,我们就需要控制走线的阻抗。也就是说,我们需要根据所选的 PCB 叠层和结构调整走线的宽度,以提供一定的传输线阻抗。通常,对于单端信号,该阻抗为 50 欧姆。Altium Designer 具有强大的 2D 场解算器,可以根据您的叠层和结构在几秒钟内为您计算所需的走线宽度!

提示#4:走线长度、间距和3h规则

我们需要让高速走线尽可能短——这有助于降低 EMI 和 SI。此外,我们希望让不同的高速走线尽可能彼此远离,以最大限度地减少串扰。

此外,应尽量使高速走线远离电感器或电路电源部分等元件。一个典型的经验法则是3h 规则,这意味着走线之间的距离应至少为信号层和下一个接地层或参考层之间电介质高度的三倍。

对于高性能、高速设计,我们通常需要模拟工具来验证我们是否满足所需的信号完整性和 EMI 性能。

446

446

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?