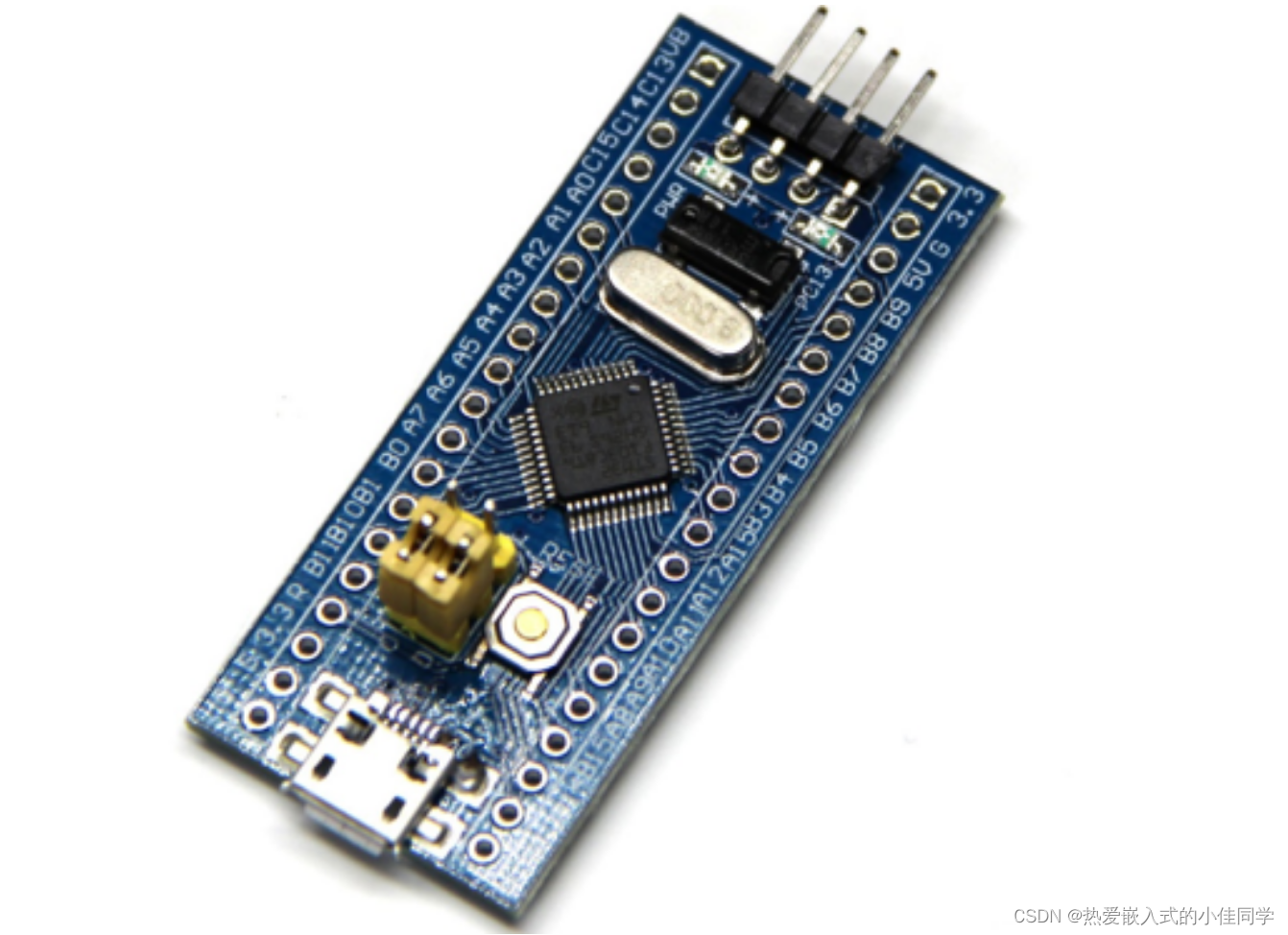

1 何为最小系统?

最小系统板就是一个最精简的电路,精简到只能维持MCU最基本的正常工作

2 最小系统电路设计

2.1 电源

2.1.1 各种名词解释

| VCC | 电路的供电正电压 | VDDD | 芯片的工作数字正电压 |

|---|---|---|---|

| GND | 电路的供电负电压 | VSSD | 芯片的工作数字负电压 |

| VDD | 芯片的工作正电压 | VREF+ | ADC基准参考正电压 |

| VSS | 芯片的工作负电压 | VREF- | ADC基准参考负电压 |

| VDDA | 芯片的工作模拟正电压 | VBAT | 电池或其他电源供电 |

| VSSA | 芯片的工作模拟负电压 | VEE | 负电压供电 |

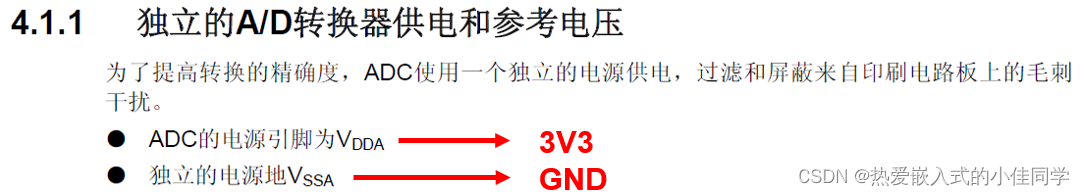

VDDA,VSSA:

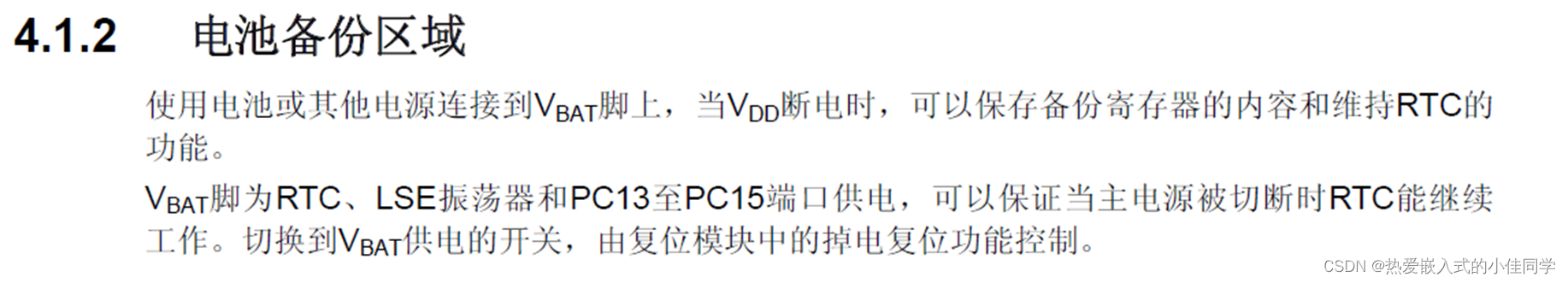

VBAT:(RTC为实时时钟,LSE为低速外部时钟)

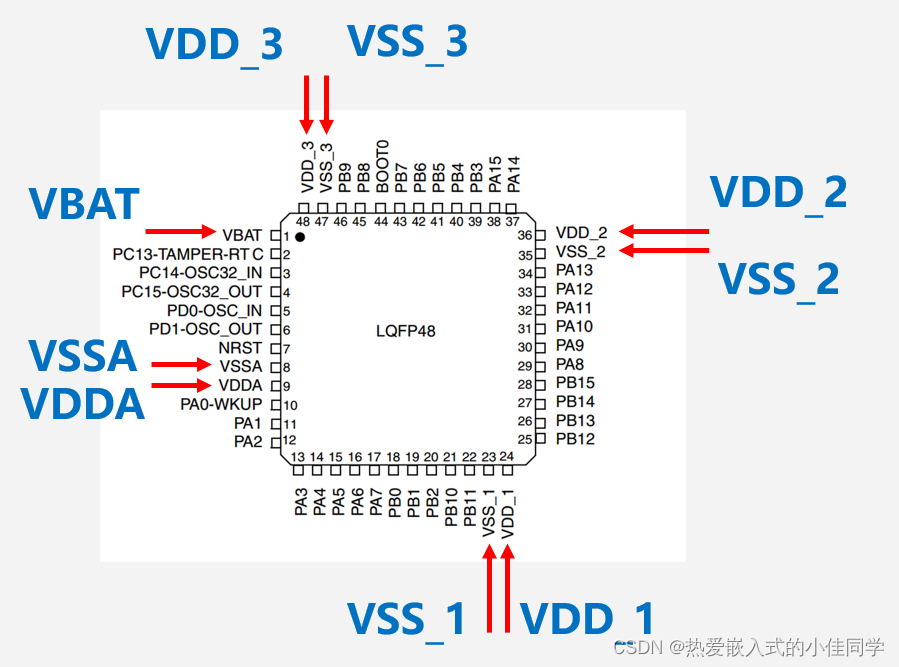

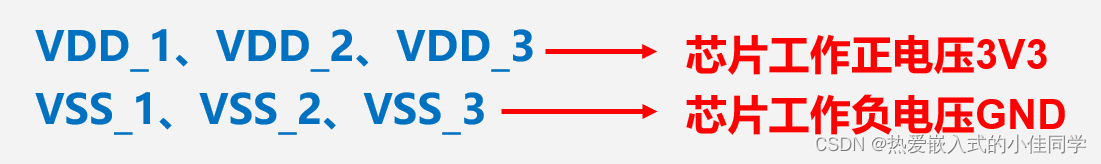

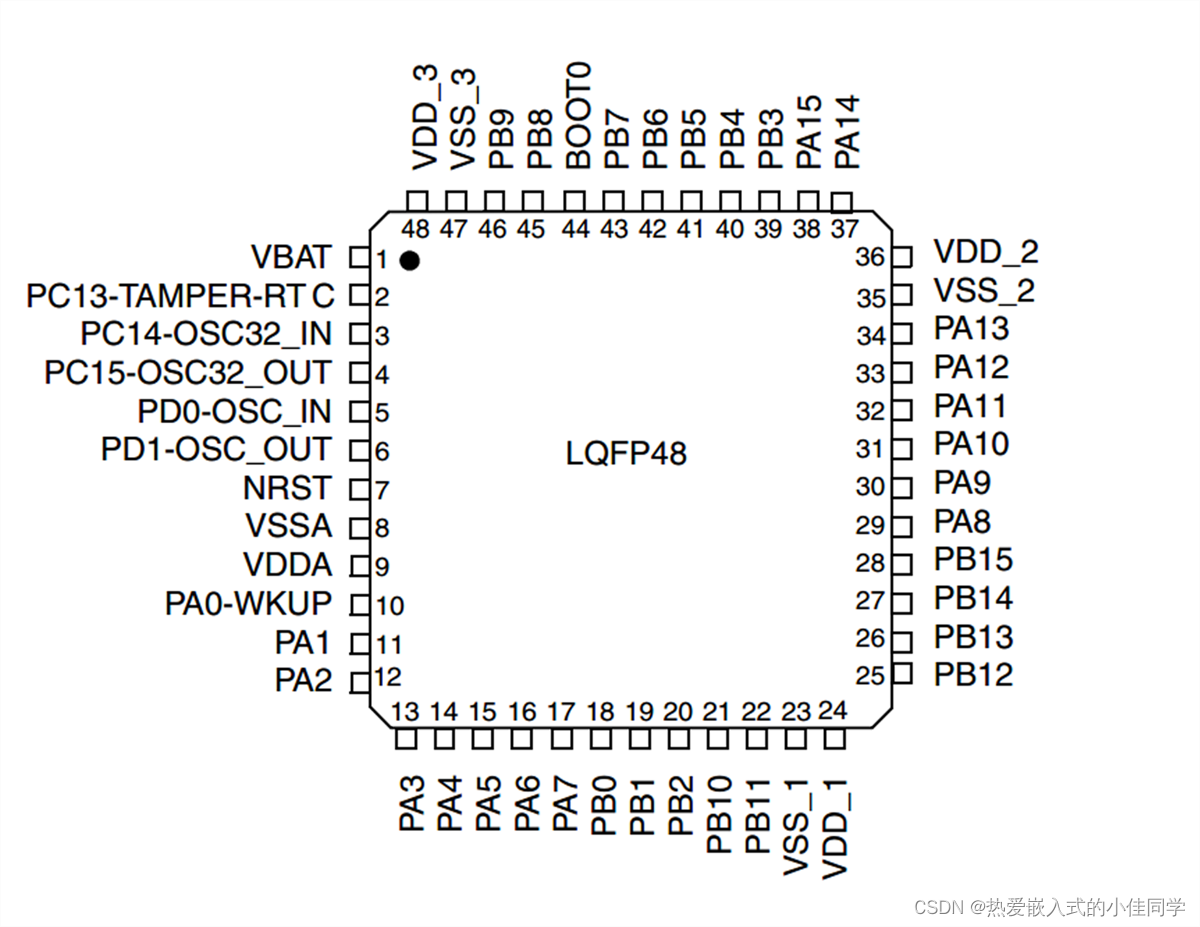

2.1.2 为什么会有VDD_1 _2 _3区分?

因为VDD和VSS在芯片内部都是连在一起的,封装的时候从不同的地方分别引出,目的是为了提供可靠的电源完整性。

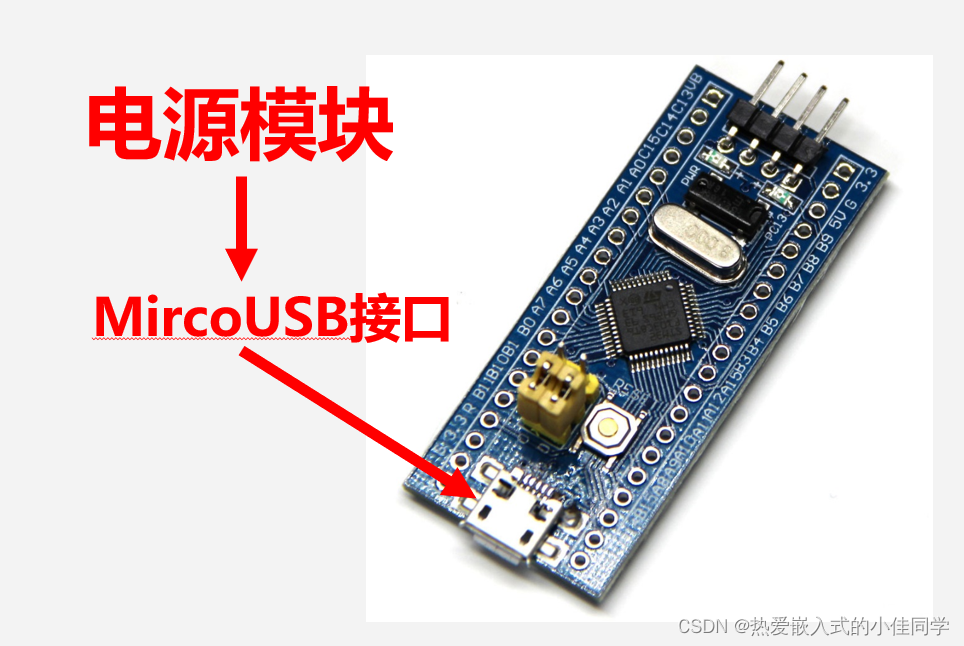

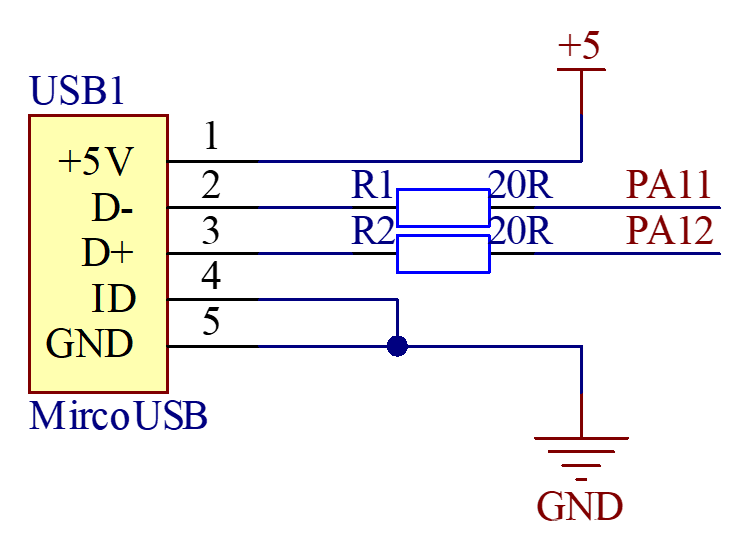

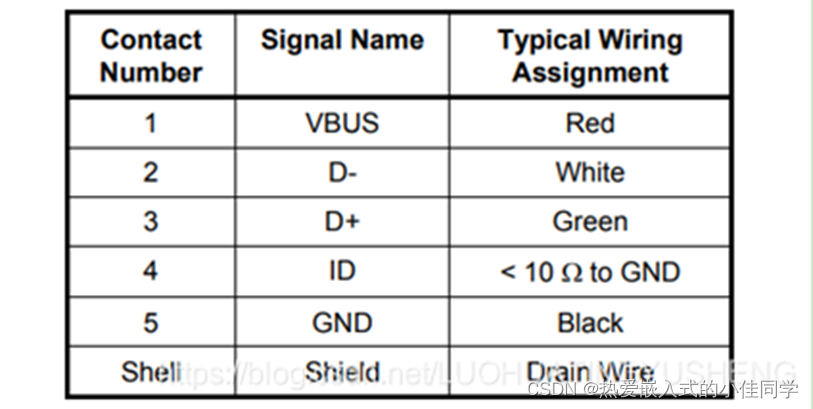

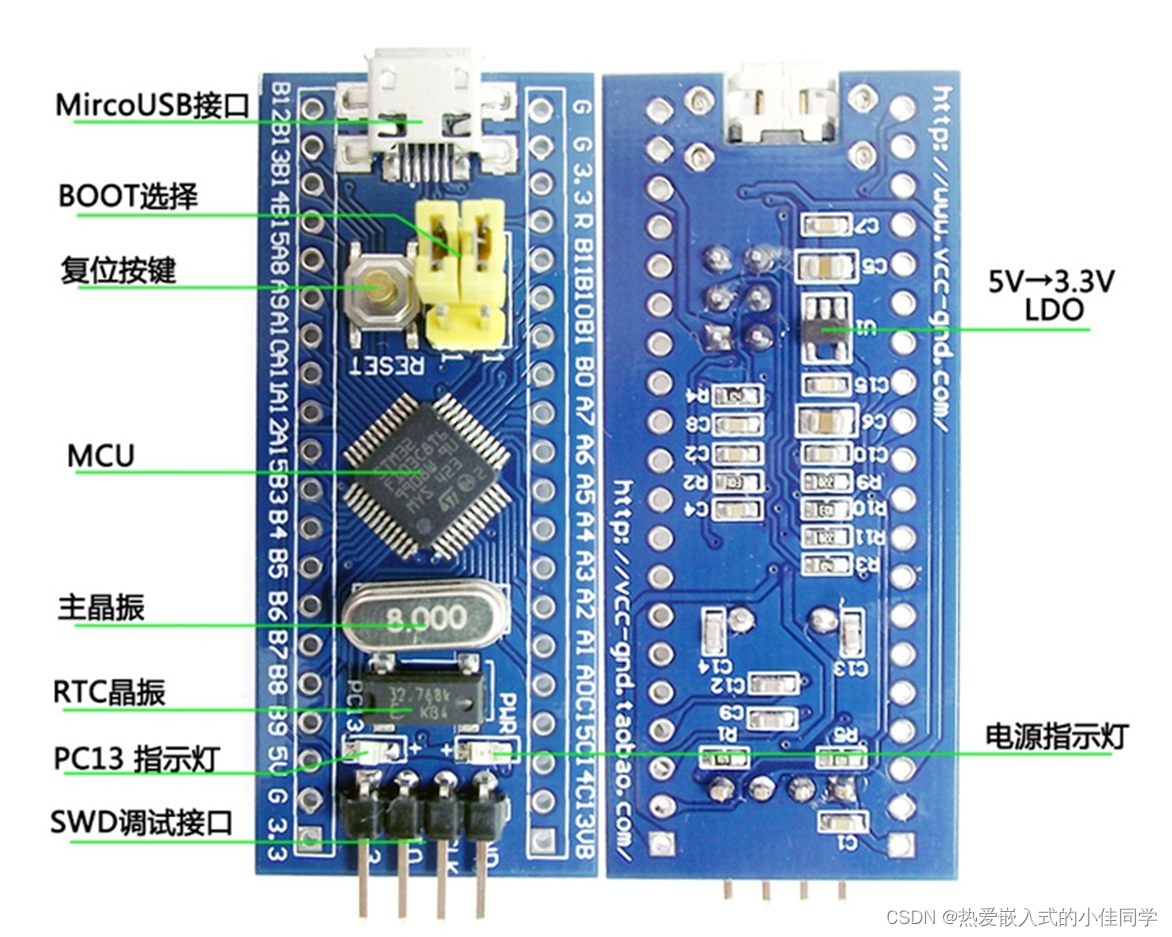

2.1.3 Mirco USB

- 1)Vbus:电源引脚。

- 2)D+:数据线+。

- 3)D-: 数据线-。

- 4)ID脚:Identification,检测的意思。ID线—以用于识别不同的电缆端点,mini-A插头(即A外设)中的ID引脚接地,mini-B插头(即B外设)中的ID引脚浮空。

- 5)GND:接地

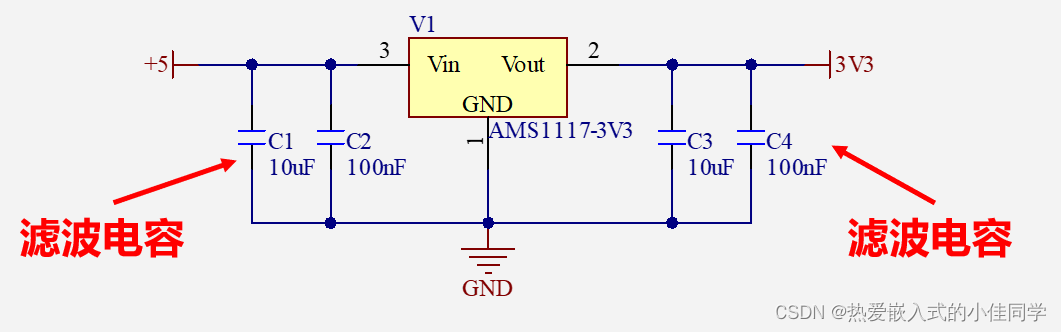

2.1.4 5v->3.3v滤波电路

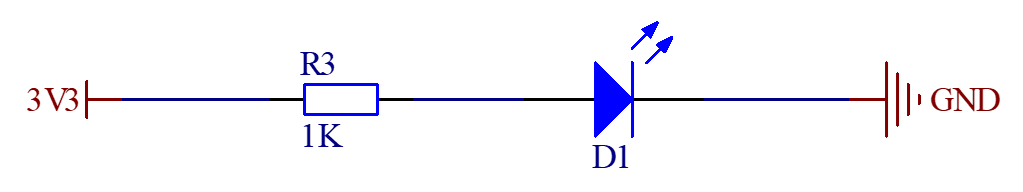

2.1.5 电源指示灯

电路:

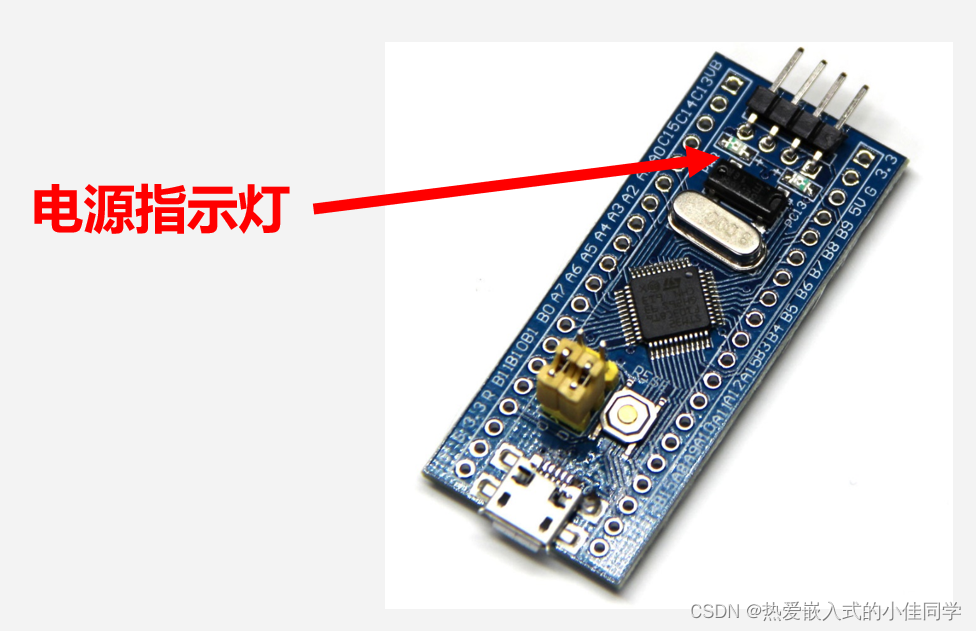

示例图:

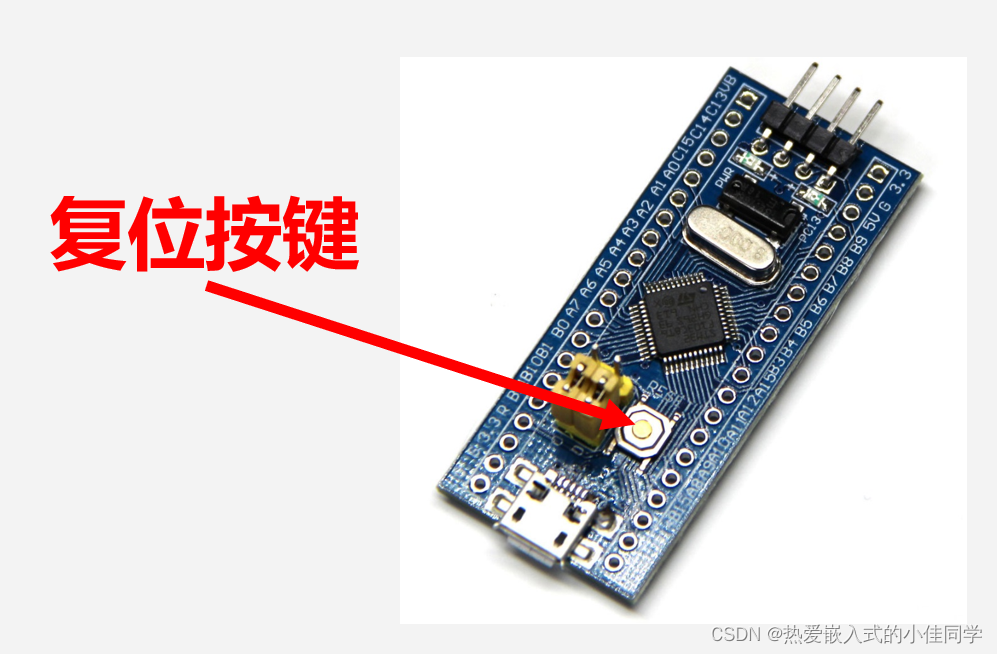

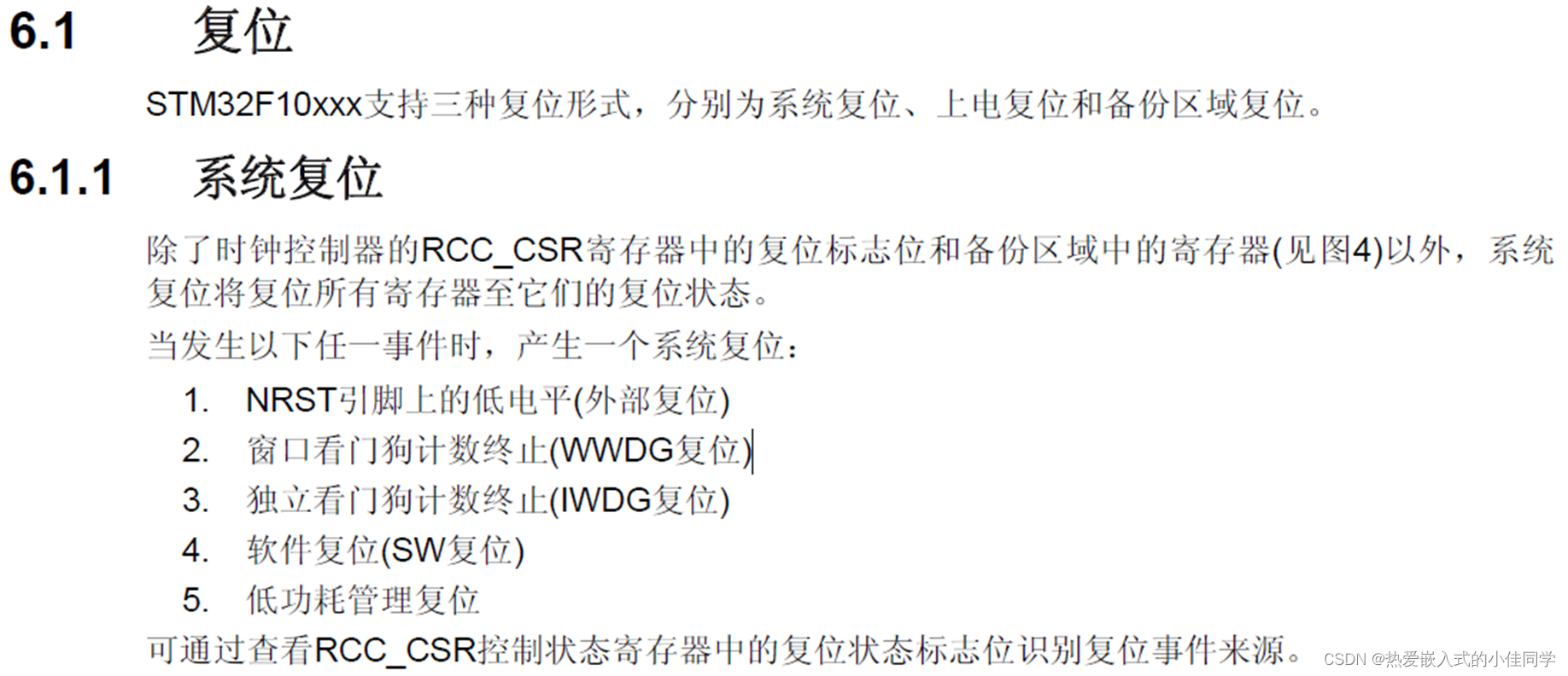

2.2 复位电路

2.2.1 什么是复位

就是让单片机程序复位,把除了备份区域寄存器以外所有寄存器状态恢复至原始状态,简单来说就是让程序重头开始跑。

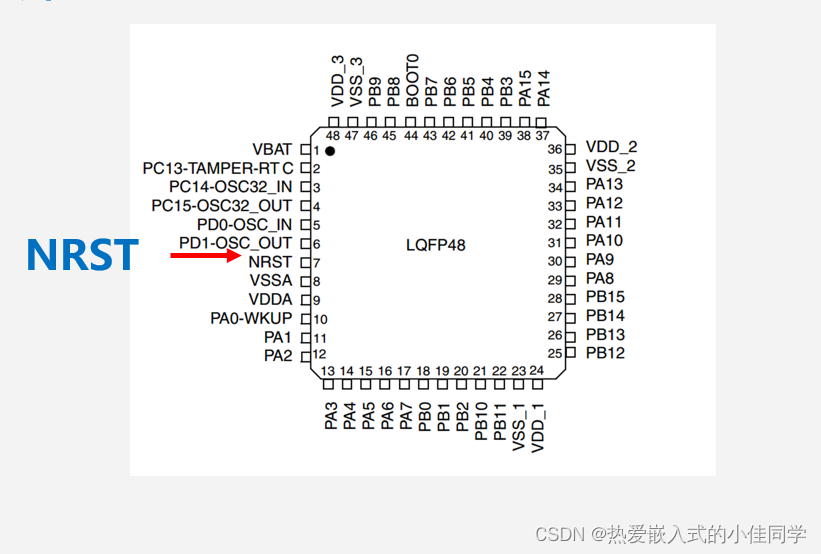

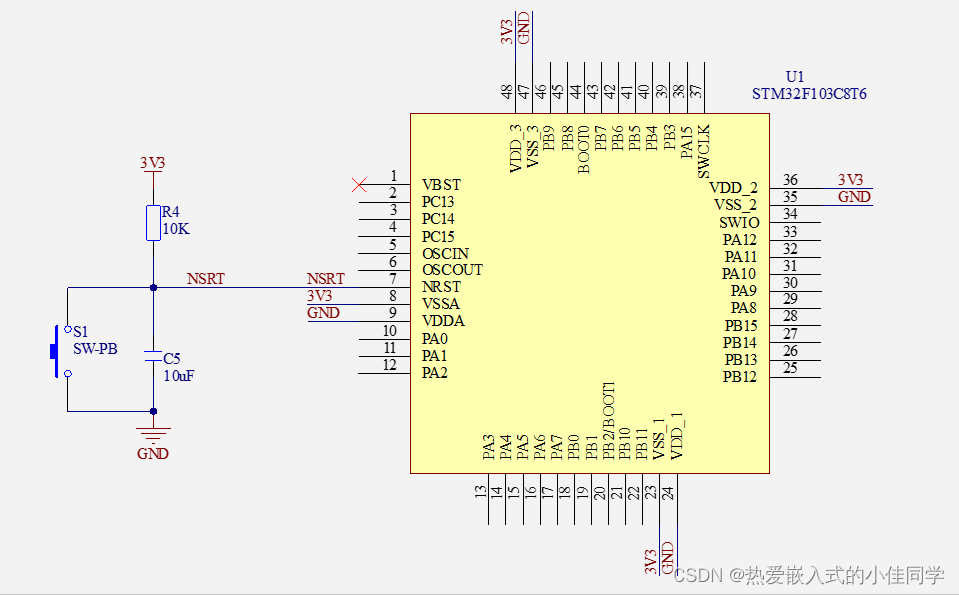

2.2.2 复位引脚和电路

复位引脚:当NRST为低电平时复位

复位电路:

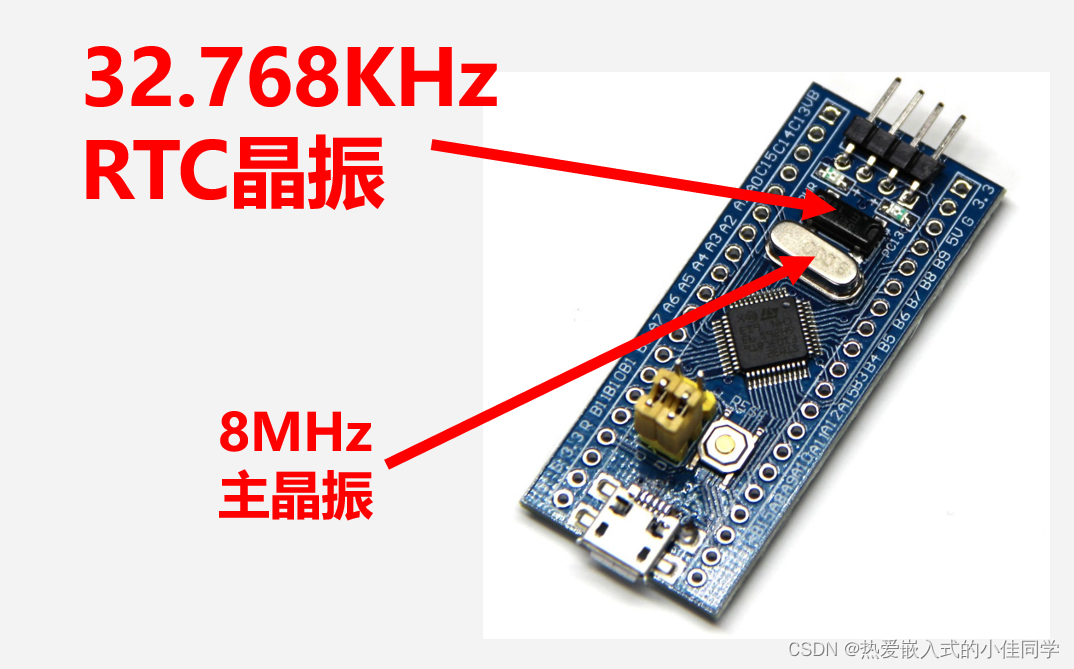

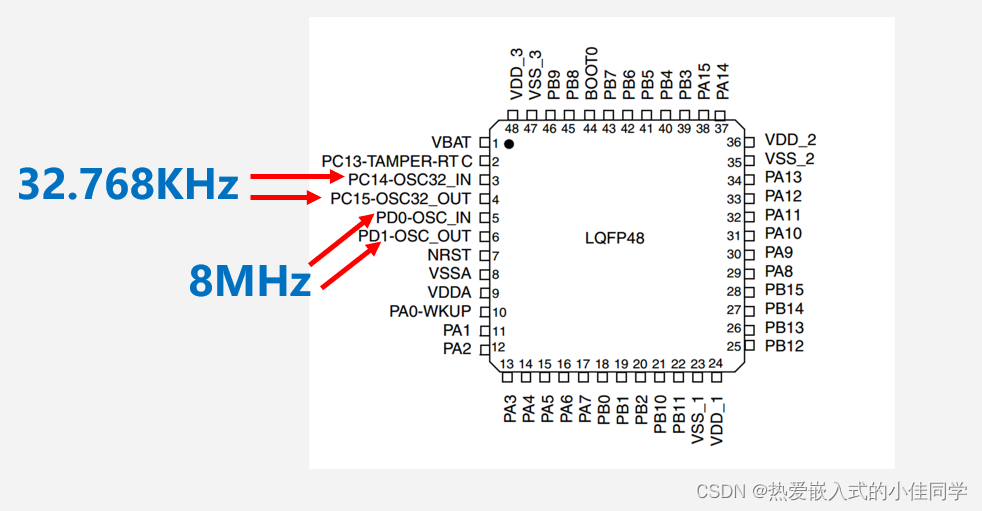

2.3 晶振模块

2.3.1 复位引脚

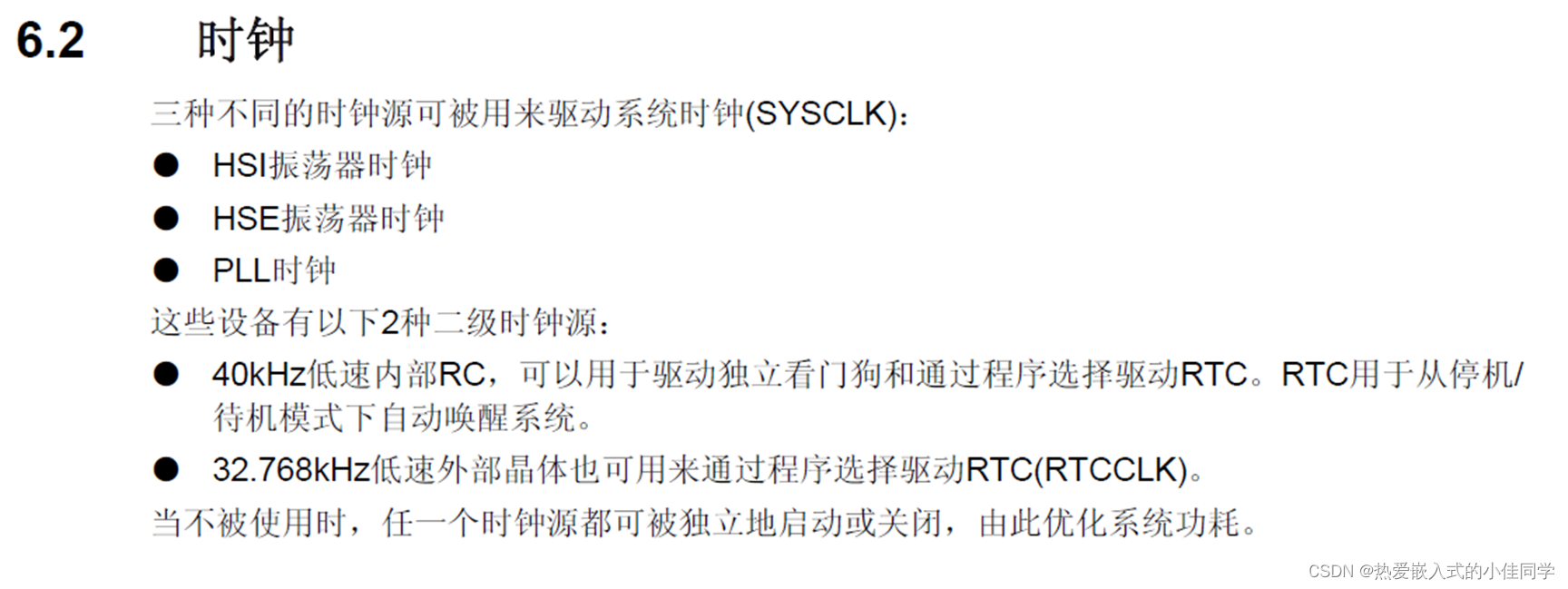

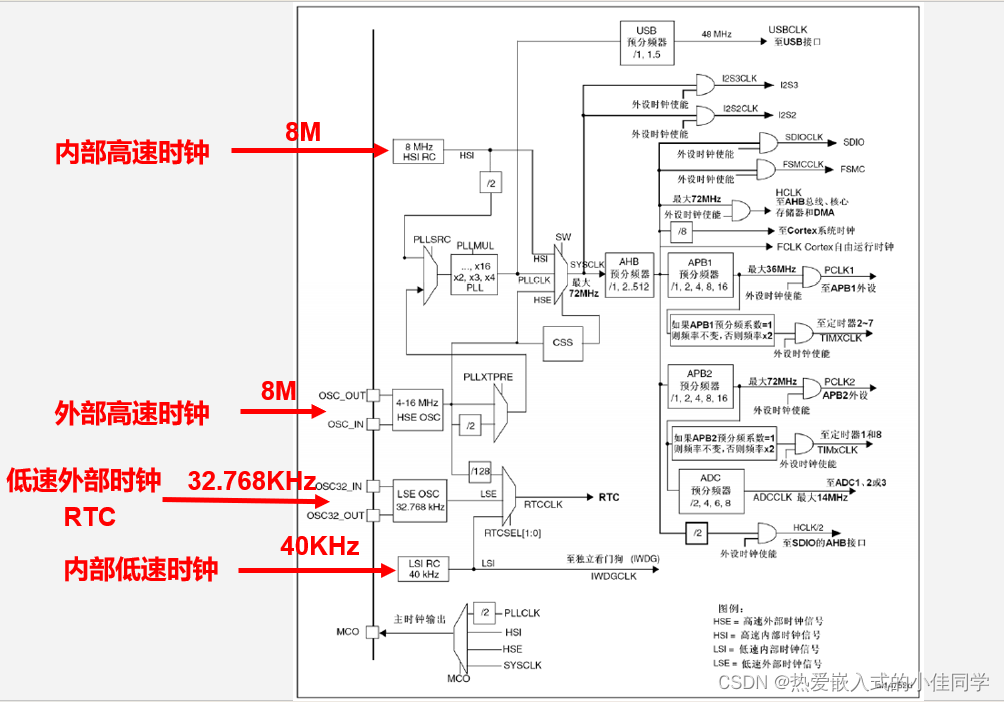

2.3.2 时钟和时钟树

时钟:

时钟树:

时钟树:

2.3.3 为什么不直接使用内部8M时钟源?

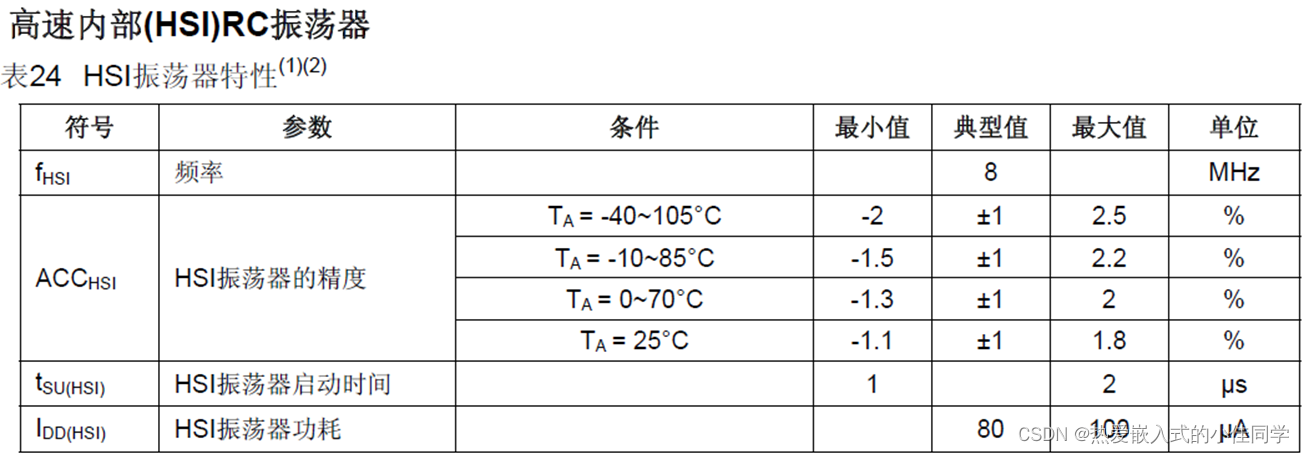

通过数据手册我们可以得知:内部的HSI是由ST出厂时校准过的,但是精度并不高,在0~70℃下误差范围达到1.3%到2%,即便是在标准的25℃下,也有 -1.1%到1.8% 的误差。

对于高波特率的异步串口通讯,或者需要高精度定时的场合,(如:需要跑积分算法的时候),用HSI就有隐患,甚至根本达不到设计要求。

2.3.4 8MHz主晶振介绍

晶振是由石英晶体组成的,石英晶体之所以能当为振荡器使用,是基于它的压电效应:在晶片的两个极上加一电场,会使晶体产生机械变形;在石英晶片上加上交变电压,晶体就会产生机械振动,同时机械变形振动又会产生交变电场,虽然这种交变电场的电压极其微弱,但其振动频率是十分稳定的。当外加交变电压的频率与晶片的固有频率(由晶片的尺寸和形状决定)相等时,机械振动的幅度将急剧增加,这种现象称为“压电谐振”。

晶振电路为主控芯片提供系统时钟,所有的外设工作,CPU工作都要基于该时钟,类似于整个系统的“心跳节拍”。

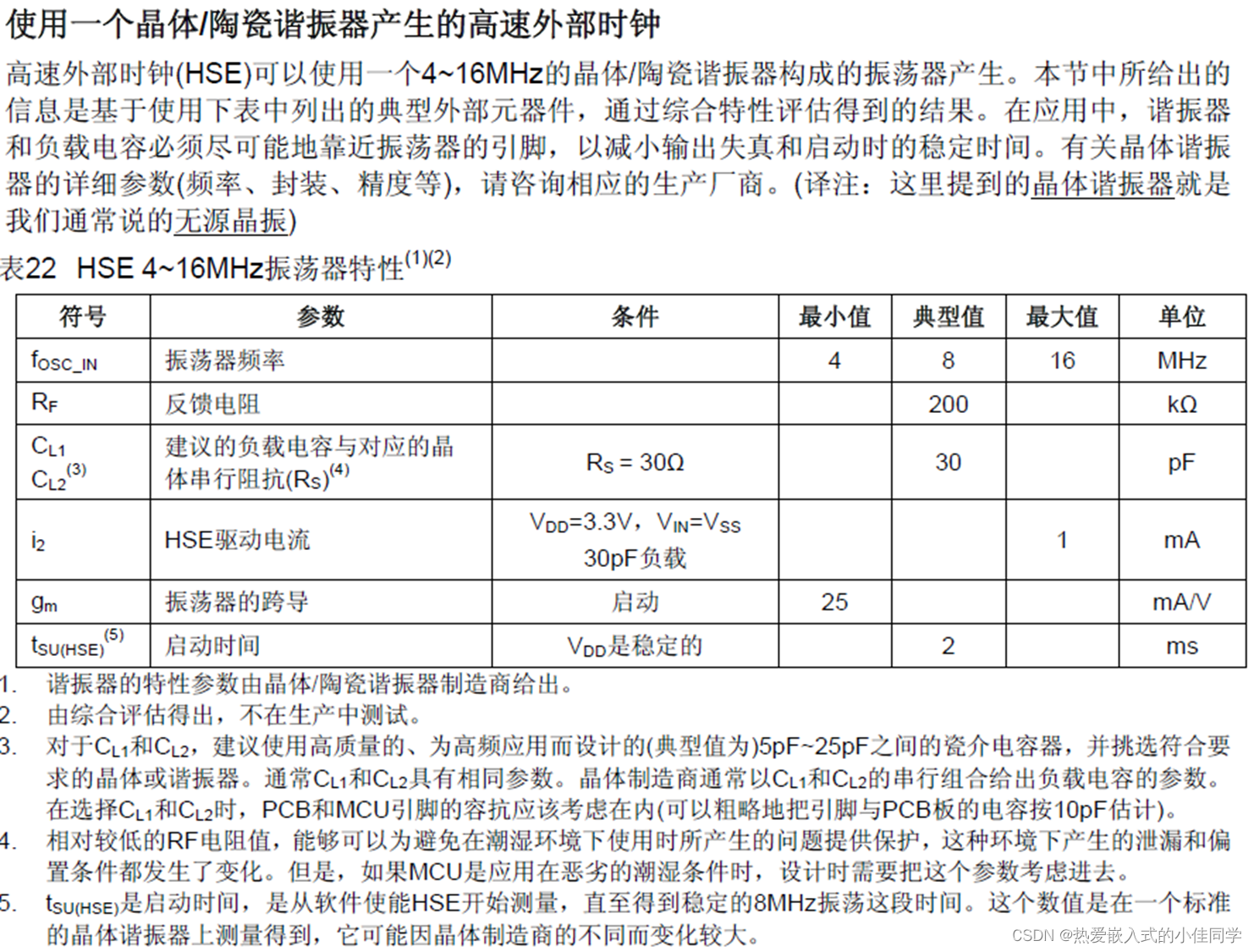

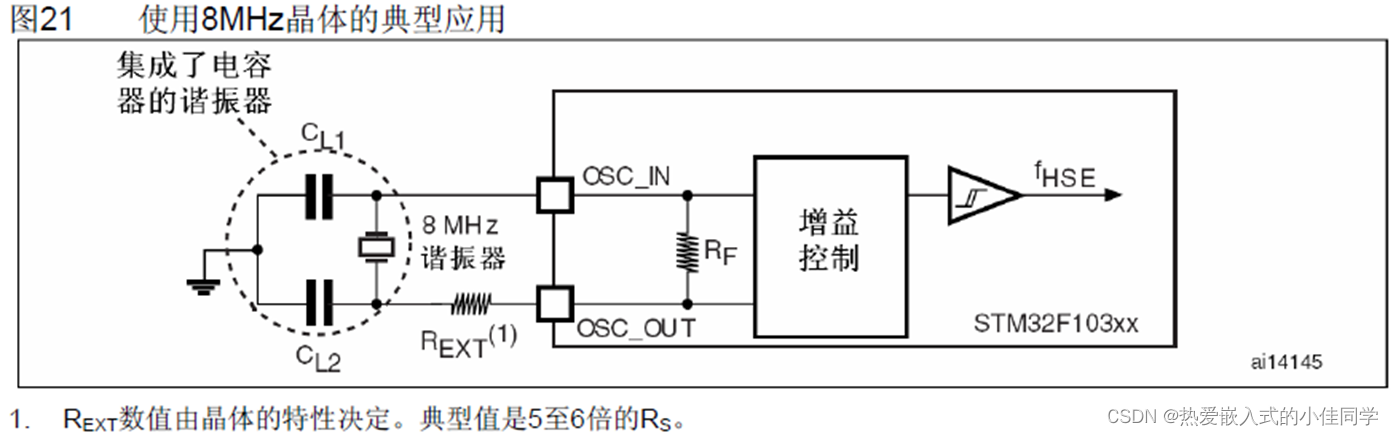

晶振分为无源和有源,但是本质上都是皮尔斯震荡电路(反相放大器+电阻+电容+晶体+电源),只不过对于单片机而言,单片机内部集成了反相放大器和电阻以及电源,外接晶体和电容就可以了,这里的晶体就称之为无源晶振。

而有源晶振是将皮尔斯振荡器作成一个整体,直接加电源即可工作,当然,价格也会比无源的贵一些。

- 增益控制: 增益很大的反相放大器。

- 8MHZ谐振器: 晶体。

- CL1、CL2: 匹配电容。是电容三点式电路的分压电容,接地点就是分压点。以接地点即分压点为参考点,输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡,它们会稍微影响振荡频率,主要用与微调频率和波形,并影响幅度。

- RF: 反馈电阻(一般≥1MΩ)它使反相器在振荡初始时处于线性工作区。

- REXT: 限流电阻,与匹配电容组成网络,提供180度相移,同时起到限制振荡幅度,防止反向器输出对晶振过驱动将其损坏。

2.3.5 为什么选择32.768KHz RTC晶振?

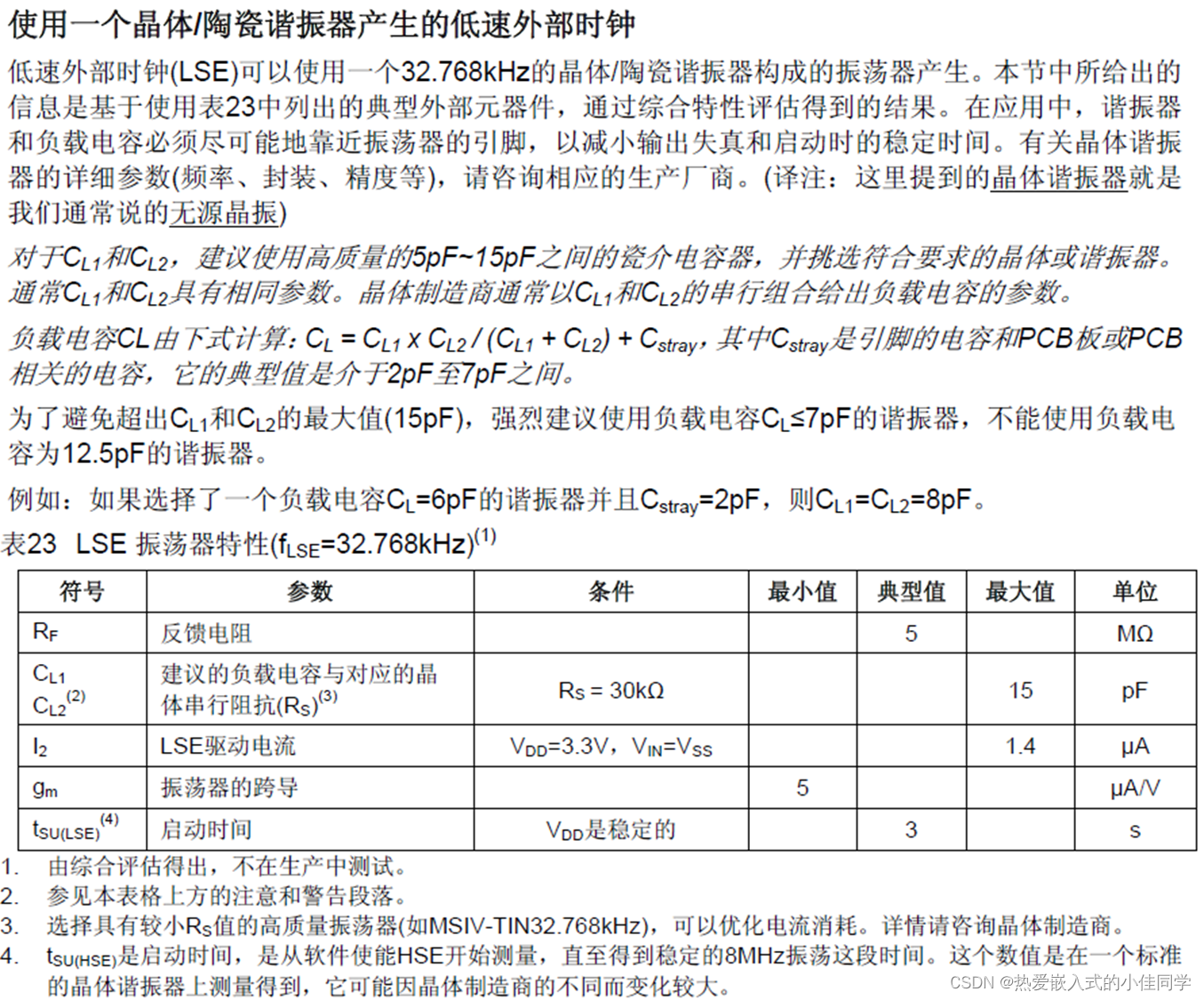

32.768KHZ的晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1HZ/秒的信号。

那为什么选择15分频呢?

频度越高计时精度越高,误差越小。

通常工作频率越高,单片机等数字电路的功耗越大,32.768KHz这个频率比较低,对降低电路功耗有利。

综上选择32.768Hz是取折中的选择!

2.3.6 晶振原理图

2.4 程序下载口

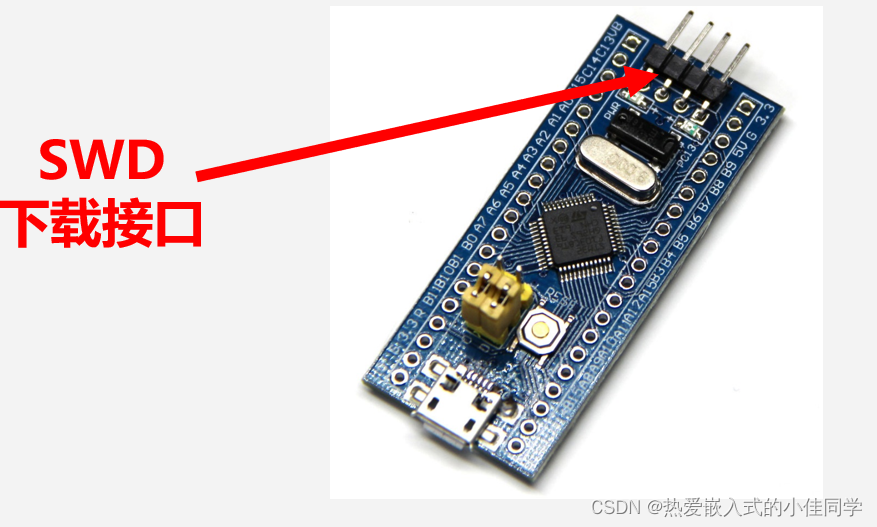

STM32F103C8T6烧录下载方法大体上有三种,分别为JTAG下载,SWD下载,以及串口下载。

2.4.1 JTAG下载:

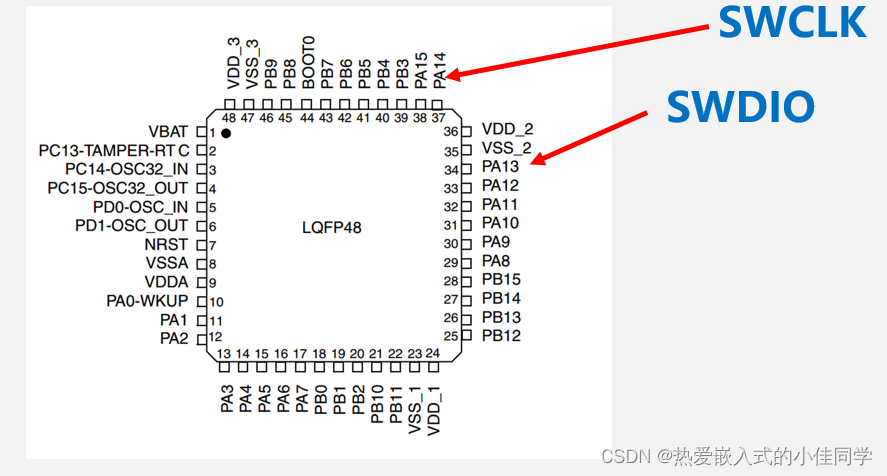

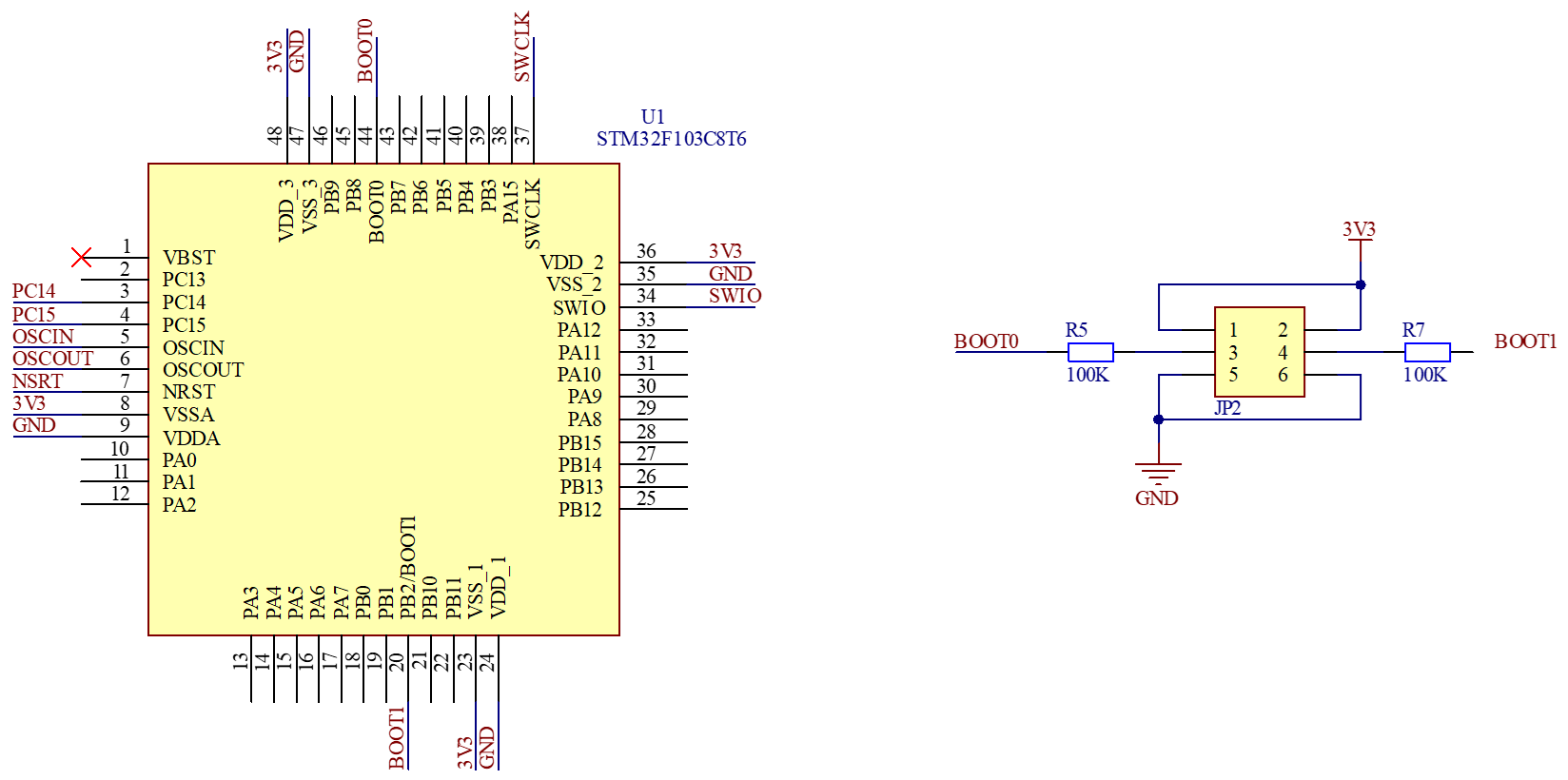

JTAG全名为Joint Test Action Group,即为联合测试行动小组,是一种国际标准测试协议。JTAG下载是需要依靠烧录器的,标准的JTAG接口是4线的,包括 JTMS, JTCK,JTDI, JTDO,它们的功能分别是模式选择,时钟输入,数据输入和数据输出,烧录器上的引脚对应连接到STM32F103C8T6的I/O口分别为PA13,PA14,PA15,PB3,加上接VCC和GND,所以JTAG接口最少需要6个引脚。同时单片机的BOOT0,BOOT1引脚要接地。

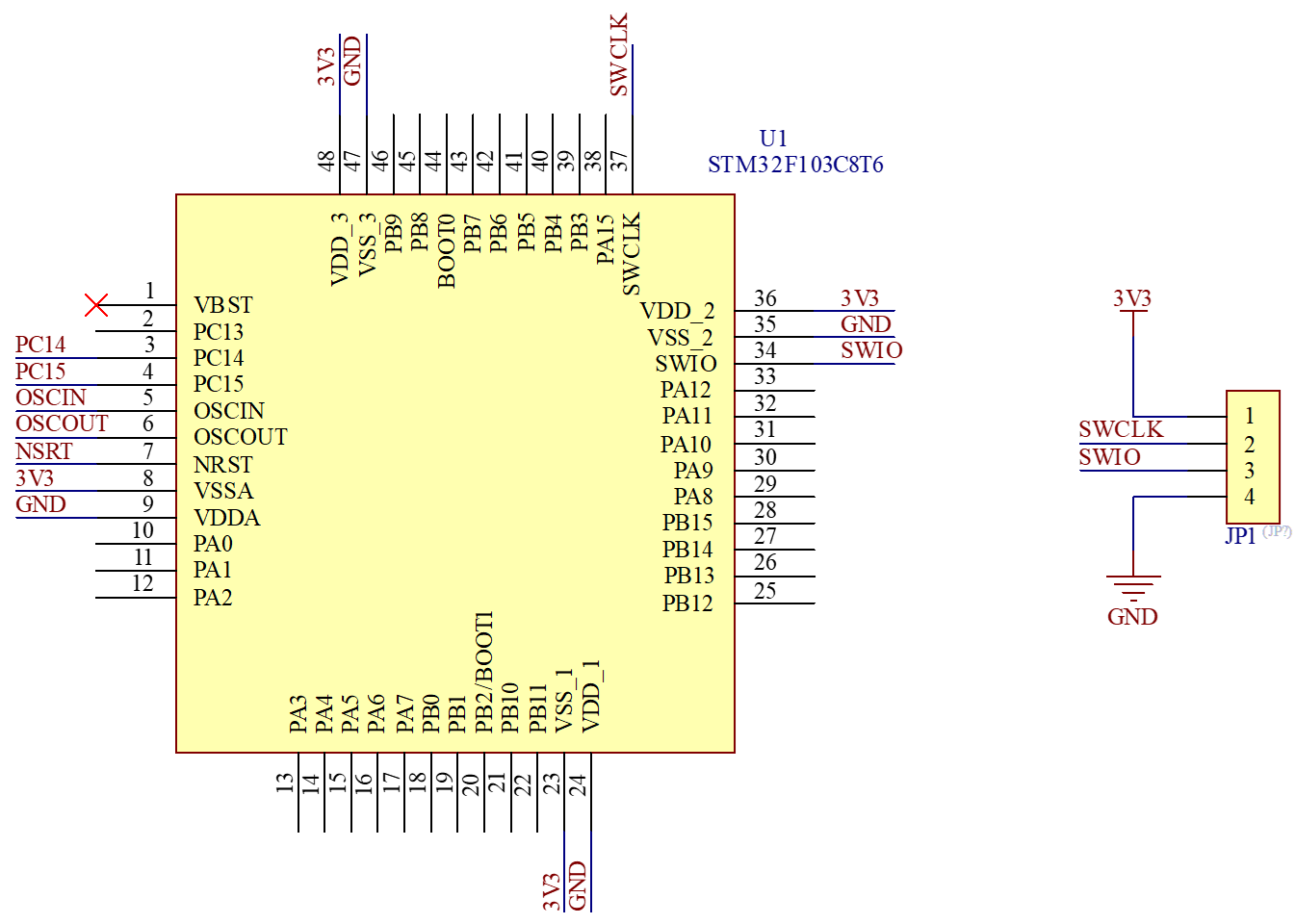

2.4.2 SWD下载:

SWD全名为Serial Wire Debug,即为串行调试接口。SWD下载是需要依靠烧录器的,SWD接口是2线的,包括SWDIO,SWCLK,它们的功能分别是数据输入输出和时钟输入,烧录器上的引脚对应对应连接到STM32F103C8T6的I/O口分别为PA13,PA14,加上接VCC和GND,所以SWD接口最少需要4个引脚。同时单片机的BOOT0,BOOT1引脚要接地。

2.4.3 串口下载:

通过USART进行烧录下载。串口下载是不需要依靠烧录器的,它直接通过安卓线连接电脑和单片机,其中STM32F103C8T6与电脑相连接的串口为USART2,对应的I/O口为PA2(TX),PA3(RX),一般在开发板上会使用串口下载,简单方便。同时单片机的BOOT0引脚要接高电平,BOOT1引脚要接低电平。

我们这里采用的烧录方式为SWD下载,下载电路设计时将PA13(SWDIO),PA14(SWCLK),VCC和GND这4个引脚引出

2.4.4 程序下载口原理图

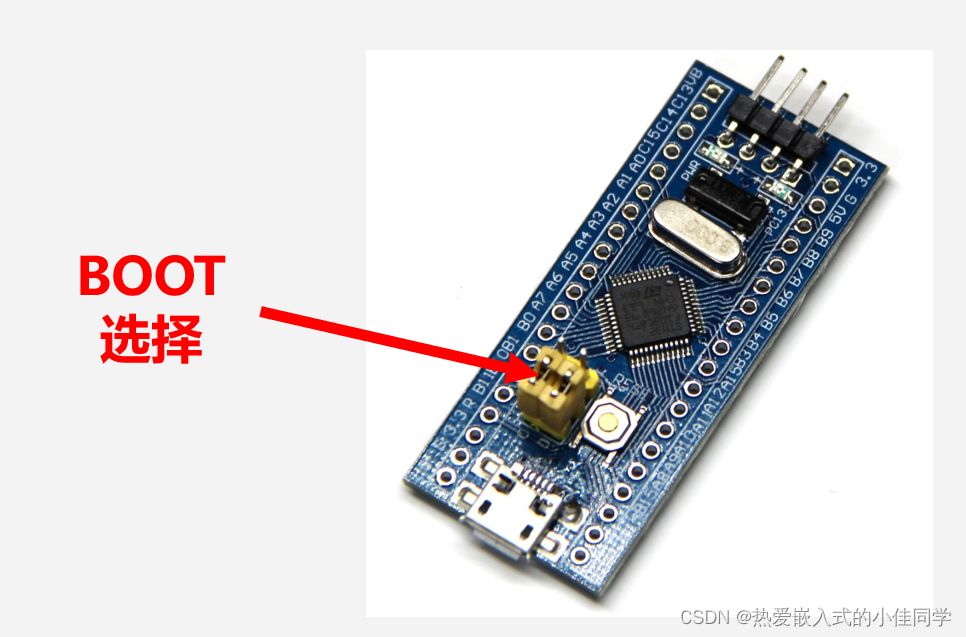

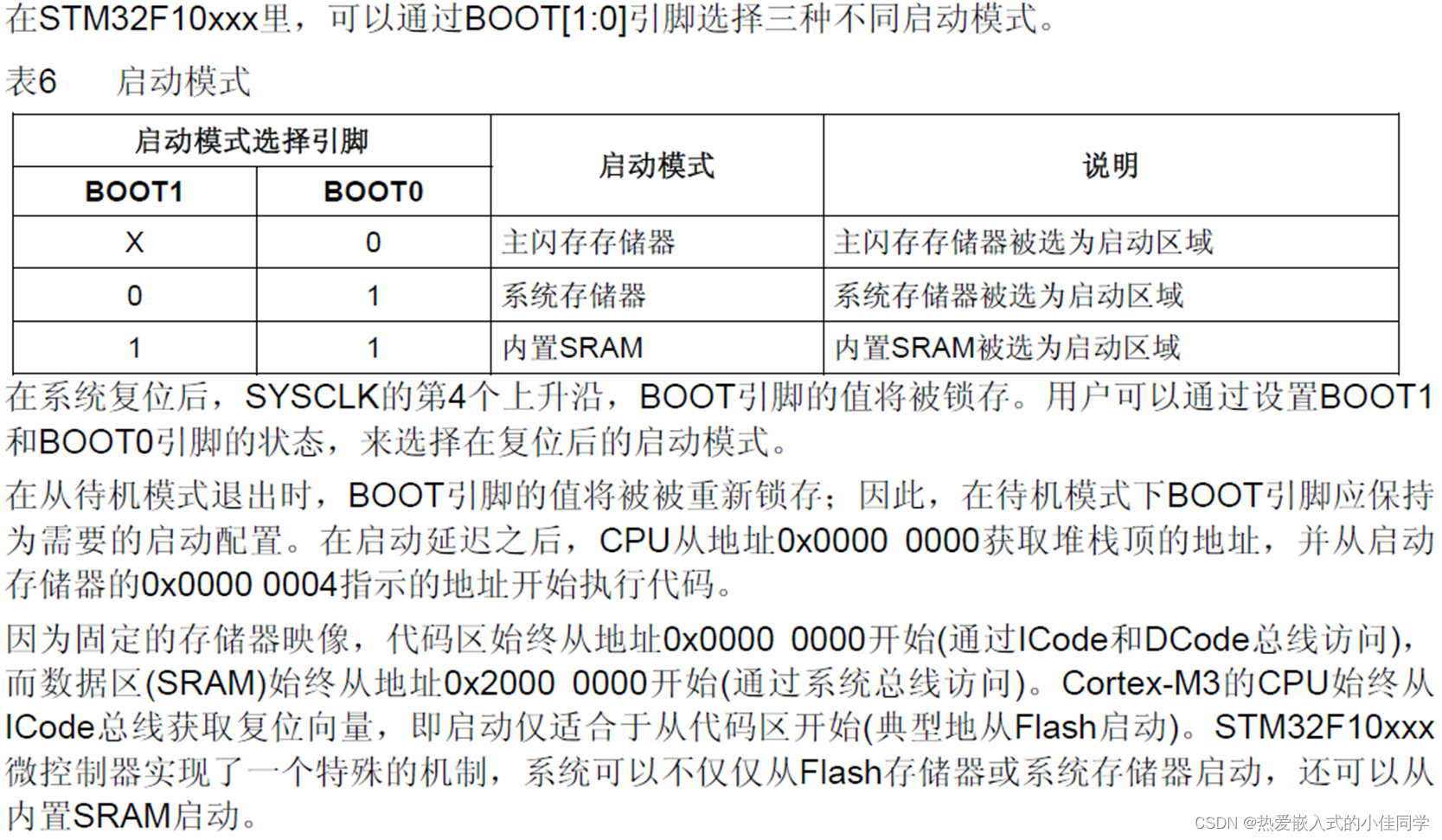

2.5 启动方式

2.5.1 三种启动方式

第一种方式(boot0 = 0):Flash memory启动方式

启动地址:0x08000000 是STM32内置的Flash

因为JTAG或者SWD模式下载程序时,是下载到内置的Flash中

所有重启后需要从内置Flash启动程序。

第二种方式(boot0 = 1;boot1 = 0):System memory启动方式

启动地址:0x1FFF0000从系统存储器启动,这种模式启动的程序功能是由厂家设置的。

系统存储器是芯片内部一块特定的区域,STM32在出厂时,由ST在这个区域内部预置了一段BootLoader, 也就是我们常说的ISP程序, 这是一块ROM,出厂后无法修改。一般来说,我们选用这种启动模式时,是为了从串口下载程序,因为在厂家提供的BootLoader 中,提供了串口下载程序的固件,可以通过这个BootLoader将程序下载到系统的Flash中。

第三种方式(boot0 = 1;boot1 = 1):SRAM启动方式。

启动地址:0x20000000 内置SRAM,既然是SRAM,自然也就没有程序存储的能力了,这个模式一般用于程序调试。假如我只修改了代码中一个小小的地方,然后就需要重新擦除整个Flash,比较的费时,可以考虑从这个模式启动代码(也就是STM32的内存中),用于快速的程序调试,等程序调试完成后,在将程序下载到SRAM中。

2.4.2 启动原理图

总结:

文章已获作者授权转载,版权归原作者所有,如有侵权,与本账号无关,可联系删除。 原文作者:热爱嵌入式的小佳同学

原文链接:https://blog.csdn.net/m0_74712453/article/details/136331394

2115

2115

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?