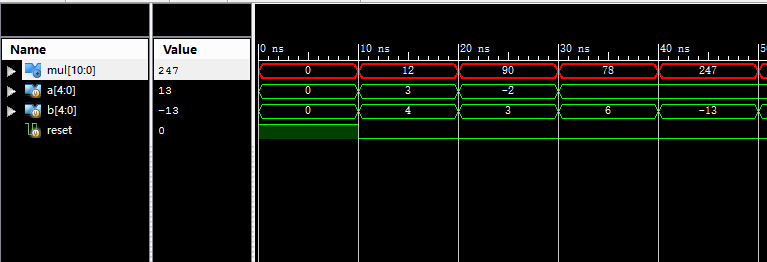

a,b,da,dm,mul都定义成有符号类型,下面这几行代码综合后仿真可以得到正确的运算结果。

assign da= (reset==1) ? 6'sb0 :a+b;

assign dm= (reset==1) ? 6'sb0 :a-b;

assign mul= (reset==1) ? 11'sb0 :a*b;下面这几行代码当输入为负数时,结果错误,为什么呢?

assign da= (reset==1) ? 6'b0 :a+b;

assign dm= (reset==1) ? 6'b0 :a-b;

assign mul= (reset==1) ? 11'b0 :a*b;因为6’sb0是有符号数,而6’b0是无符号数,而在 6’b0 :a+b; 这个表达式中左边是无符号,右边是有符号数,则右边也会转换成无符号数。

例如:当我们在testbench里面赋 a=-2; b=3;因为输入端口是有符号类型,所以输入的二进制是 11110 (-2,即2的补码表示),00011,

而这个表达式里 6’b0 :a*b;,因为左边是无符号类型,所以a b都变成了无符号类型,此时 11110 被理解成无符号数30, 00011是3,所以结果是90,而不是-6.

所以,要注意,“在一个表达式中混用signed 和unsigned 操作数时必须非常小心,只要有一个操作数时是无效的,那么在开始任何操作前,所有其他的操作数都被转换成了unsigned”——《Verilog HDL入门,54页》

4383

4383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?