FPGA入门——1位全加器

一、全加器与半加器

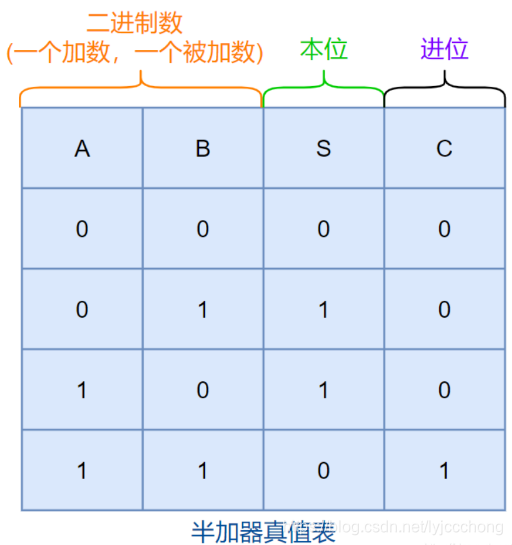

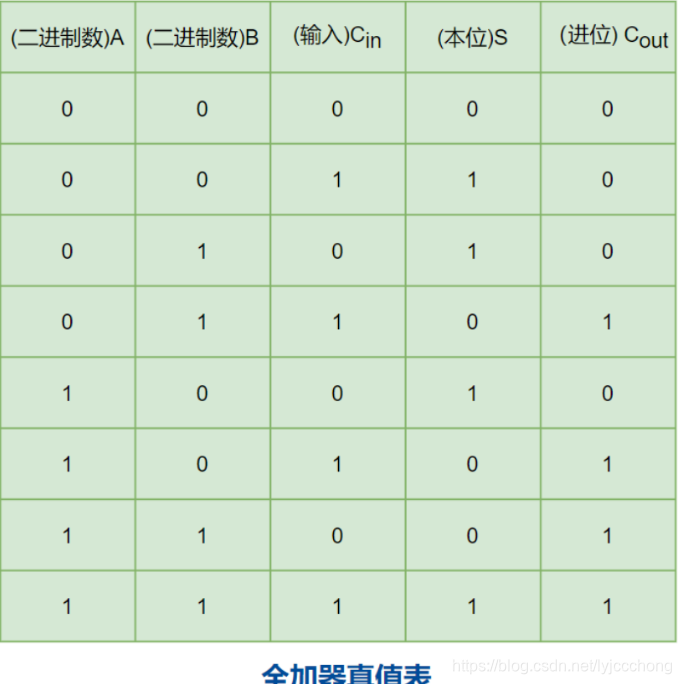

1.1 半加器

1.2全加器

二、原理图输入实现1位全加器

2.1 创建工程

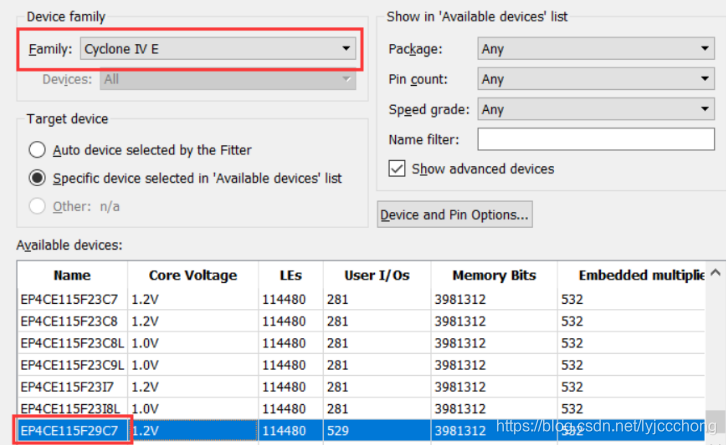

选择目标芯片:CycloneIVE系列的EP4CE115F29C7

2.2 原理图输入

1.新建Block Diagram,输入and2

2.调入xnor、输入输出引脚input、output

3.连接好电路图,并修改输入输出引脚名字

4.保存编译

2.3 将设计项目设置成可调用的元件

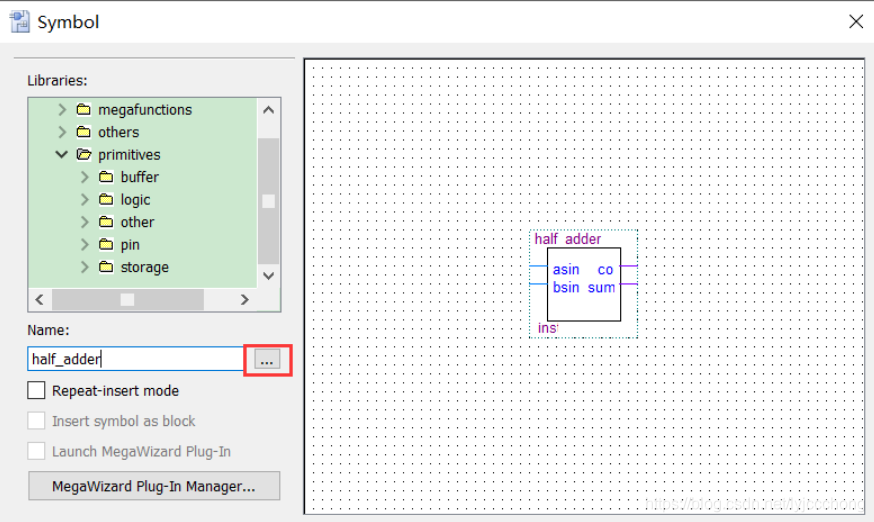

为了构成全加器的项层设计,必预将以上设计的半加器full_adder.bdf设置成可调用的元件。在打开半加器原理图文件full_adder.bdf的情况下,选择File中的Create/Update→Create Symbol Files for Current File项,即可将当前文件full_adder. bdf变成一个元件符号存盘,以待在高层次设计中调用。

2.4 半加器仿真

1.新建波形文件

2.输入波形文件

3.设置输入波形取值

4.仿真,先保存文件为half_adder.vwf,然后点击

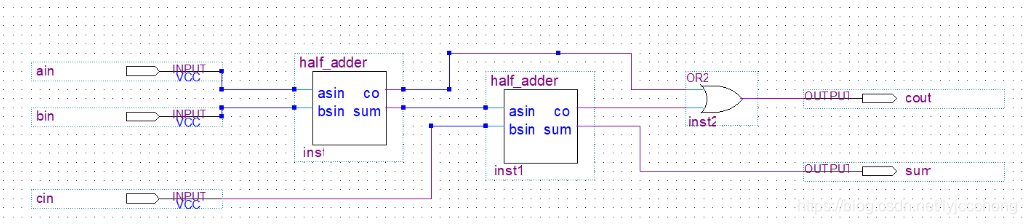

2.5 设计全加器顶层文件

1.File->New->Block Diagram

2.选择底层文件半加器的存储名“half_adder”调出半加器

3.再调出其他元件or2

4.连好电路图

5.保存编译

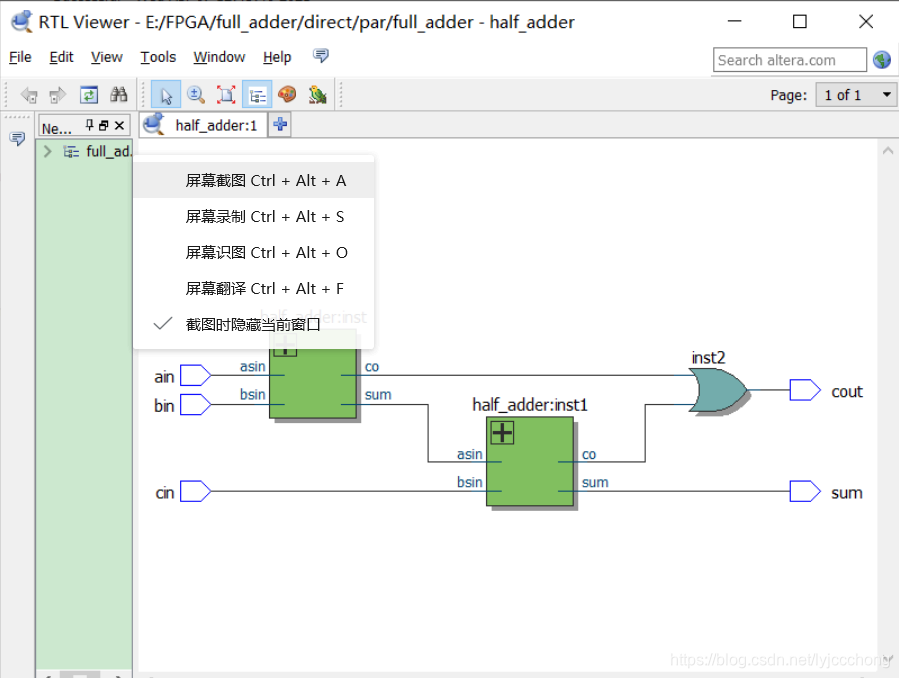

6.Tools->Netlist->RTL Viewer

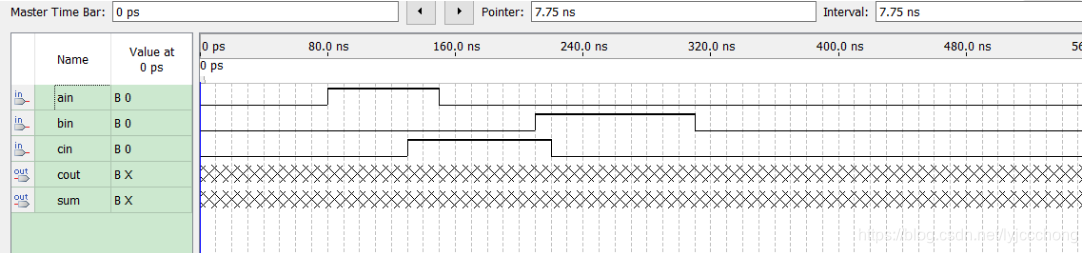

2.6 全加器仿真&同1.4

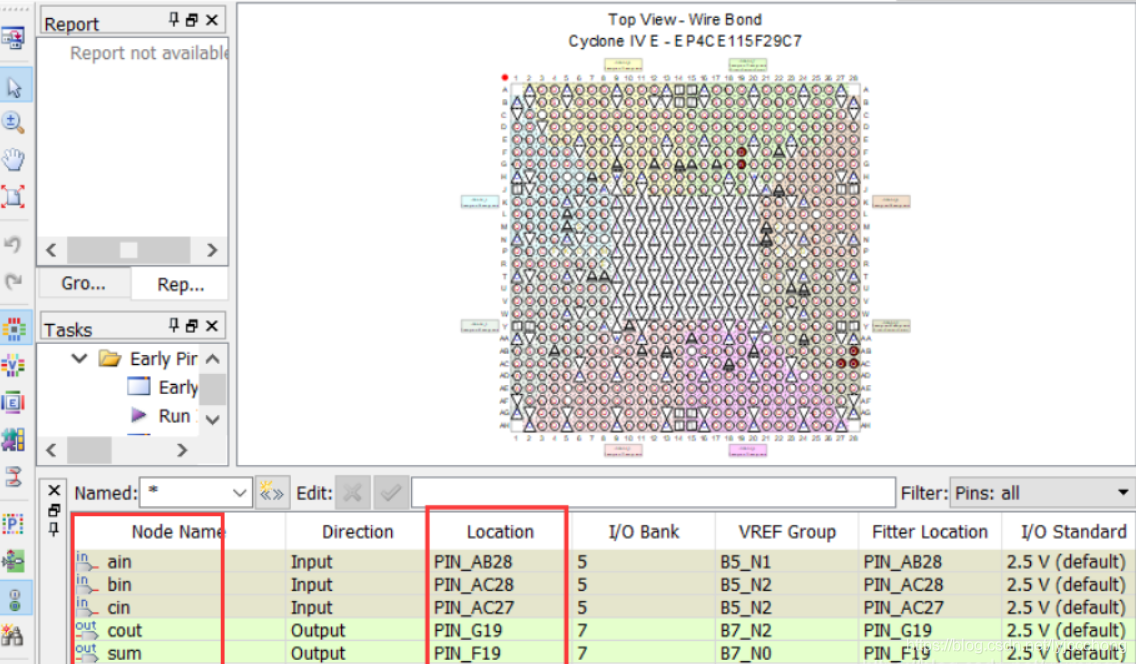

2.7 硬件测试

1.引入pin引脚

Assignments→Pin Planner或者点击如下图位置

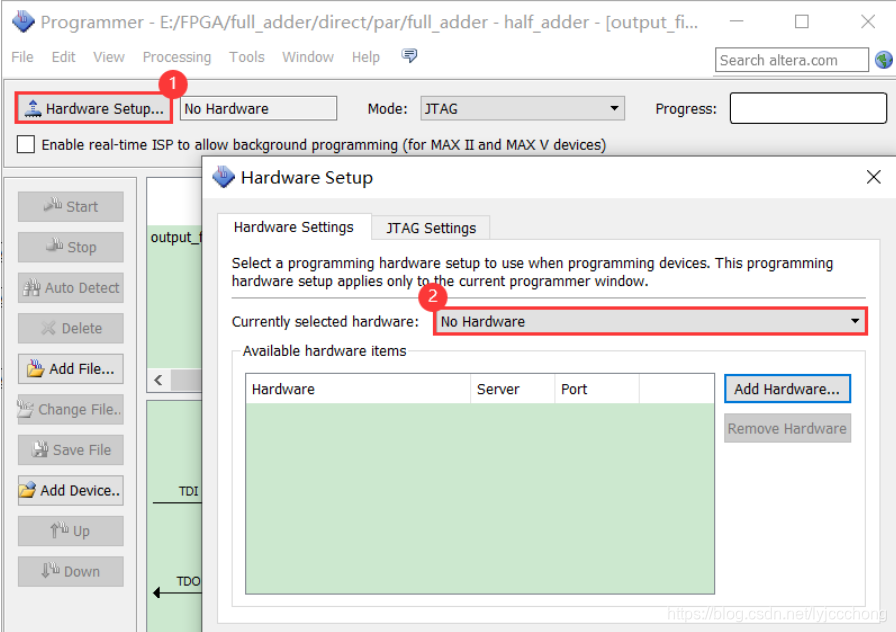

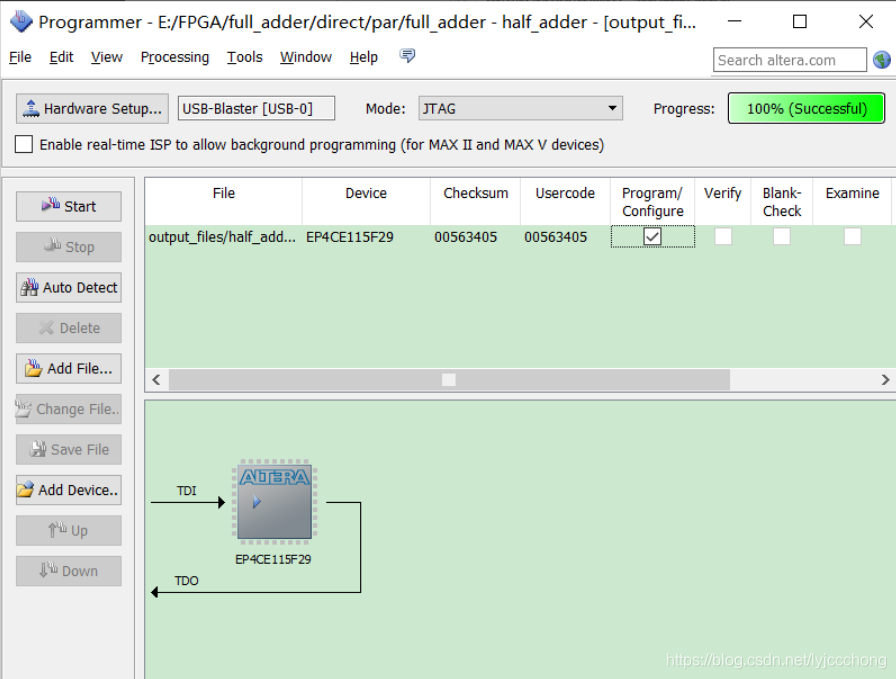

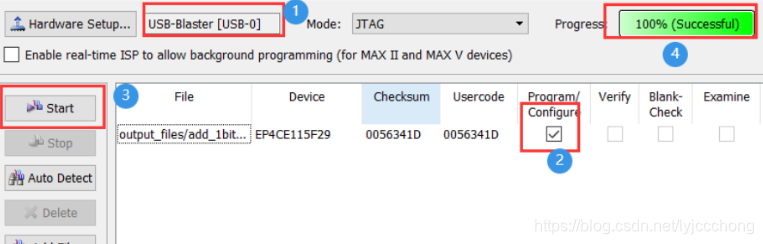

2.Tools->Programmer第一次下载需要安装硬件

3.没有altera USB blaster的需要安装驱动,下面是下载到硬件完成

三、Verilog实现1位全加器

3.1新建工程

芯片选择和之前一样

3.2.新建一个Verilog文件

module add_1bit(S,C_out,A,B,C_in);

input A,B,C_in ;

output S,C_out ;

reg S,C_out ;

always @(A or B or C_in)

begin

{C_out,S} = A +B +C_in ;

end

endmodule

3.3编译仿真

2687

2687

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?