asic设计的时候,芯片都需要使用复位信号。复位有同步复位、异步复位两种分各种情况而定,一般来说所有的寄存器都需要提供复位信号,以确保开始工作的时候系统处于一个确定的状态。但是移位寄存器这一类在某些高速信号电路中使用的时候需要去掉复位信号以获得最佳性能。

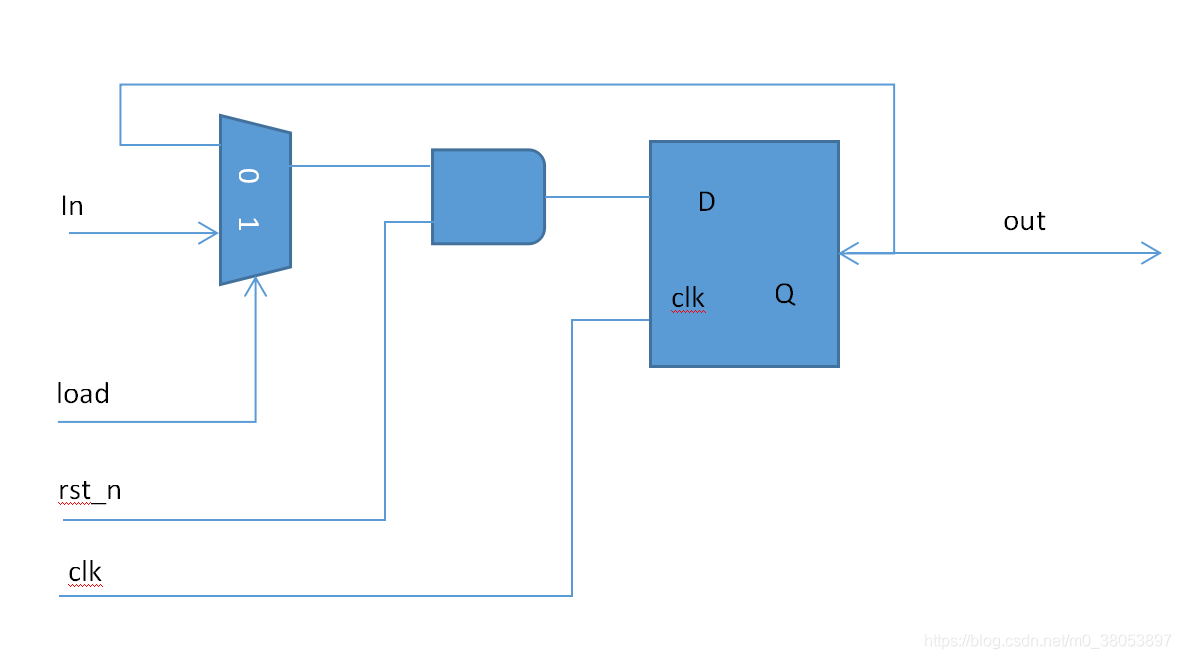

1 同步复位设计

由于复位树的高扇出,导致复位带载功率大,复位信号上升沿相对来说较为缓慢,对于时钟信号来说属于一个迟到的信号,即使经过缓冲区缓冲,也要尽可能减少中间逻辑数量。

同步复位的优点:

- 同步复位一般能确保电路是100%复位

- 综合的时候效率更高、尤其是在类似上述触发器门控复位的时候

- 同步复位动作只发生在有效时钟沿,正好用时钟过滤了复位信号的毛刺

同步复位的缺点:

- 同步复位需要一个脉冲展宽器,以保证复位信号能出现在时钟有效沿处,可以使用一个小计数器来确保复位发生在制定周期个时钟信号的有效沿。

- 如果复位由SOC的组合逻辑产生或复位必定经过多级组合逻辑,就会存在潜在问题。在仿真过程中,根据复位的产生方式或在功能模块上的使用方式,复位信号可能是X,也就是任意边沿。

- 如果刚好和门控时钟遇到了,就会出现时钟不启动,复位也无法复位的现象,这个时候就需要使用异步复位来确保系统启动。

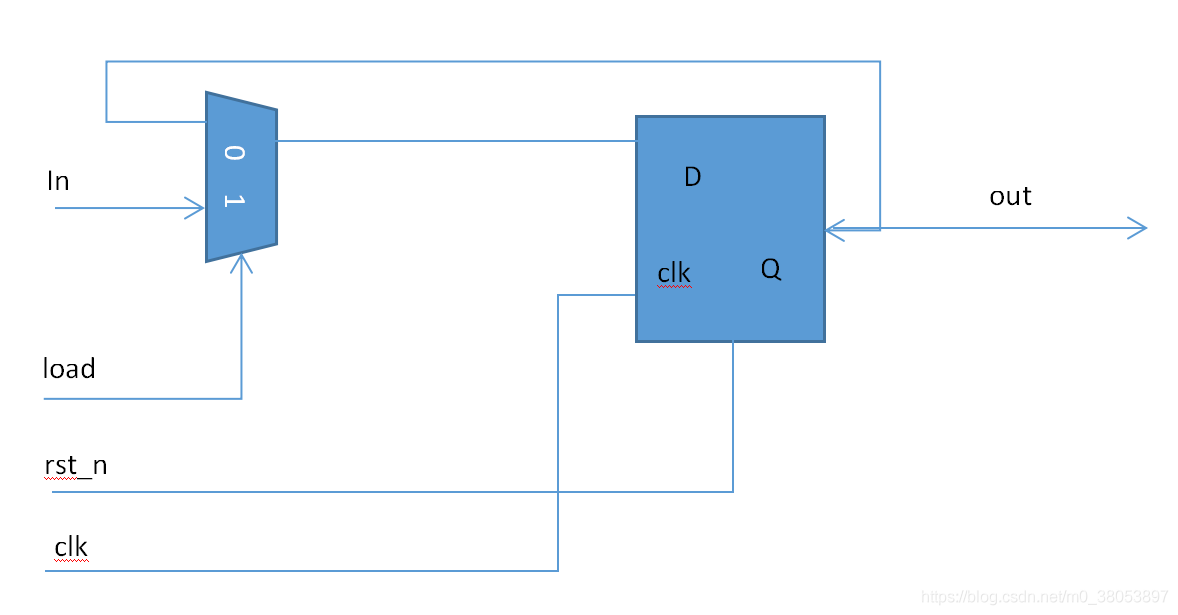

2使用异步复位设计

采用上图所示的复位电路,本质上就是复位出低电平,不复位出输入。

异步复位设计优点

- 延迟低

- 不需要时钟

缺点

- 在DFT时,如果异步复位信号不能直接被IO引脚驱动,就必须将异步复位线路与复位驱动器断开以保证DFT扫描和测试的正确

- 如果在侧小复位信号的时候在触发器时钟有效沿附近,触发器的输出就会进入亚稳态,因此SOC的复位状态就会丢失。

- 毛刺或者噪声容易导致异常复位

2053

2053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?