可能标题有点大,各位看官仔细看吧。。。

第一部分各个开发编写环境介绍:

转自:https://zhuanlan.zhihu.com/p/33443736

各个编辑器的肤浅体验(for Verilog)

个人体验,有一说一。。。就不列123了,都是自己的感受。

这两天我试用了notepad++,Vim,Atom,VScode,Sigasi 以及 sublime。

至于Emacs,还是@神吧(不是sb)。

UE:不说了,之前一直在用,界面风格我喜欢,带列操作,语法高亮,自动补全,自动缩进功能都有,但是需要uew文件,没有版本控制功能,并且需要正版支持。如果你很容易满足,并且喜欢的界面风格跟我一样,那就是他了。

notepad++:功能全面,上面说的功能都有,重要的是不需要下载别的文件,官方支持Verilog语法,但是没有版本控制功能,编程界面看不顺眼,毕竟动不动要一直对着他25个小时,还是顺眼点好,各位可以下载下来根据自己喜好安装。

Vim:编辑器之神,功能强大,因为我之前一直在用UE,没有体验到他的强大,反正别人是这么说的,如果你觉得vim比我这个方法好点,欢迎分享=。=我之所以没用,当然是因为编程界面啊。。。

***Atom:***git的东西,免费,但以后收费不收费不知道。没有官方Verilog支持,需要下载verilog的社区Package,对Verilog语法支持可以说弱爆了,语法高亮颜色单一,哪有什么五彩缤纷的代码,视觉瞬间回到文本编辑器,软件我卸载了,自动补全不记得有没有,但是就算有相比sublime也是弱爆了。值得关注的是Atom编程界面好看,支持外部插件,拓展性好,可以实现语法报错,自带git版本控制,这点我喜欢。我对他持有观望态度,什么时候插件资源库成熟了,记得@我。ps:使用插件可以支持列操作

VScode:微软亲儿子,但免费,各种优势请各位百度,我只说与Verilog相关的。可以搜索到Verilog语法包,插件几乎没有。语法高亮就一到两个颜色,自动补全功能不全,有些关键词不能补全,补全功能也比较弱,自带git版本控制。到此为止我体验了作为一个Verilog编程者的心酸,建议各位改行学python吧=。= 别和我竞争了。

Sigasi:针对Veilog编程者定制的工具,暖心。功能强大,语法高亮这种最低要求不是考量他的标准,功能方面去官网看下,你会明白的。但是要免费的话,你得要连上他们的服务器,反正我是没连上。。。有别的方法也可以@我一下,悄悄地告诉我。

Sublime:好处大大的,界面顺眼。上面说的,没说的功能都有,按照文章安装下、体验下你就知道了。缺点是需要安装cygwin等软件,过程相对多点,但是一劳永逸。但是没有git版本控制功能是遗憾。如果你很容易满足的话,那我建议你安装上面的UE或者notepad++,就OK了,此文转发下就行了。ps:列操作鼠标中间点击

这里使用最多的应该是UE和NPP了,所以网上大把教程,按照教程来就好了,接下来主要介绍VIM和Sublime(这个教程也比较多,主要参考知乎上的一篇文章)

华丽分割线

一、vim + syntastic + verilator or iverilog

这里有别人弄好的VIM,可惜不会用,又会用的大佬请留言。

Introduction

syntastic让你可以在vim里可以使用lint功能,让你在写code時检查看看有沒有语法上的错误或者可能潜在的错误

Install

linter

首先要先安装inter有两种选择: Icarus Verilog或是verilator,看你偏好哪一种,我是经由homebrew安装:

$brew install verilator

$brew install iverilogsyntastic

syntastic我是使用vundle安装,你也可以通过其他package manager安裝.請參考GITHUB

通过vundle安装(这里我是通过vundle安装syntastic,如果不会使用vundle,請參考GITHUB

Plugin 'scrooloose/syntastic'在vimrc加上以下几行, 以下是参考syntastic官方的设定

set statusline+=%#warningmsg#

set statusline+=%{SyntasticStatuslineFlag()}

set statusline+=%*

let g:syntastic_always_populate_loc_list = 1

let g:syntastic_auto_loc_list = 1

let g:syntastic_check_on_open = 1

let g:syntastic_check_on_wq = 0设置lintor:verilator和iverilog我都设置了,两个都有则会一起检查,若是第一个挂了它会自动找第二個,如果你只想使用其中一种,留着你要的那一个即可

let g:syntastic_verilog_checkers = ['verilator','iverilog']Use

完成之后可以用:SyntasticInfo查看是否有配置完成

接下來就可以使用:SyntasticCheck开始语法检查功能啦

syntastic好像也有提供在:w時提供检查的功能

Some problem

syntastic会根据filetype去開啟不同语言的linter

可以用:set filetype?看看是不是verilog

有些人会使用verilog_systemverilog的套件來让verilog产生语法高亮,filetype則会是verilog_systemverilog,此时syntastic则不会支持

目前我的解法是在verilog_systemverilog套件里判断副档名的地方更改.

本來是长这样:

au! BufNewFile,BufRead *.v,*.vh,*.vp,*.sv,*.svi,*.svh,*.svp setfiletype verilog_systemverilog为了同時使用syntastic 和verilog_systemverilog的语法高亮,我的做法是将.v檔案當成普通的verilog并让syntastic只支持.v,我將上面改成:

au! BufNewFile,BufRead *.vh,*.vp,*.sv,*.svi,*.svh,*.svp setfiletype verilog_systemverilog

au! BufNewFile,BufRead *.v setfiletype verilog_systemverilog.verilog也就是让.v档案同時有两种filetype, .v档案之外都当成verilog_systemverilog.

Summary

簡單來說你可以用一樣的方法去設定其他語言的linter

可以分成以下step:

- 安裝語言相對應的linter

- 安裝syntastic(如果本來就有可以跳此步驟)

- 查看syntastic官方文件,看syntastic有沒有支持你的linter

- 根據syntastic官方文件去設定你的linter

step3 的syntastic所支持的linter列表

Reference

[VIM插件: SYNTASTIC[语法检查]](http://www.wklken.me/posts/2015/06/07/vim-plugin-syntastic.html)

[[資工雜筆] 建置 vim + syntastic + eslint + gcclint](https://noootown.wordpress.co…

二、Sublime+Verilator建立强大的verilog编写环境

正文(5步走,其实不麻烦)

话不多说,上干货。

1、下载cygwin。

该软件在windows上模拟linux环境,为了编译verilator。如果你有别的方法编译verilator,自己就可以搞了,方法不限。

安装cygwin也可以感受linux命令行的强大,何乐不为。

2、cygwin安装

安装时我填写阿里的镜像服务器地址http://mirrors.aliyun.com/cygwin/,直接用软件里的镜像服务器地址,速度可以,如果下载速度不好的话,百度一个cygwin的镜像服务器地址。ps:安装Atom后,因为墙太高,你可以使用国内的镜像服务器下载Atom的package。

安装cygwin时需要安装下列插件

- binutils (搜索到binutils:GNU assembler)

- gcc (搜索到gcc-core、gcc-g++)

- gcc-mingw

(64bit电脑搜索到mingw64-i686-gcc-core和mingw64-i686-gcc-g++的,32bit电脑带X86的同上两个core和g++) - cc(C compiler)

- gdb(搜索到gdb:The GNU Debugger)

- perl(我全下了。。。有懂的可以说下)

- Flex(搜索到flex:A fast lexical)

- bison(在devel目录下)

- make(GNU)

或者(简单粗暴)直接把devel中的全选了

安装包先别删除编,编译verilator时缺什么模块可以后面通过再打开cygwin安装包安装。

3、下载verilator或者修改版的verilator,并在cygwin上编译verilator

注:verilator需要module里关联的module都在一个文件夹下,修改版则去除了这个限制。(我个人喜欢把源文件放在一个目录下,所以用了原版verilator)

在cygwin里输入下面代码,编译verilator。

unset VERILATOR_ROOT # For bash

cd verilator #打开verilator安装目录,自己修改目录

./configure #开始编译,缺什么用cygwin补什么。

make

make install4、sublime里安装SublimeLinter模块和SublimeLinter-contrib-verilator模块等

sublime安装方法自行百度,安装好后使用快捷建ctrl+shift+p打开命令窗口,输入package control,点击搜索结果,安装包管理插件。安装好后使用快捷建ctrl+shift+p打开命令窗口,输入install package,等一会出现命令窗口,在命里窗口里搜索SublimeLinter模块、SystemVerilog模块、VerilogGadget模块,点击安装。ps:卸载的话,使用remove,跟安装同理。

PS:如果搜索模块搜索不到,请先install package 再 搜索相关模块。

- SublimeLinter模块用于连接verilator。

- SystemVerilog模块用于语法高亮,高端自动补全等。

- VerilogGadget模块用于自动生成模块实例化,自动生成testbench,自动生成case序列等。

5、修改paths路径

将cygwin的bin夹下这三个的文件拷贝到verilator的bin目录下

cygwin1.dll

cygstdc++-6.dll

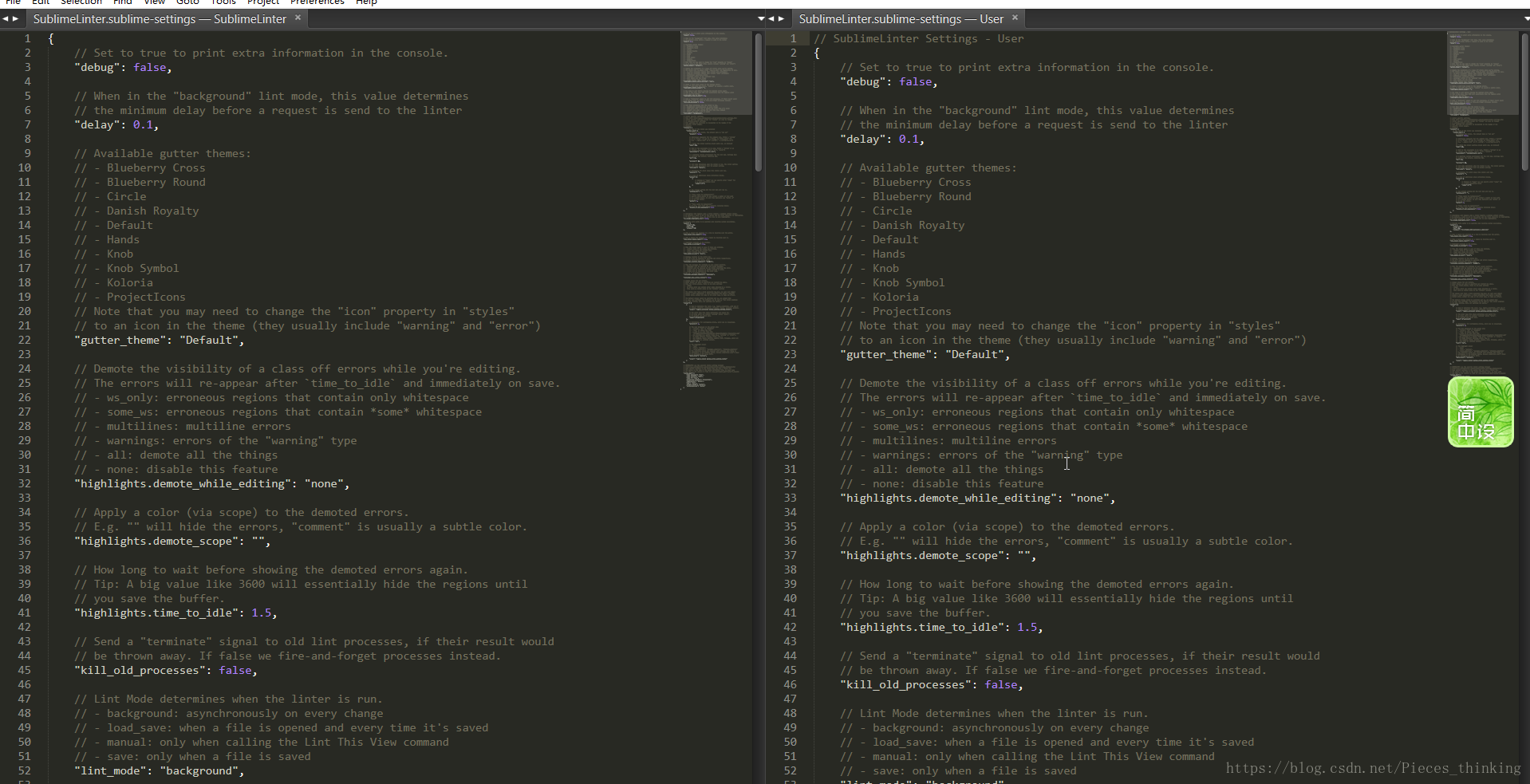

cyggcc_s-seh-1.dll进入sublime,打开菜单栏 tool->SublimeLinter->Open Settings

在右边用户设置里找下面的函数,windows的路径改成你自己安装verilator的路径。

PS:这一步SB3设置路径在这

需要把左边的系统设置全部拷贝到右边

然后在右边这里设置下路径(注意:路径是里 “/” 不是 “\” ,否则会报错)

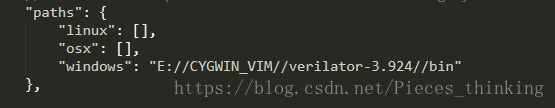

"paths": {

"linux": [],

"osx": [],

"windows": "E:/app/verilator-3.918/bin"

},这样,SublimeLinter就能找到verilator了。

使用F1可显示语法错误地点和原因。报错是实时的。

如果你有更好的美化方法,请告知。。。人多力量大。。。

6、gutter主题(根据喜好自己选)

切换语法报错提示图标样式

进入sublime,打开菜单栏 tool->SublimeLinter->Choose Gutter Theme 自己选吧。

7、卸载原有编辑器 =。=

华丽的分割线

接下来的部分持续更新中…

8、部分插件的安装

常见的插件安装,网上大把教程

- 1 sidebarenhancements

对于sidebarenhancements这个强大的插件比较复杂,所以另开一篇进行说明,详情请移步:https://blog.csdn.net/Pieces_thinking/article/details/81974784

- 2 sublime安装ctags函数追踪插件

详情请移步 https://www.cnblogs.com/you-jia/p/7550023.html

1535

1535

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?