未经允许,本文禁止转载

目录

简介

本文简要介绍xilinx 7系的AXI quad spi IP核的使用,主要用于读写boot用的flash(n25q128为例)做在线升级用。本文会略去很多细节,主要是因为我也没有搞得很懂,其次是很多细节可以在其他博客找到介绍。目前为止,我只尝试了使用axi lite接口配置寄存器,对flash读id,读数据,擦除扇区,写数据。后期会学习如何对flash进行分区管理,做升级备份以及针对不同flash加入quad的读写命令提高速率。

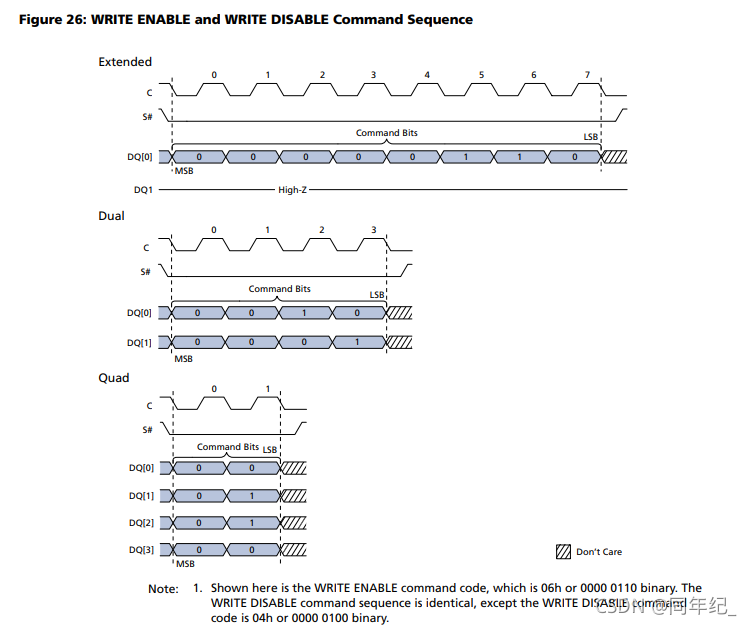

串行flash通常指spi flash,有standard,dual,quad三种,flash的操作就是发送命令,发送地址(可选),写数据/读数据(可选)。各种模式间的区分主要在于传输数据在数据线上的分布。这里我描述不清楚,细节暂且略过。

AXI Quad SPI IP设置

手册pg153介绍了该ip的寄存器含义,在第五章节Example Programming Sequence介绍了几种flash操作方式的寄存器写顺序。IP配置中,XIP(eXecute In Place)即芯片内执行,指应用程序可以直接在flash闪存内运行,就是说提供一个memory map的操作接口让CPU直接访问地址,就像访问内存一样,而不是发送flash的cmd命令,相当于是flash里再集成了一个控制器,把读地址命令转换为各种读时序。注意XIP只能读flash。这里我用不上不勾选。勾选performance Mode就能有AXI4接口支持突发,目前也不需要。配置IP为quad模式,只有1个slave设备,设备类型是混合的,支持winbond,micron,spansion,macronix共有的命令。如果勾选Micron,就能支持micron的特殊命令,否则发送它的特殊命令,IPISR状态寄存器就会报command error。FIFO深度只有16和256两种选择。STARTUP原语勾选上后指SPI的clk就会从FPGA专用的CCLK引脚输出时钟。

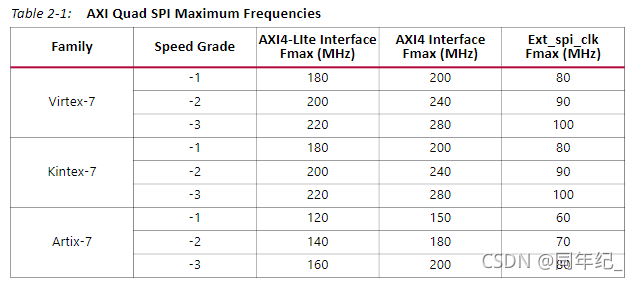

axi lite和spi的时钟频率在手册上有说明。spi_clk是操作flash clk的2倍,这个频率也要受到flash器件的约束。STARTUP_IO不用接,SPI_IO输出后用IOBUF引出到inout管脚即可,也可以自己写三态控制,spi_io0_t = 1时输出高阻。

寄存器说明

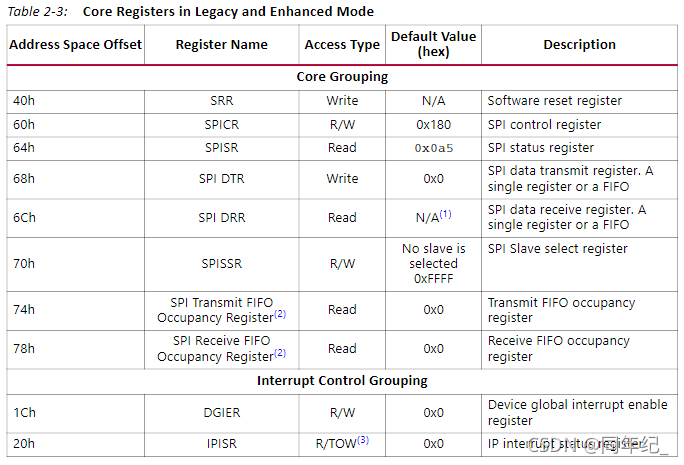

寄存器说明在pg153的第二章节Register Space。主要寄存器如下。

该IP的操作原理就是,先配置SPI为master,配置相位/极性,复位fifo,禁止传输;再把命令和数据写到SPI_DTR寄存器里,再使能设备片选,使能传输,关闭片选,关闭传输;从SPI_DRR里读取出数据(可选)。此外可以配置中断,选择使能哪些中断,再打开全局中断使能,传输完后查询IPISR就知道当前传输有没有错误。

40h:复位寄存器,写0xa复位整个IP,自动解复位。

60h:控制寄存器,控制SPI的工作方式。

64h:状态寄存器,查看fifo是否空满,用来判断是否传输结束。

68h:发送fifo,往里面写数据,写满了会覆盖。所以不要写满。

6ch:接收fifo,接收满了会自动丢弃后续数据。

70h:片选,写

本文详细介绍如何在Xilinx 7系列FPGA中使用AXIQuadSPI IP进行Boot flash(如N25Q128)的读写操作,包括设置步骤、寄存器理解、通用命令应用、读ID、读写数据、擦除扇区和写入数据的详细示例。还讨论了注意事项和远程升级策略。

本文详细介绍如何在Xilinx 7系列FPGA中使用AXIQuadSPI IP进行Boot flash(如N25Q128)的读写操作,包括设置步骤、寄存器理解、通用命令应用、读ID、读写数据、擦除扇区和写入数据的详细示例。还讨论了注意事项和远程升级策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

102

102

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?