根据快速幂的思想

b=(b1*1+b2*2+b3*4...+bn*2^n-1)

res=a*(b1*1+b2*2+...)

#include <iostream>

#include <algorithm>

using namespace std;

typedef long long ll;

int main()

{

ll a,b,p;

cin>>a>>b>>p;

ll res=0;

while(b)

{

if(b&1)

{

res=(res+a)%p;

}

b>>=1;

a=a*2%p;

}

cout<<res%p;

return 0;

}应用模的定义出发

由于 a%b=a-(a/p)*p (a/b是下取整)

那么 a*b%p=a*b-(a*b/p)*p

a*b和(a*b/p)*p 的差一定是在 0~p-1 之间的

如果res=a*b%p <0 res+=p;

res>=p res-=p;

#include <iostream>

#include <algorithm>

using namespace std;

typedef long long ll;

int main()

{

ll a,b,p;

cin>>a>>b>>p;

ll c=(long double)a*b/p;

ll res=a*b-c*p;

if(res<0) res+=p;

else if (res>=p) res-=p;

cout<<res;

return 0;

}

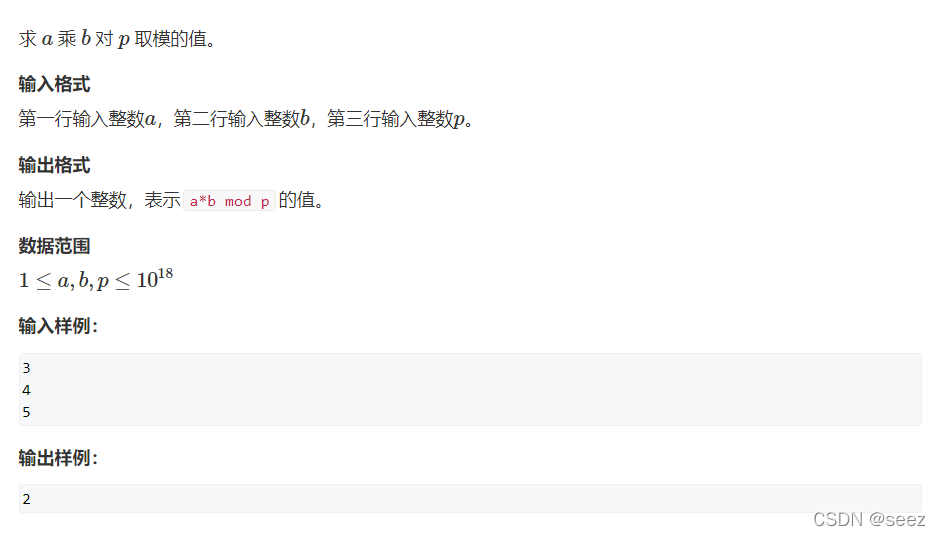

本文介绍了快速幂算法的两种实现方式:一种是通过位运算逐步计算幂的结果并取模,另一种是利用模的定义来简化计算过程。这两种方法都能有效地解决大数幂运算的问题。

本文介绍了快速幂算法的两种实现方式:一种是通过位运算逐步计算幂的结果并取模,另一种是利用模的定义来简化计算过程。这两种方法都能有效地解决大数幂运算的问题。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?