前天去面试,问到了这个问题,在回答这个问题的时候,面试官说我理解的有此问题,其实还问到了对于中断和异常的理解,现在整理一点资料出来,全当是复习吧。

1.什么是异常,什么是中断?

说法一:

中断的描述主体是外设,而异常的描述主体是CPU。

中断是一个过程,是CPU在执行当前的程序的过程中因硬件或软件的原因插入了另一段程序运行的过程。

异常主要是从CPU角度,接受信号的。

中断主要是从外设角度,向CPU发送信号。

说法二:

异常是中断的一种,异常非为中断异常(IRQ/FIQ)和非中断异常(SVC/Undefine/Abort)

个人觉得,说法二应该是更专业和更好的理解,不过,面试官说应该是说法一,由于对于这两种理解,我问了一些做驱动的朋友,他们说法大多也是出自这两种,没有定论,那就两种都上,还是按个人理解,取第二种说法吧。

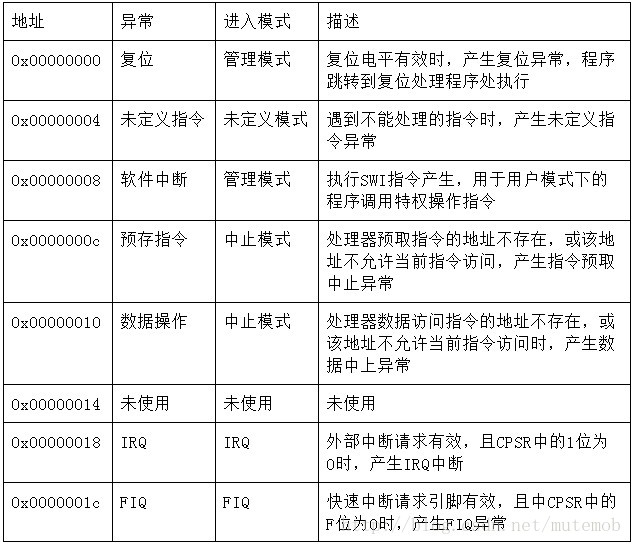

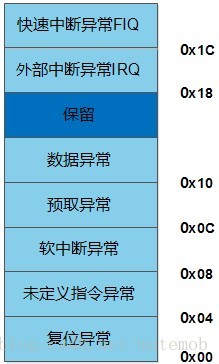

2.ARM异常种类及对应的处理器模式

ARM体系结构中存在7种异常处理。异常发生时,处理器会把PC指向一个特殊地址,这个地址放在存储器中一个特定表中,称为异常向量表

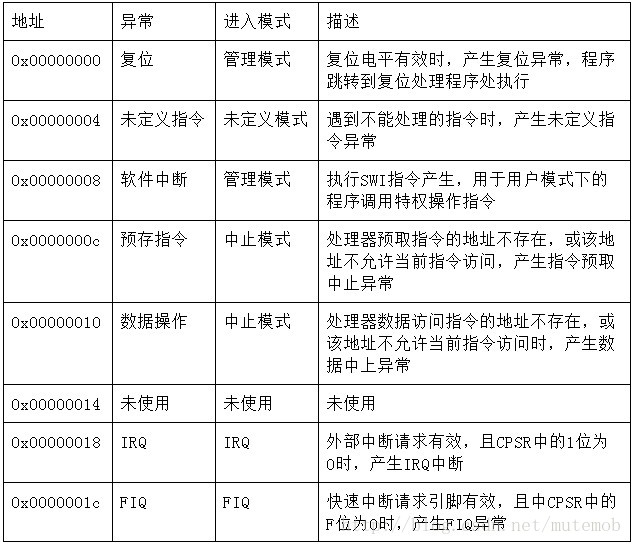

画个更直观的图来看一下

画个更直观的图来看一下

低地址向量表(从0x00000000开始) --裸板

高地址向量表(从0xFFFF0000开始) --带操作系统

5种异常:

中断异常:IRQ/FIQ

非中断异常:SVC/Undefine/Abort

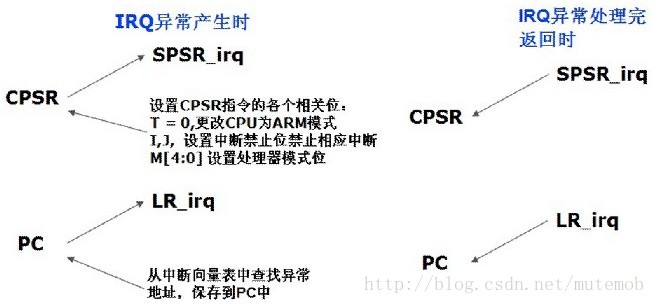

3.异常发生时的CPU处理步骤

(1)保存当前执行位置(将当前执行位置存入到R14--LR寄存器中)

(2)保存当前执行状态(状态保存到CPSR中)

(3)寻找中断入口,即向量表地址(PC寄存器中加入东西)

(4)执行中断处理程序

(5)中断返回,继续执行

思考一下:上面这两大步究竟是在干什么?为什么要CPSR拷到SPSR,PC拷到LR_IRQ?为什么做这两步?

CPSR-->SPSR 保存要执行哪条机器码(要干什么?)

PC-->LR 保存要在哪里执行(在哪里执行?)

其实想透了非常简单,为什么要这些什么CPSR,SPSR,LR,PC搞这么一堆寄存器,目的其实只有一个----知道要在哪里干什么,SPSR中保存的是中断的的机器码,而LR_irq或LR_fiq中保存要执行的地址,这样返回的时候,就知道我要在哪个位置执行异常产生前的机器码了,仅此而已。抛开计算机这个东西,这个设计的原理其实是很简单的,不过多了几个英文缩写的名称的寄存器名字来吓人而已。

其实想透了非常简单,为什么要这些什么CPSR,SPSR,LR,PC搞这么一堆寄存器,目的其实只有一个----知道要在哪里干什么,SPSR中保存的是中断的的机器码,而LR_irq或LR_fiq中保存要执行的地址,这样返回的时候,就知道我要在哪个位置执行异常产生前的机器码了,仅此而已。抛开计算机这个东西,这个设计的原理其实是很简单的,不过多了几个英文缩写的名称的寄存器名字来吓人而已。

当异常产生时,ARM Core:

1)拷贝CPSR到SPSR<mode>

2)设置适当的CPSR位

3)保存返回地址到LR_<mode>

4)设置PC为相应的异常向量地址

返回时,异常处理需要:

1)从SPSR_<mode>恢复CPSR

2)从LR_<mode>恢复PC

在以前的ARMCPU,如ARM720和ARM9/10中,中断向量表的基地址只是0x00000000或是0xFFFF0000,在新的ARM11和Cotrex系列中,中断向量表可以自行设置任意的基地址。

4.FIQ和IRQ

为什么FIQ叫快速中断?

1)FIQ在中断向量表中牌向量表的最末端(最上面),基本上可以不用再跳转一次,就可以从异常地址处执行(少一层跳转指令,就少了一次流水线的重新填充周期)

2)FIQ的CPU模式拥有独立的R8--R12寄存器,其他的中断模式都必须先保存别人的,用完后再恢复,而FIQ可以使用自己的私有寄存器,当然就更快一些。

这其中有三级流水线刷新的一些问题,网上有很多的资料,喜欢研究的,可以去看《大话处理器》里面图文并茂,讲的非常清楚,面了一段时间,被问到了各种各样的问题,不断的补充与加强吧,转型不容易,选择了转型,那就坚持下去。

3053

3053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?