目录

前言

简要整理本书部分章节内容,详细内容可以参考阅读原著《Xilinx FPGA开发实用教程--田耘 著》!

原语查找:

altera 的在 quartus 界面的 help -- help_topics -- primitives 里

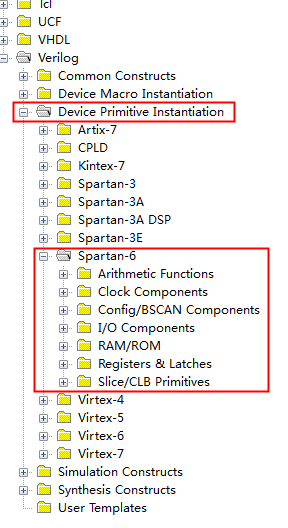

xilinx 的在 vivado 界面的 tools -- language_templates -- verilog -- device_primitive_instantiation

xilinx ise 界面的 edit -- language_templates -- verilog

1、Xilinx 原语简介

Xilinx 提供的原语涵盖了FPGA 开发常用领域,但只有相应配置的硬件才能执行相应的原语, 并不是所有的原语都能在任意一款芯片上运行。

本节以Virtex-4平台介绍各类原语。

原语按功能分类,主要分为:

- 计算组件原语;

- I/O端口组件原语;

- 寄存器和锁存器原语;

- 时钟组件原语;

- 处理器组件原语;

- 移位寄存器原语;

- 配置和检查组件原语;

- RAM/ROM组件原语;

- Slice/CLB组件原语;

- 吉比特收发器组件原语;

1.1 时钟组件原语(Clock Components)

时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通I/O本地的时钟缓冲器,以及高级数字时钟管理模块。

| 原语名 | 描述 |

| BUFG | 全局时钟缓冲器 |

| BUFGCE | 全局时钟复用器,附带时钟使能信号和0状态输出 |

| BUFGCE_1 | 全局时钟复用缓冲器,附带时钟使能信号和1状态输出 |

| BUFGCTRL | 全局时钟复用缓冲器 |

| BUFGMUX | 全局时钟复用缓冲器,附带时钟使能信号和0状态输出 |

| BUFMUX_1 | 全局时钟复用器,附带0状态输出 |

| BUFGMUX_VIRTEX4 | Virtex-4期间特有的全局时钟复用缓冲器 |

| BUFIO | I/O端口本地时钟缓冲器 |

| BUFR | I/O端口和CLB的本地时钟缓冲器 |

| DCM_ADV | 带有高级特性的数字时钟管理模块 |

| DCM_BASE | 带有基本特征的数字时钟管理模块 |

| DCM_PS | 带有基本特征和移相特征的数字时钟管理模块 |

| PMCD | 匹配相位时钟分频器 |

对几个常用时钟组件进行简单介绍。

1.1.1 BUFG

BUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用。全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连接到时钟抖动可以忽略不计的全局时钟网络。BUFG组件可以应用与典型的高扇出信号和网络,如复位信号和时钟使能信号。如果要对全局时钟实现PLL或DCM等时钟管理,需要手动例化该缓冲器。

1.1.2 BUFGMUX

1.2 I/O端口组件(IO Components)

I/O组件提供:

- 本地时钟缓存;

- 标准单端I/O缓存;

- 差分I/O信号缓存;

- DDR专用I/O信号缓存;

- 可变抽头延迟链;

- 上拉;

- 下拉;

- 单端信号和差分信号互相转换;

| 原语 | 描述 |

| BUFIO | I/O的本地时钟缓存 |

| DCIRESER | FPGA配置成功后,DCI状态机的复位信号 |

| IBUF | 标准和容量可选I/O单端输入缓存 |

| IBUFDS | 带可选择端口的差分信号输入缓存 |

| IBUFG | 带可选择端口的专用输入缓存 |

| IBUFGDS | 带可选择端口的专用差分信号输入缓存 |

| IDDR | 用于接收外部DDR输入信号的专用输入寄存器 |

| IDELAY | 专用的可变抽头输入延迟链 |

| IDELAYCTRL | IDELAY抽头数的控制模块 |

| IOBUF | 带可选择端口的双向缓存 |

| IOBUFDS | 低有效输出的三态差分信号I/O缓存 |

| ISERDES | 专用I/O缓存的输入分解器 |

| KEEPER | KEEPER符号 |

| OBUF | 单端输出端口缓存 |

| OBUFT | 带可选择端口的低有效输出的三态输出缓冲 |

| OBUFDS | 带可选择端口的差分信号输出缓冲 |

| OBUFTDS | 带可选择端口的低有效输出的三态差分输出缓冲 |

| ODDR | 用于向外部DDR发送信号的专用输出寄存器 |

| OSERDES | 用于快速实现输入源同步接口 |

| PULLDOWN | 输入端寄存器下拉至0 |

| PULLUP | 输入端寄存器、开路以及三条输出端口上拉至Vcc |

1.2.1 BUFIO

1.2.2 IBUFDS

| 作者 | 博文 |

| 1、sazczmh | XILINX 7系列FPGA_SelectIO篇 |

| xilinx原语的使用方法 | |

| Xilinx原语的使用方法2 | |

| 2、李锐博恩 | ODDR使用研究记录 |

| Buffer专题介绍(一) | |

| Buffer专题介绍(二) | |

| Buffer专题介绍(三) | |

469

469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?