Si5324是Silicon Labs公司的一款任意频率时钟发生芯片。基于Silicon Labs的DSPLL技术,可以从任何输入频率产生无限组合的低抖动输出频率,Si53xx系列的芯片好像都是这种类似的功能。

图1. DSPLL®模块图解

Si5324有很多寄存器,要正确的使用它就得配置这些寄存器,它的控制模式有IIC和SPI两种,我程序里面用的是模拟IIC,IIC通信协议网上一找全都是,所以协议我就不多说了。图1左下角的信号检测模块包含信号丢失报警(LOS)、频率偏置报警(FOS)和PLL是否锁定标志,都可以通过寄存器来设置是否开启警报或读取警报状态,更详细的内容可以参考下面资源链接里面的数据手册。

刚开始使用IIC与Si5324通信时总是失败,依照格式先是一行IIC产生起始信号函数i2c_start(),紧接着再发送一个字节的器件写地址i2c_SendByte(0xd0),然后等待应答信号i2c_WaitAck(),但这里总是显示的从器件无应答,这就表明Si5324就像个高冷的小姐姐一样,你想搭理她她却不理你,出现这种情况就不能再继续下去了,要找出到底是自身的原因还是对方的原因。

首先便是用示波器观测IIC的时钟线SCL和数据线SDA的时序是否按照预想的进行,起始信号和要发送的字节都没问题,说明模拟IIC的底层函数写的没问题,然后仔细查看板子的原理图和芯片数据手册,发现了原理图上Si5324有个复位引脚经上拉电阻后接入了MCU。既然如此,那就在通信之前加个复位函数,将其复位引脚拉低一段时间后再拉高(刚开始复位时傻逼了,拉低之后就不管了,导致芯片一直处于复位状态,又找了好久的原因)。进行完复位操作后应该是万事大吉了,发送器件写地址过去后是有回应了,但见了鬼的是紧接着发送一个字节的寄存器地址过去后又没回应了。真特么的是走一步卡一步,难道回去养猪才是正道么。

后来用万用表检测Si5324芯片的几个VDD和GND引脚时发现有个重要的地线板子上面没连上,给我的原理图和PCB文件上显示的是接上了的,但那个小老弟解释道可能是最后一次修改后投去做板的文件是没有保存的文件,真是一波令人窒息的骚操作。通过飞线解决后一切正常,可以与Si5324通信了,想写就写想读就读,真好。

图2. Si5324 IIC读写命令格式

图2还是不难理解的,依照格式来就能读写指定的寄存器,寄存器地址和寄存器里面各位代表的功能数据手册里面有详细介绍,图中还说明了芯片的寄存器地址是自动增加的,也就是说先写了一个寄存器之后,地址自动加一,可以不断的写数据,感觉这功能没啥用。

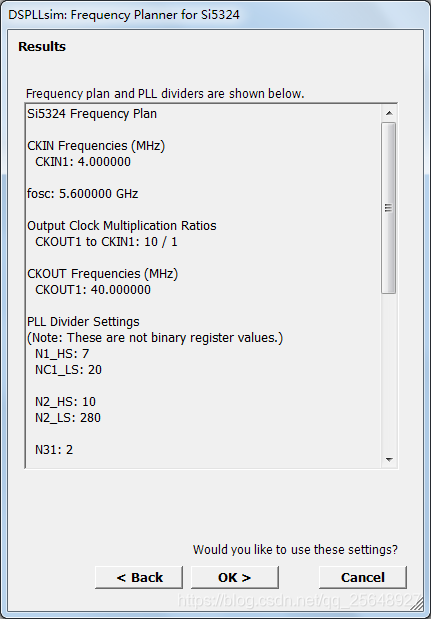

接下来便是要仔细研究数据手册中的各个寄存器描述了,配置寄存器时最主要的还是设置其各项分频参数,可以利用Silicon Labs公司的DSPLLsim软件快速得到各项分频值,然后在程序里面利用IIC写入对应分频寄存器的值便可完成分频配置。图3图4便是DSPLLsim的软件预配置界面(软件是他们开发板的配套软件,我们只需用它来获取各个分频系数即可),图4中PLL Divider Settings下面的几个参数便是分频系数,这里设置的是CKIN1输入4MHz,CKOUT1输出40MHz。软件可以从Silicon Labs官网下载,下面的资源链接里面也有。

配置完成后既可以读取其中几个指示状态的寄存器来获取芯片运行时的状态信息,例如通过读取寄存器130的值来获取PLL是否处于锁定状态。注意不要在配置完后立即读取状态信息,我一开始是配置完后直接读取寄存器130的值来得知PLL是否锁定,结果一直显示的是未锁定状态,还以为配置出了问题,后来发现PLL从失锁进入锁定状态需要一定的时间,立即读取的话肯定是显示未锁定状态。

配套资源链接:https://download.csdn.net/download/qq_25648927/10770209

2722

2722

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?