系统:win10

软件编辑和程序下载平台:Quartus II

仿真平台:modelsim

FPGA:EP4CE6

实验仿真结果

设计思路:

由于是程序员,所以结构要清晰,操作要骚

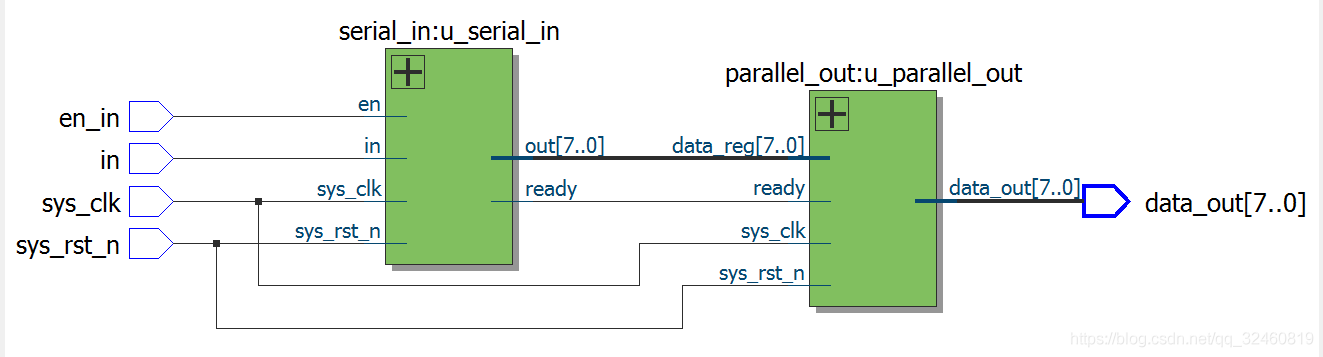

首先创建三个个块

块1 serial_in

目的:

实现串口输入.将输入的数据保存到八位寄存器中,每次连续输入8位后,

再一次性将八位分别在并行端口的八位对应输出

模块2

并行输出

模块3

顶层模块例化

下面是代码

模块1serial_in

/*

该程序串行输入并进行转换为并行,保存到8位寄存器 out中

输入:

时钟,复位,

串行输入使能

串行输入

输出:

并行输出

并行输出使能

*/

`define bit0 8

module serial_in(

input sys_clk,

input sys_rst_n, //系统复位,低电平有效

input in, //串行输入

output reg [`bit0 - 1:0] out, //并行输出

output reg ready //高电平有效_输出使能

);

reg [2:0] i; //用于计数

reg en; //高电平有效

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)begin //复位初始化

out <= `bit0'b0000_0000;

i <= 3'd0;

ready <= 1'b0;

en <= 1'b1; //使能输入

end

else if(en) begin

out <= {out[`bit0-2 : 0], in}; //相当于左移一位

// out <= {out, in}; //相当于左移一位

i <= i + 1'b1;

if(i == 3'd7) //已经传来了8位数据, 此时out寄存器已满, 使能输出ready

ready <= 1;

else

ready <= 0;

end

else begin //没有使能

out <= out;

i <= 3'd0;

ready <= 0;

end

end

endmodule

模块2 parallel_out

`define bit0 8

module parallel_out(

input sys_clk,

input sys_rst_n, //系统复位,低电平有效

input ready, //并行输入使能

input [`bit0 - 1:0] data_reg, //并行输入

output reg[`bit0 - 1:0] data_out

// output reg en_out //高电平有效_输出使能

);

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n) begin

data_out <= `bit0'b0000_0000;

// en_out <= 1'b0;

end

else if(ready) begin

data_out <= data_reg;

// en_out <= 1'b1; //输出使能

end

else begin

data_out <= data_out;

// en_out <= 1'b0;

end

end

endmodule

模块3 例化代码

`define bit0 8

module top_serial_to_parallel_8bit(

input sys_clk,

input sys_rst_n, //系统复位,低电平有效

input en_in, //串行输入使能

input in, //串行输入

output [`bit0 - 1:0] data_out //并行输出

);

wire [`bit0 - 1:0] out_reg;

wire ready;

serial_in u_serial_in(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n), //系统复位,低电平有效

// .en (en_in), //IO输入使能,高电平有效

.in (in), //串行输入

.out (out_reg), //并行输出

.ready (ready) //高电平有效_输出使能

);

parallel_out u_parallel_out(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n ), //系统复位,低电平有效

.ready (ready), //并行输入使能

.data_reg (out_reg), //并行输入

.data_out (data_out) //并行输出

// .en_out (en_out)

);

endmodule

/*

移位一般是要有时钟做同步的,也就是说,n个时钟采样到的串行数据需要在n个时钟周期后以并行方式输出,这是最基本的传入并出设计思想,对于串行接口大行其道的高速传输领域,这种简单的转换也是接口芯片的重要任务之一,但从FPGA的角度来看,串并转换又有着更深的意义,串并转换正是面积换速度思想的体现。

*/

仿真代码

`timescale 1 ns/ 1 ns

module top_serial_to_parallel_8bit_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

//输入

reg in;

reg sys_clk;

reg sys_rst_n;

// wires

//输出

wire [7:0] data_out;

// assign statements (if any)

top_serial_to_parallel_8bit i1 (

.data_out(data_out),

.in(in),

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n)

);

reg [31:0] i;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

i = 1'b0;

#10 sys_rst_n = 1'b1; //延时100ns 复位信号拉高

#5000 $stop;

end

always #10 sys_clk = ~sys_clk; //延时10ns反转 50MHz

always @ (posedge sys_clk or negedge sys_rst_n)begin

if(i%10==0 || i%3==0 )begin

in <= 1;

i <= i+1'b1;

end

else if(i>99)

i <= 32'b0;

else begin

i <= i+1'b1;

in <= 0;

end

end

endmodule

仿真结果图

见第一个图

注意:

问题

该程序有一个问题是串行并行转换总会延迟1个时钟周期, 程序还是有点问题,待我干掉这个bug

3230

3230

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?