由于该系列文章阅读有顺序性,所以请跳转至该系列文章第一篇从头开始阅读,并按照文章末尾指示按顺序阅读,否则会云里雾里,传送门在此: https://blog.csdn.net/qq_33486907/article/details/89380368 《TIMING_01 时序约束与时序分析》

目录

1.输入延迟约束

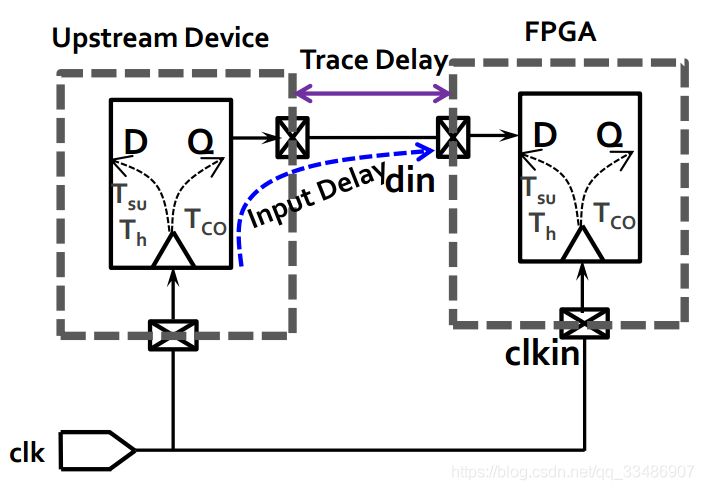

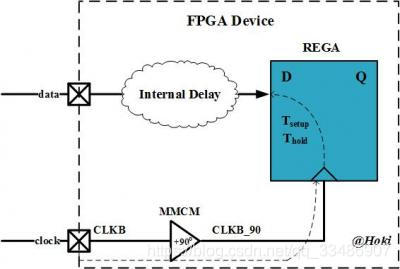

输入延迟约束用于告诉VIVADO FPGA上游器件的时序性能参数,FPGA结合自身内部的时序性能参数即可获得这条时序路径的分析结果,如图:

约束如下:

情况1:没有最大最小延迟的情况

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

set_input_delay –clock clk 4 [get_ports din]

情况2:有最大最小延迟的情况

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

set_input_delay -clock clk -max number [get_ports din]

set_input_delay -clock clk -min number [get_ports din]

对于延时时间参数的计算方式和系统同步方式有关,接下来分别介绍。

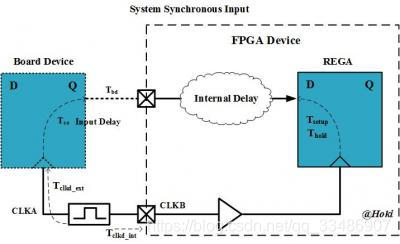

1.1 同步方式 之 系统同步

分析输入端口到FPGA内部时序单元的路径时,当source clock和destination clock来自同一个系统时钟时,称为系统同步输入(system synchronous input);

source clock是CLKA,destination clock是CLKB,其中CLKB通过输入端口引入FPGA内部(约束成主时钟),而CLKA引到了FPGA外部的板上芯片,并没有引入到FPGA内部,CLKB是采集输入端口的时钟,因此首先约束CLKB为主时钟。

Tclkd_ext:表示外部时钟源到外部芯片的延时;

Tclkd_int:表示外部时钟源到FPGA输入端口的延时;

Tco:表示外部芯片Tco时间;

Tbd:表示外部芯片输出端口到FPGA芯片的板上延时。

通用公式如下:

max_input_delay = Tclkd_ext_max + Tco_max + Tbd_max – Tclkd_int_min

min_input_delay = Tclkd_ext_min + Tco_min + Tbd_min – Tclkd_int_max

通常在硬件设计时会将外部时钟源到FPGA管脚和到外部芯片时钟管脚做等长处理,即可认为Tclkd_ext == Tclkd_int,可以将公式简化为:

max_input_delay = Tco_max + Tbd_max

min_input_delay = Tco_min + Tbd_min

做约束时只需关注上游芯片的Tco时间和传输线延迟时间即可,但前提是时钟线做了等长处理;

Tco时间一般由上游器件的器件手册或时序图得到,传输线延迟时间Tbd则是根据实际PCB布线的长度来获得的。

对于Tbd的最大最小值的得来,如果约束的对象是单比特数据线,那么自然Tbd只存在一个值;但如果约束的是多比特数据总线,那么在不做到绝对等长的情况下,走线肯定存在长短,也就有了最大和最小的延迟时间;

系统同步接口(System Synchronous Interface)的构建相对容易,以 FPGA 做接收侧来举例,上游器件仅仅传递数据信号到 FPGA 中,时钟信号则完全依靠系统板级来同步。时钟信号在系统级上同源,板级走线的延时也要对齐。正因为这样的设计,决定了数据传递的性能受到时钟在系统级的走线延时和 skew 以及数据路径延时的双重限制,无法达到更高速的设计要求,所以大部分情况也仅仅应用 SDR 方式。

1.1.1 传输线延迟的计算方式

这里单独给出一个章节,用于讲解传输线延迟的计算方法:

“信号速度还与不同材料的介电常数相关,具体计算公式是 V=C/Er0.5 ,其中Er是信号线周围材料的相对介电常数。我们常见的PCB材料Fr4的介电常数在4.2-4.5左右,为了计算方便我们取4。带入公式可以算出,Fr4材料制作的PCB板上面信号的传输速度是光速的二分之一。光速大约等于12inch/ns,计算得出Fr4板上信号速度大约是6inch/ns。换算成延时,也就是166ps/inch。这就是我们经常说的PCB板上信号延时大约是166ps/inch。”

Tbd = lenth mil * 166ps/inch / 10^6 = num ns 使用这个公式即可得出传输线的延迟时间;

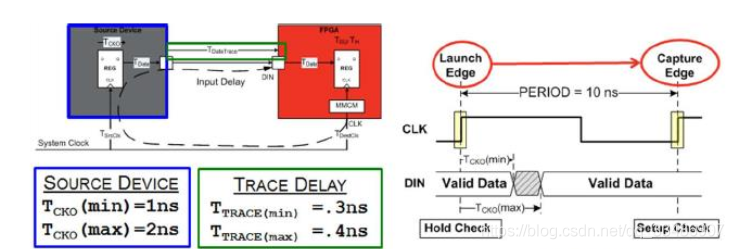

1.1.2 系统同步约束案例

如图所示:假设时钟信号在板级做等长处理,那么可以采用简化的延迟时间计算公式:

max_input_delay = Tco_max + Tbd_max = 2 + 0.4 = 2.4ns

min_input_delay = Tco_min + Tbd_min = 1 + 0.3 = 1.3ns

然后就可以对input 做出如下约束:

第一步约束主时钟:

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

第二步输入端口延迟约束:

set_input_delay -clock clk -max 2.4 [get_ports din]

set_input_delay -clock clk -min 1.3 [get_ports din]

这样就完成一个对系统同步输入端口的延迟约束; 如果始终信号在板级没有做等长处理则就需要考虑时钟的歪斜带来的延迟。

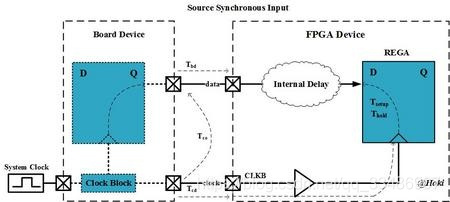

1.2 同步方式 之 源同步方式

分析输入端口到FPGA内部时序单元的路径时,当destination clock来自外部芯片,即与数据输入同源,称为源同步输入(source synchronous input)。

Tcd:表示外部芯片时钟输出到FPGA输入端口的延时;

Tco:表示外部芯片Tco时间;

Tbd:表示外部芯片输出端口到FPGA芯片的板上延时;

max_input_delay = Tbd_max + Tco_max - Tcd_min

min_input_delay = Tbd_min + Tco_min - Tcd_max

通常在硬件设计时会将随路时钟和数据线进行等长处理,即Tbd = Tcd,即可得出简化的延迟时间计算公式:

max_input_delay = Tco_max

min_input_delay = Tco_min

做约束时只需关注上游芯片的Tco时间即可,但前提是时钟线做了等长处理;

源同步相对于系统同步更为复杂一些,由于时钟和与数据的相位关系,分为边缘对齐和中心对齐两种;然后数据采集的方式又分为两种SDR和DDR两种情况,下面分两种方式来对约束进行讲解。

1.2.1 SDR

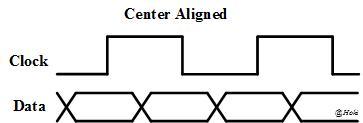

(1)Center Aligned 中心对齐

中心对齐是指时钟和数据到达后级时序单元时,时钟沿在数据中心,在这种情况下可以直接使用时钟采集数据。

中心对齐输入延迟约束案例:

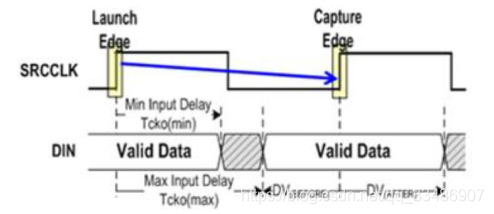

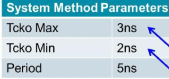

如图所示,假设时钟和数据走线做了等长处理,其中:

Tcko max = max_input_delay = Tco_max = 3ns

Tcko min = min_input_delay = Tco_min = 2ns

然后就可以对input 做出如下约束:

第一步约束随路时钟:

create_clock -period 5.000 -name SRCCLK -waveform {0.000 2.500} [get_ports SRCCLK]

源同步所约束的源时钟一定是随路时钟,这里一定要注意;

第二步输入端口延迟约束:

set_input_delay -clock SRCCLK -max 3 [get_ports din]

set_input_delay -clock SRCCLK -min 2 [get_ports din

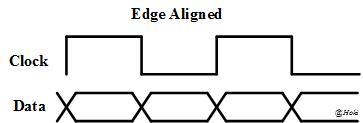

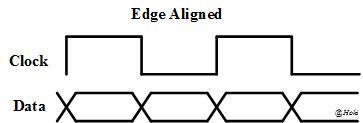

(2)Edge Aligned 边沿对齐

边缘对齐是指时钟和数据到达后级时序单元时,时钟沿与数据变化沿重合,如图所示,由于是随路时钟的关系,时钟和数据极有可能同时达到FPGA的输入端口,这样很明显不能满足目的端寄存器的时序要求,通常的做法是通过逻辑或锁相环对时钟和数据的关系进行相位调整,这样就能正确采集数据了,之后在以调整后的相位进行时序约束即可;

边缘对齐输入延迟约束案例:

如图所示,数据data和时钟Clock的关系是边缘对齐,案例中使用MMCM将随路时钟相移了90°,使数据和采样时钟的关系变成了中心对齐,因此可以得到如下约束:

第一步约束随路时钟:

create_clock -period clk_period -name CLKB –waveform {0.000 clk_period/2} [get_ports {CLKB}]

第二步约束随路时钟的生成时钟:

create_generated_clock -name CLKB_90 -source [get_clocks CLKB] -phase 90 [get_pins{MMCM|co[0]}] //该约束仅仅适用于Altera,不适用于XILINX

第三步输入端口延迟约束:

set_input_delay -clock SRCCLK -max max_input_delay [get_ports data]

set_input_delay -clock SRCCLK -min min_input_delay [get_ports data]

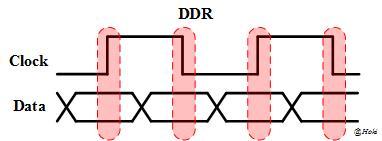

1.2.2 DDR

(1)Center Aligned 中心对齐

如图所示,DDR的中心对齐;

这里直接给出案例来讲解约束的方法,如图所示:

第一步约束随路时钟:

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

第二步输入端口延迟约束:

set_input_delay -clock clk -max 4.3 [get_ports data]

(max = period/2 – dv_bfe)

set_input_delay -clock clk -min 0.6 [get_ports data]

set_input_delay -clock clk -max 4.6 [get_ports data] –clock_fall –add_delay

(max = period/2 – dv_bre)

set_input_delay -clock clk –min 0.2 [get_ports data] –clock_fall –add_delay

(2)Edge Aligned 边沿对齐

边沿对齐的情况,可通过如下约束:

第一步约束随路时钟:

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

第二步输入端口延迟约束:

set_input_delay -clock clk -max 0.4 [get_ports data]

set_input_delay -clock clk -min -0.6 [get_ports data]

set_input_delay -clock clk -max 0.7 [get_ports data] –clock_fall –add_delay

set_input_delay -clock clk –min -0.3 [get_ports data] –clock_fall –add_delay

通常这样约束以后也很难达到理想的效果,一般采用和SDR中边沿对齐的方式相同,将时钟经过一个MMCM/PLL 做一定的相移,从而把边沿对齐变成中心对齐,然后使用相移的时钟进行采样和约束;

本系列博客对应的完整《时序约束手册》传送在此,点击下方下载链接一:

https://download.csdn.net/download/qq_33486907/19846182

或点击下载链接二:https://item.taobao.com/item.htm?spm=a1z38n.10677092.0.0.22131debncNwzA&id=588531553802

推荐使用链接一,链接二即将停止服务

179

179

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?