转自https://zhuanlan.zhihu.com/p/678582210

0. 目录

-

垫话

-

extended xAPIC(x2APIC)[10.12]

2.1 检测及使能 x2APIC 模式[10.12.1]

2.1.1 访问 APIC 寄存器的指令[10.12.1.1]

2.1.2 x2APIC 寄存器地址空间[10.12.1.2]

2.1.3 保留 bit 检查[10.12.1.3]

2.2 x2APIC register 可用性[10.12.2]

2.3 x2APIC 模式下的 MSR 访问[10.12.3]

2.4 MSR 及 x2APIC 寄存器的 VM-Exit 控制[10.12.4]

2.5 x2APIC 状态转换[10.12.5]

2.5.1 x2APIC 状态[10.12.5.1]

2.6 x2APIC 模式下的设备中断路由[10.12.6]

2.7 系统软件的 x2APIC 初始化[10.12.7]

2.8 CPUID 扩展及拓扑枚举[10.12.8]

2.8.1 APIC ID 与 CPUID 的一致性[10.12.8.1]

2.9 x2APIC 模式下的 ICR 操作[10.12.9]

2.10 x2APIC 模式下的 IPI 目标决议[10.12.10]

2.10.1 x2APIC 模式下的 logical destination 模式[10.12.10.1]

2.10.2 从 local x2APIC ID 到 logical x2APID ID[10.12.10.2]

2.11 Self IPI Register[10.12.11]

- 垫话

本文乃 Intel SDM “Chapter 10 Advanced Programmable Interrupt Controller(APIC)” 一章的翻译。

要点概述:

x2APIC 模式是 xAPIC 模式的扩展。主要改变有:接口从 MMIO 改成 MSR;local APIC ID 扩展到 32 bit;ICR 扩展到 64 bit,IPI 的 destination 域扩展到 32 bit;新增专门用于 self-interrupt 的寄存器。

2. extended xAPIC(x2APIC)[10.12]

x2APIC 架构是 xAPIC 架构(Section 10.4)的扩展,在向后兼容的基础上提供了面向未来 Intel 平台的向前扩展性。具体来说,x2APIC 架构做了下面这些事:

对 xAPIC 架构提供了兼容支持

— delivery mode

— interrupt 及 processor 优先级

— 中断源

— 中断目标类型

为 logical 和 physical destination 模式提供了处理器寻址扩展。

提供新的 feature 提升中断投递性能。

在 link based 平台架构上降低了 logical destination 模式中断投递的复杂性。

使用 MSR 来访问 x2APIc 模式下的 APIC 寄存器,而不是 MMIO。在 xAPIC 模式下时仍然支持 MMIO 接口。

2.1 检测及使能 x2APIC 模式[10.12.1]

发起 CPUID EAX = 1 并检查 ECX bit 21 可检测处理器对 x2APIC 模式的支持。如果 CPUID.(EAX = 1):ECX.21 是置上的则支持 x2APIC。

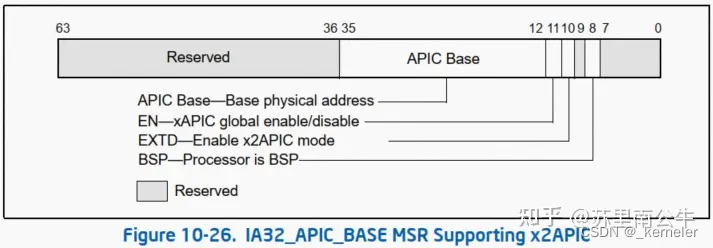

系统软件可以通过设置 IA32_APIC_BASE MSR(地址 01BH)中 x2APIC 模式 enable bit(bit 10) 来将 APIC 切换为 x2APIC 模式。Figure 10-26 是 IA32_APIC_BASE_MSR 的布局:

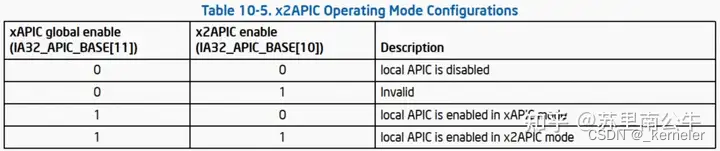

Table 10-5,“x2APIC operating mode configurations” 罗列了 IA32_APIC_BASE MSR enable bit(EN -bit 11) 及 extended mode bit(EXTD - bit10) 的可能组合。

将 local APIC 切换成 x2APIC 模式(EN = 1,EXTD = 1)之后,若要再切回 xAPIC 模式,需要系统软件先禁能 local APIC。具体来说,在 local APIC 使能且处于 x2APIC 模式时,对 IA32_APIC_BASE 写入 (EN = 1,EXTD = 0)将触发 general-protection 异常。一旦 IA32_APIC_BASE bit 10 置上,通过 IA32_APIC_BASE 退出 xAPIC 模式的唯一方法就是通过 WRMSR 将 bit 11 和 bit 10 都写 0。Section 10.12.5, “x2APIC State Transitions” 描述了 local APIC 状态转换的细节。

2.1.1 访问 APIC 寄存器的指令[10.12.1.1]

x2APIC 模式下,系统软件通过 RDMSR 及 WRMSR 来访问 APIC 寄存器。x2APIC 寄存器的 MSR 访问地址是 architecturally 定义的,见 Section 10.12.1.2,“x2APIC Register Address Space”。RDMSR 指令的执行需要通过 ECX 指定 APIC 寄存器地址,EAX 中是所返回 APIC 寄存器的 bits 0 到 31。EDX 中是所返回的 bits 32 到 63 —— 如果所读 APCI 寄存器是 32 bit 的则这些 bits 保留。WRMSR 的执行类似,ECX 指定 APIC 寄存器地址,将 EAX 中 bits 0 到 31 写入指定 APIC 寄存器的 bits 0 到 31。如果是 64 bit 寄存器,则将 EDX 的 bits 0 到 31 写入 APIC 寄存器的 bits 32 到 63。唯一一个 64 bit MSR 的 APIC 寄存器是 Interrupt Command Register。对保留 bits 的操作见 Section 10.12.1.3,“Reserved Bit Checking”。

2.1.2 x2APIC 寄存器地址空间[10.12.1.2]

800H 到 8FFH 范围内的 MSR 地址区域是 architecturally 保留的,专用于访问 x2APIC 模式下的 APIC 寄存器。Table 10-6 列举了 x2APIC 模式下可访问的 APIC 寄存器。

除以下场景之外,x2APIC MSRs 与 legacy xAPIC 寄存器偏移之间存在一对一映射关系:

Destination Format Register(DFR):DFR 在 xAPIC 模式下偏移为 0E0H,x2APIC 模式下不支持。80EH 地址没有对应的 MSR。

Interrupt Command Register(ICR):xAPIC 模式下的两个 32 bit 寄存器(偏移 300H 及 310H)在 x2APIC 模式下合并为一个 64 bit MSR(地址 830H)。831H 地址没有对应的 MSR。

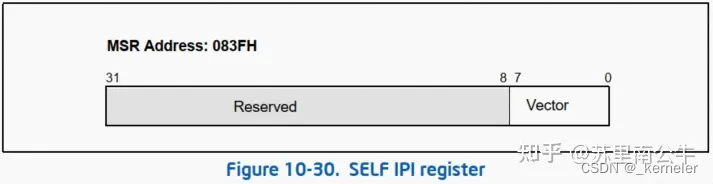

SELF IPI register:x2APIC 模式下该寄存器位于 83FH 地址处。xAPIC 模式下,3F0 偏移没有对应的寄存器。

未罗列在 Table 10-6(包括 80EH 及 831H)中的范围在 800H-8FFH 的 MSR 地址是保留的。对这些地址执行 RDMSR 及 WRMSR 会触发 general-protection exception。

为未来的地址增长考虑,对 MSR 地址空间进行了压缩。legacy MMIO 空间中 128-bit 边界上每个 32 bit 寄存器映射到 x2APIC MSR 地址空间的一个 MSR 上。所有 x2APIC MSRs 的高 32 bit(ICR 除外)都是保留的。

2.1.3 保留 bit 检查[10.12.1.3]

Section 10.12.1.2 及 Table 10-6 罗列了 x2APIC 模式下 APIC 寄存器的保留 bit。对这些寄存器的保留 bits 做非 0 写(WRMSR 指令)会触发 general protection 异常,读会返回 0(RsvdZ 语义)。

x2APIC 模式下 local APIC ID 寄存器宽度增长到 32 bit。这使得 physical 目标模式下有 232-1 个可寻址处理器。此 32 bit 值被称为“x2APIC ID”。一个具体的处理器实现可以在其硬件中实现少于 32 bit。系统软件对具体实现了多少个 bits 应该是不预知的。软件对未实现 bits 的读将返回 0。

FFFF_FFFFH 以及具体 local APIC ID 寄存器宽度实现下的最大值 APIC ID 是保留的,不可被赋予任何逻辑处理器。

x2APIC 模式下的 local APIC ID 寄存器对系统软件是只读的,由硬件初始化。通过 RDMSR 指令读 0802H 地址处的 MSR 来访问。

系统中的每个逻辑处理器(包括有通信 fabric 的 clusters)都必须配置一个唯一的 x2APIC ID 以免 x2APIC ID 冲突。

2.2 x2APIC register 可用性[10.12.2]

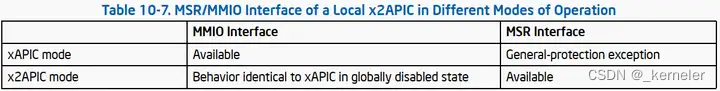

只有在将 local APIC 切换至 x2APIC 模式时才可以通过 MSR 接口访问 local APIC 寄存器(Section 10.12.1)。local APIC 在非 x2APIC 模式下时,通过 RDMSR 或 WRMSR 访问 0800H 至 08FFH 地址范围内的 APIC MSR 寄存器时会 general-protection 异常。x2APIC 模式下 MMIO 接口不可用,对 MMIO 的访问行为类似 legacy xAPIC 处于全局禁能状态时的行为。Table 10-7 展示了 legacy & extended 模式的交互以及寄存器接口。

2.3 x2APIC 模式下的 MSR 访问[10.12.3]

为实现 x2APIC 模式下 APIC 寄存器访问的高效性,弱化了 APIC 寄存器写入的 WRMSR 的 serializing 语义。因此,系统软件不应将“x2APIC 模式下对 APIC 寄存器的 WRMSR”作为 serializing 指令使用。对 APIC 寄存器的读和写访问是 program order 的。对 APIC 寄存器的 WRMSR 可能会在前面的 store 全局可见之前完成(译者注:意思就是 WRMSR 指令被重排至 store 之前);软件可以通过插入 serializing 指令或在 WRMSR 之前添加 MFENCE、LFENCE 避免此情况。

RDMSR 指令不是 serializing 的,且对 x2APIC 模式下 APIC 寄存器的读亦然。通过 RDMSR 指令访问 APIC 寄存器的系统软件不应期望有 serializing 行为(注意:基于 MMIO 的 xAPIC 接口被系统软件映射为 un-cached 区域。因此,xAPIC 模式下对 xAPIC-MMIO 接口的读写是有 serializing 语义的)。

2.4 MSR 及 x2APIC 寄存器的 VM-Exit 控制[10.12.4]

VMX 架构支持 VMM 通过 VMX-transition MSR 区域指定一个在 VMX 切换时进行 load 或 store 的 MSR 列表(参考 Intel 64 and IA-32 Architectures Software Developer’s Manual, Volume 3C 中的 VM-exit MSR-store address field,VM-exit MSR-load address field 以及 VM-entry MSR-load address field)。

x2APIC MSR 无法在 VMX 切换时 load 和 store。如果 VMM 指定 VMX 切换时访问任意地址在 0000_0800H 至 0000_08FFH 区域(该区域用来访问 x2APIC 寄存器)内的 MSR,则 VMX 会切换失败。具体来说,操作 VMX-transition MSR 区域内任意一个 128 bit entry 时,如果该 entry 的 bits 31 : 0(称为 ENTRY_LOW_DW)满足如下条件,则操作失败:“ENTRY_LOW_DW & FFFF F800H = 0000 0800H”。该操作的失败会导致对应的 VM entry 失败(通过重载 host 状态),并引发一个相应的 VM exit,最终 VMX abort。

2.5 x2APIC 状态转换[10.12.5]

略。

2.5.1 x2APIC 状态[10.12.5.1]

复位后的 x2APIC 状态

从 x2APIC 模式的 x2APIC 切换

从禁能模式的 x2APIC 切换

从 xAPIC 到 x2APIC 模式的状态切换

2.6 x2APIC 模式下的设备中断路由[10.12.6]

x2APIC 架构的设计的一个重要原则是兼容性,可以与现有 IOxAPIC 以及支持 MSI 的 PCI/PCIe 设备共同工作。x2APIC 支持的修改点仅在于:

local APIC

连接 IOxAPIC 与 local APIC 的 interconnect。

连接 MSI-capable PCI/PCIe 设备及 local APIC 的 interconnect。

MSI-capable PCI/PCIe 设备无需修改,同理,IOxAPIC 亦无需修改。这使得通过 Intel Virtualization Technology for Directed I/O, Revision 1.3 中的中断重映射架构,来实现 x2APIC 模式下 MSI-capable 设备到 local APIC 的中断路由成为可能。

2.7 系统软件的 x2APIC 初始化[10.12.7]

x2APIC 模式下设备中断到 local APIC 的路由需要使用 Intel Virtualization Technology for Directed I/O(Revision 1.3 和/或更新的版本) 中的中断重映射架构。正因为如此,BIOS 必须枚举中断重映射能力的支持,软件在使能 local APIC 的 x2APIC 模式前,必须通过 Extended Interrupt Mode Enabled 来使能中断重映射。

x2APIC 的 ACPI 接口在 Advanced Configuration and Power Interface Specification,Revision 4.0a,Section 5.2,“ACPI System Description Tables”。BIOS 的默认行为是,如果所有 APIC ID(CPUID.0BH:EDX)皆小于 255,或者 x2APIC 模式下有任意逻辑处理器其 APIC ID 大于等于 255,则将 xAPIC 模式下的 local x2APIC 控制交给操作系统。

2.8 CPUID 扩展及拓扑枚举[10.12.8]

略。

2.8.1 APIC ID 与 CPUID 的一致性[10.12.8.1]

略。

2.9 x2APIC 模式下的 ICR 操作[10.12.9]

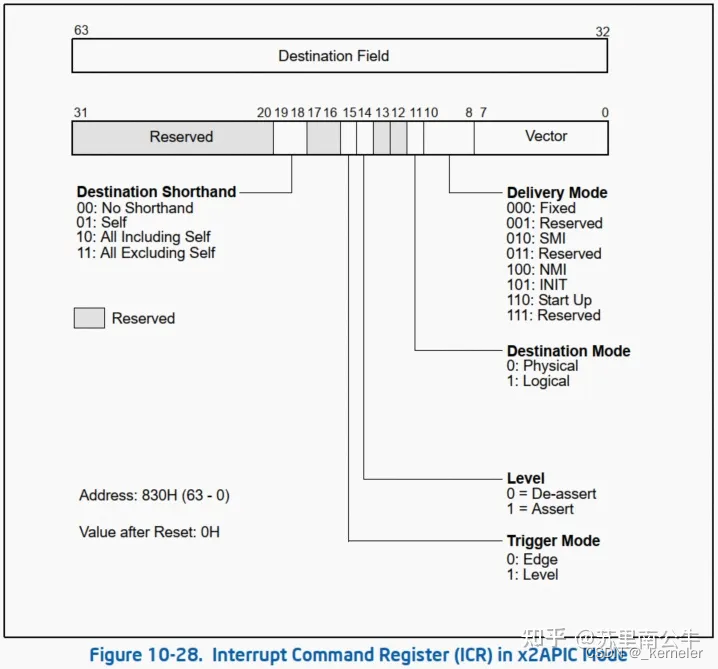

x2APIC 模式下的 ICR(Interrupt Command Register) 布局见 Figure 10-12。x2APIC 模式下 ICR 的低 32 与 xAPIC 模式下的 ICR 的低半部分相同,Delivery Status bit 除外,因为 x2APIC 模式下没有这个。destination ID 域在 x2APIC 模式下扩展到 32 bit。

要通过 ICR 发送 IPI,软件需要配置 ICR 指明 IPI 消息的类型以及目标处理器(们)。self IPI 还可以通过 SELF IPI 寄存器发送(Section 10.12.11)。

对 ICR 的 MSR 写会触发一个 x2APIC 模式下的中断。因为移除了 Delivery Status bit,系统软件不再需要读 ICR。为调试缘故其保持只读状态;但是,软件不应该假设 ICR 读的返回值是上一次的写入值。

FFFF_FFFFH 目标 ID 用作 logical destination 和 physical destination 模式下的广播中断。

2.10 x2APIC 模式下的 IPI 目标决议[10.12.10]

略。

2.10.1 x2APIC 模式下的 logical destination 模式[10.12.10.1]

略。

2.10.2 从 local x2APIC ID 到 logical x2APID ID[10.12.10.2]

略。

2.11 Self IPI Register[10.12.11]

SELF IPI 在系统软件中应用广泛。x2APIC 架构引入了新的寄存器接口。该寄存器是实现高效的 self-IPI 发送。

9

9

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?