代码1

void hp_test(volatile int* a1,volatile int* b){

#pragma HLS INTERFACE m_axi port=a1 offset=slave bundle=IN1

#pragma HLS INTERFACE m_axi port=b offset=slave bundle=OUT

#pragma HLS INTERFACE s_axilite port=return bundle=CTRL

int buff[10000];

int i;

loop1:for(i=0;i<10000;i+=4){

buff[i]=*(a1+i);

buff[i+1]=*(a1+i+1);

buff[i+2]=*(a1+i+2);

buff[i+3]=*(a1+i+3);

}

loop2:for(i=0;i<10000;i++)

*(b+i)=buff[i];

}

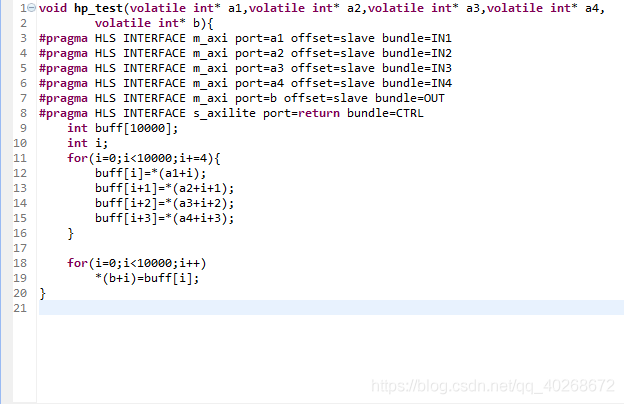

代码2

代码2有两种连接方式,四个IN接口只和一个AXI HP口相连、四个IN接口分别和四个AXI HP接口相连。

最终实验结果如下:

代码1:1个AXI接口 用时1378us

代码2:4个AXI接口1个AXI HP接口 用时619us

代码2:4个AXI接口4个AXI HP接口 用时511us

可见即使多个AXI接口连接1个HP接口,也能起到增大带宽的作用,而多个AXI HP接口则能达到更大的带宽。

4763

4763

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?