BRAM简介

BRAM,即Block RAM,是FPGA中一种重要的存储资源,另一种常见的存储资源是DRAM(Distributed RAM),Distributed RAM 经过综合工具综合,通过多级 LUT 查找表资源级联实现,因此会消耗较多的逻辑资源。

而是BRAM是FPGA 厂商在逻辑资源之外,给 FPGA 加入的专用 RAM 块资源。相比分布式 RAM,BRAM 块内部以及与逻辑资源之间经过特意的布局布线,使 BRAM 具有很高的运行速度,确定的低延迟周期。

BRAM的容量为36Kb,且可当作两个独立的18Kb BRAM使用。对于一个36Kb的BRAM,其最能达到的最大位宽为72bit。BRAM 的初始值是可以设定的,无论 BRAM 是单端口、简单双端口还是真双端口都可以通过 COE 文件设定其初始值

BRAM类型

总体上 Memory 按照类型可以分为RAM 和 ROM,ROM 预置了数据,在使用中只能被读取,不能写入,ROM 实现的物理结构与 RAM 类似,相当于一个只能读取的 ”RAM”。一般用于存放一些固定的参数,在使用过程中只能读取,不需要也不能修改。

按照端口的数量有单端口以及双端口之分,双端口来自于同时对 RAM 进行读写的需求。一边将等待处理的数据从端口 A 输入 RAM,另一端口 B 读取数据进行处理,可以实现高效的数据流式处理,尤其适用于图像的行缓存处理。双端口 RAM 相较于 FIFO ,有可以映射地址以及多次重复利用数据的优势。在新的数据写入之前,可以多次从一指定位置读取旧数据。

此外,双端口 RAM 又可以分为 Simple/Ture 双端口

三种读写模式

BRAM有三种读写模式,分别是Write First,Read First和No Change。

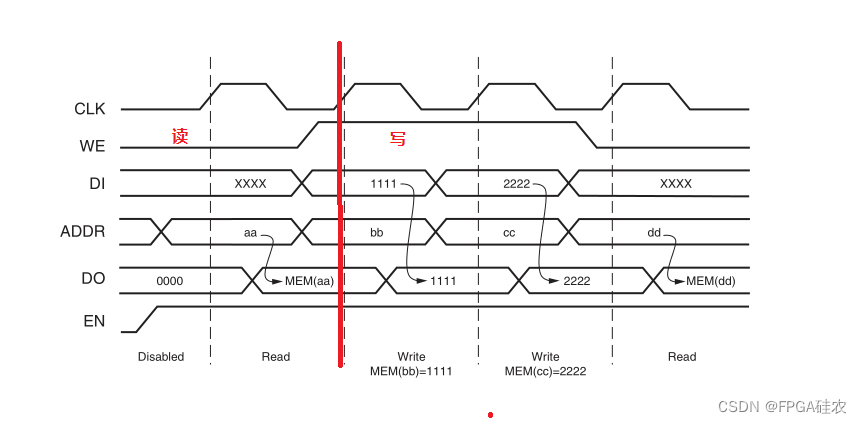

写优先

上图为Write_First的时序图,在红线以前,WE=0 ,即端口做的是读操作。在CLK上升沿后,地址aa里的数据打到DO(MEM(aa))。在红线后,WE=1,即端口做的是写操作。在CLK上升沿后,DI(1111)的数据存入到地址bb里,与此同时输入的数据DI直接输出到DO,原先存在bb里的数据还没出来就被冲掉了。

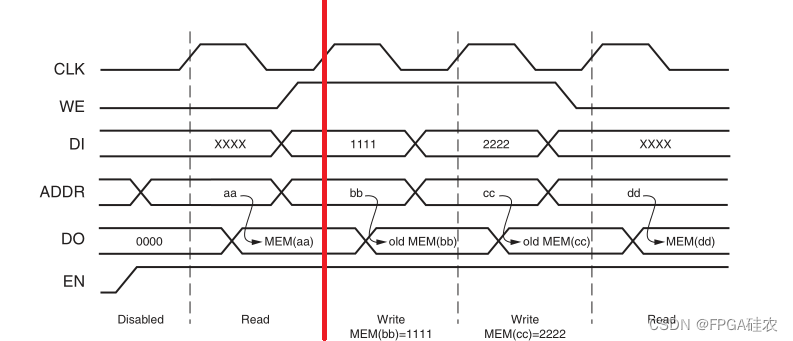

读优先

上图为Read_First的时序图,在红线以前,WE=0 ,即端口做的是读操作。在CLK上升沿后,地址aa里的数据打到DO。在红线后,WE=1,即端口做的是写操作。在CLK上升沿后,DI的数据存入到地址bb里,与此同时原先存放在地址bb的数据输出到DO。该模式以消耗更多 BRAM 资源的前提下,保证每次读操作读取到的都是先前的数据。输入数据会首先被缓存,与此同时在输出总线上输出先前值。

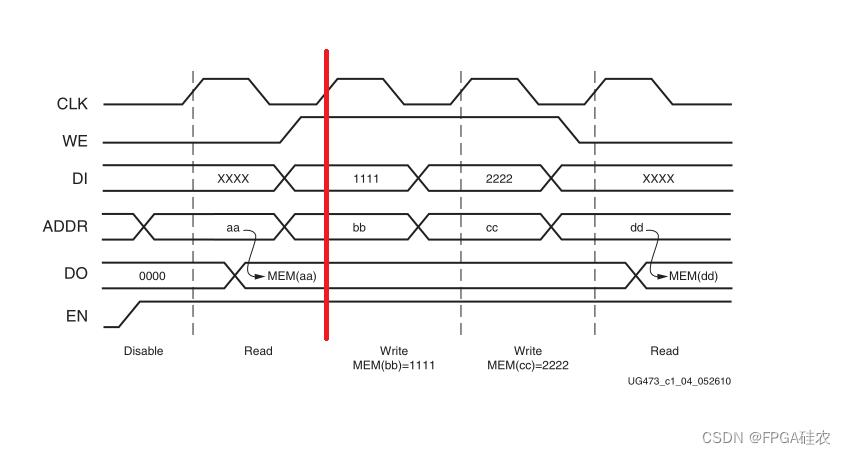

No change

上图是NO_CHANGE的时序图,在红线以前,WE=0 ,即端口做的是读操作。在CLK上升沿后,地址aa里的数据打到DO。在红线后,WE=1,即端口做的是写操作。在CLK上升沿后,DI的数据存入到地址bb里,与此同时输出DO的数据保持不变(依旧是地址aa里的数据)。

总线支持

Xilinx的BRAM支持两种形式的总线:Native和AXI

输出寄存

另外重要的一点是配置 RAM 的输出寄存器。共有两个选项 Primitive / Core Output Register。这两个选项可以各自选择,都是为输出端添加一级寄存器,不同在于前者在 Port 内部添加寄存器,而后者是在 Port 外部添加寄存器。每一级的寄存器都会增加一个周期的读延迟,从初始的 1 周期读延迟,最高可以增加到 3 周期读延迟。

添加寄存器虽然会增加延迟周期数,因为输出信号经过了打拍,但其优点是可以改善时序。

206

206

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?