Vivado与matlab系统开发设计 system generator(1)入门与安装

今天由“82年的程序媛”本媛给大侠带来FPGA设计 vivado 与 matlab系统开发设计之 System generator 入门与安装,后续本媛还会继续更新产品项目开发心得,学习心得等,欢迎大家持续关注,话不多说,上货。

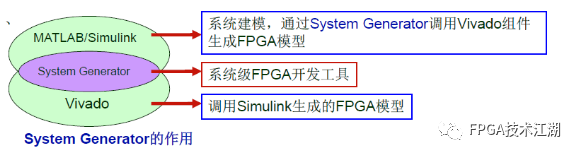

System generator 是一款 xilinx 公司的 DSP设计工具,其借助MATLAB中的 simulink 开发环境完成 FPGA 的设计,是一种基于模型设计的方法。

System generator具有如下关键特性:

-

超过90种DSP设计模块,包括加法器、乘法器、寄存器、FFT、滤波器、存储器等等;

-

包含一个与7系列/UltraScale系列FPGA相贴合的FIR编译模块,支持多种滤波器模式,可以使用MATLAB函数或FDATOOL工具生成系数;

-

包含一个Mcode模块,可以接入MATLAB代码完成简单的控制;

-

可以生成HDL文件、网表或IP核,在vivado中调用。

System generator的安装

System generator软件可在安装vivado时一起安装,需要与MATLAB一起使用,并且必须与MATLAB版本兼容。

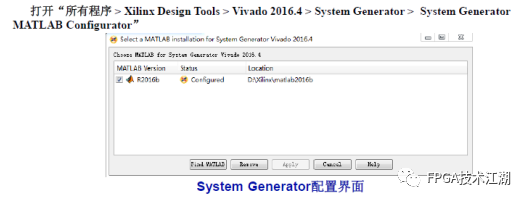

1、配置MATLAB

选中前面的复选框,点击“Apply”,status变更为“configured”,表明配置正确。

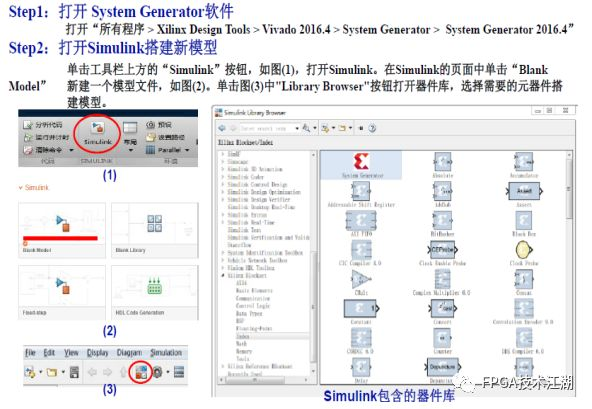

2、Simulink建模

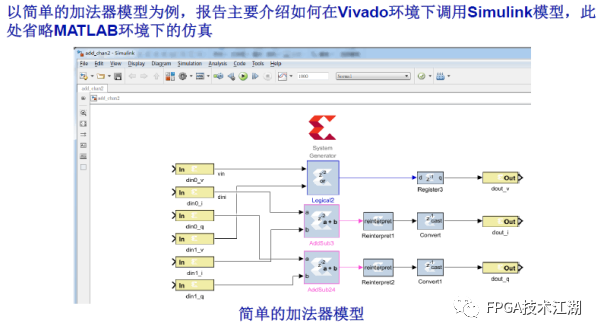

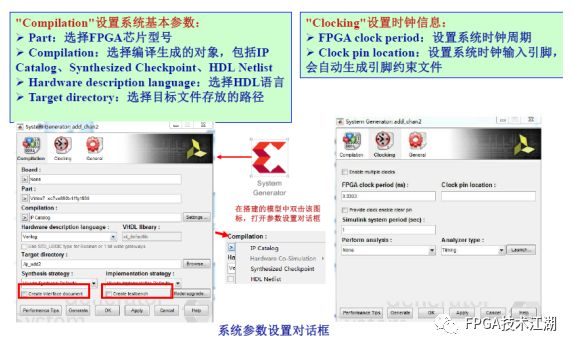

3、System generator参数配置

4、Vivado调用system generator生成模型的三种方式

(1)、以IP核的形式生成IP,用户在设计时直接调用IP:

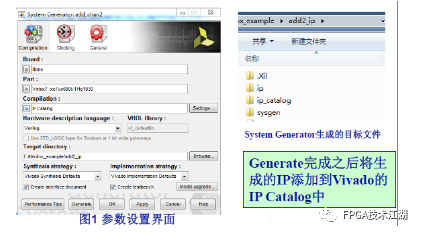

Compilation选项选择“IP Catalog”,设置好其他参数之后,单击“Generate”生成IP;

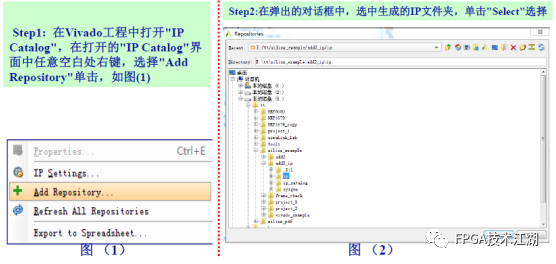

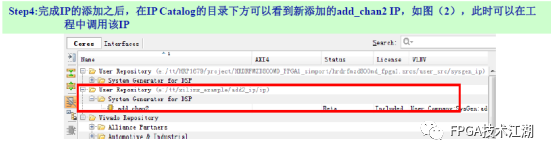

在vivado中添加IP;

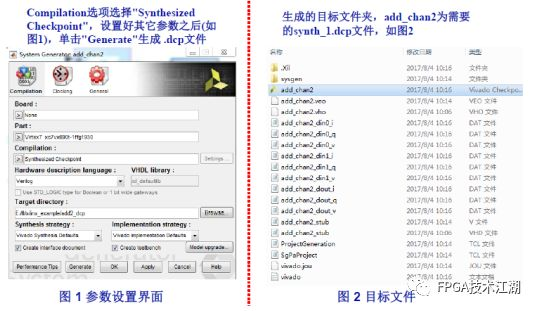

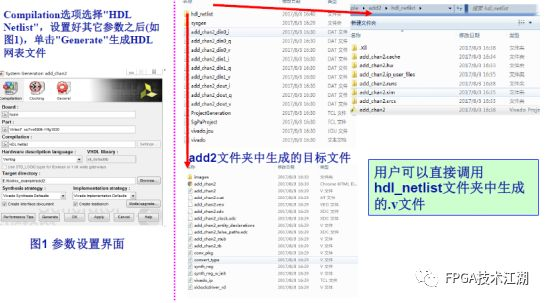

(2)、将模型生成.dcp文件

(3)、将模型生成HDL网表文件

5、Vivado调用system generator生成模型的三种方式对比

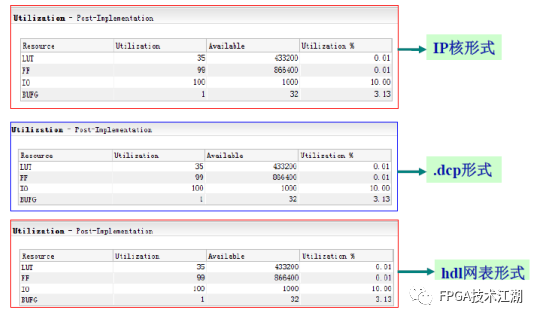

(1)、Vivado调用add2模型三种目标文件时,FPGA的资源利用率对比:

(2)、通过对比,三种方式消耗FPGA资源相同。

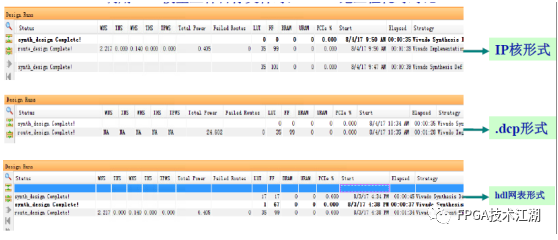

FPGA跑工程耗时对比:

(3)、三种方式特点对比:

-

IP核和.dcp形式下的模型在跑工程的时候需要的时间少于HDL网表。

-

“HDL Netlist”选项时,需要调用模型的所有.v文件,操作上不如另外两种方便

-

HDL网表文件可以直接在vivado工程中修改,另外两种需要修改MATLAB中的模型

-

IP核的可移植性。

工程设计中推荐使用IP核形式。

END

以上是本媛一小部分心得总结,仅供参考。

【QQ交流群】

群号:173560979,进群暗语:FPGA技术江湖粉丝。

多年的FPGA企业开发经验,各种通俗易懂的学习资料以及学习方法,浓厚的交流学习氛围,QQ群目前已有1000多名志同道合的小伙伴,无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有。

【微信交流群】

现微信交流群已建立08群,人数已达数千人,欢迎关注“FPGA技术江湖”微信公众号,可获取进群方式。

完

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

江湖偌大,继续闯荡,愿大侠一切安好,有缘再见!

5801

5801

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?