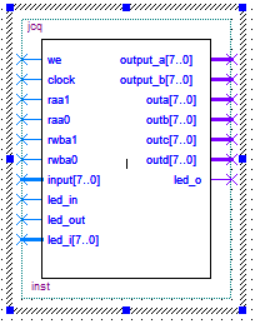

3)JCQ部分

library ieee;

use ieee.std_logic_1164.all;

entity jcq is

port(we,clock:in std_logic;

raa1,raa0,rwba1,rwba0:in std_logic;

input:in std_logic_vector(7 downto 0);

led_in:in std_logic:='0';

led_out:in std_logic:='0';

led_i:in std_logic_vector(7 downto 0);

output_a,output_b:out std_logic_vector(7 downto 0);

outa,outb,outc,outd:out std_logic_vector(7 downto 0);

led_o:out std_logic

);

end jcq;

architecture st of jcq is

signal a:std_logic_vector(7 downto 0):="11111100";--chu shi zhi

signal b:std_logic_vector(7 downto 0):="00000111";--chu shi zhi

signal c:std_logic_vector(7 downto 0):="01100011";--chu shi zhi

signal d:std_logic_vector(1 downto 0):="00";--di zhi ji cun qi

begin

process(clock,we,input,raa1,raa0,rwba1,rwba0)

begin--shi neng duan wei 0 de shi hou ke yi xie ru

if (we='0' and falling_edge(clock)) then--tong guo raa de shu ru lai pan ding wang na ge ji cun qi zhong shu ru shu ju

if (raa1='0' and raa0='0') then a<=input;--00,01 shi fu gei a ji cun qi

elsif (raa1='0' and raa0='1') then b<=input;

elsif (raa1='1' and raa0='0') then c<=input;--10 shi fu gei b ji cun qi

elsif (raa1='1' and raa0='1') then d<=rwba1 & rwba0;--11 shi fu gei c ji cun qi

end if;

elsif (we='1' and falling_edge(clock)) then

if (we='1' and led_in='1') then

if (raa1='0' and raa0='0') then a<=led_i;--00,01 shi fu gei a ji cun qi

elsif (raa1='0' and raa0='1') then b<=led_i;

elsif (raa1='1' and raa0='0') then c<=led_i;--10 shi fu gei b ji cun qi

elsif (raa1='1' and raa0='1') then d<=led_i(1 downto 0);--11 shi fu gei c ji cun qi

end if;

end if;

if (we='1' and led_out='1') then

if (raa1='0' and raa0='0') then led_o<='1';--00,01 shi fu gei a ji cun qi

elsif (raa1='0' and raa0='1') then led_o<='1';

elsif (raa1='1' and raa0='0') then led_o<='1';--10 shi fu gei b ji cun qi

elsif (raa1='1' and raa0='1') then --11 shi fu gei c ji cun qi

if (d="00") then led_o<='1';

elsif (d="01") then led_o<='1';

elsif (d="10") then led_o<='1';--cun c

elsif (d="11") then led_o<='1';--hai shi cun c

end if;

end if;

else

led_o<='0';

end if;

end if;

if (raa1='0' and raa0='0') then output_a<=a;

elsif (raa1='0' and raa0='1') then output_a<=b;

elsif (raa1='1' and raa0='0') then output_a<=c;

elsif (raa1='1' and raa0='1') then

if (d="00") then output_a<=a;

elsif (d="01") then output_a<=b;

elsif (d="10") then output_a<=c;--cun c

elsif (d="11") then output_a<=c;--hai shi cun c

end if;

end if;

if (rwba1='0' and rwba0='0') then output_b<=a;

elsif (rwba1='0' and rwba0='1') then output_b<=b;

elsif (rwba1='1' and rwba0='0') then output_b<=c;

elsif (rwba1='1' and rwba0='1') then

if (d="00") then output_b<=a;

elsif (d="01") then output_b<=b;

elsif (d="10") then output_b<=c;--cun c

elsif (d="11") then output_b<=c;--hai shi cun c

end if;

end if;

end process;

outa<=a;

outb<=b;

outc<=c;

outd<="000000" & d;

end st;

接口设计:

Clock:时钟信号

Outa,outb.outc,outd:内存的展示输出

Input:传入的处理数据

Led_i:来自外部的输入数据

Led_o:向外部输出的数据

Raa1,raa0,rwba1,rwba0,led_in,led_out:控制信号

we:使能信号

Output_a,output_b:数据的输出

功能实现:

存储进行计算的数据,并在raa0,raa1,rwba0,rwba1的控制下从寄存器中选择对应的数据。我采用了四个寄存器,分别为三个数据寄存器abc和一个地址寄存器d,数据寄存器中存储初始数据,地址寄存器中若为00则指向a寄存器,01指向b寄存器,10和11指向c寄存器。简单的讲就是一个寄存器组,包括了三个八位二进制数的寄存器和一个两位的二进制数的地址寄存器,这个可以通过自己定义,书上要求的是三个寄存器,即两个八位二进制数的寄存器和一个地址寄存器,我由于感觉对于两位二进制信号有四种情况,所以出现了信号浪费,故进行了添加,将八位寄存器数改为了三个。以此来减少浪费,也看着比较整齐。

另外,我在此实现了in和out两条指令,即外部可以改变寄存器中的数据,也可以查看寄存器中的数据(寄存器中的数据可以输出给外部)。

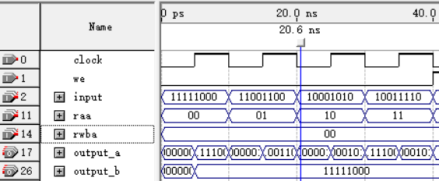

仿真验证:

在we为0的时候进行取值操作,根据raa和rwba的值取出相对应的数值,在raa为00时输出a寄存器的值,为01时输出b寄存器的值,在1时输出c寄存器的值,特定的,在raa为11的时候输出d寄存器所存储的寄存器的地址的该寄存器的值,即若d寄存器中存储的是00,则输出a寄存器的值,若为01则输出b寄存器的值,若为10或11则输出c寄存器的值。

结论:正确,信号结果正确。

下一篇

3187

3187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?