Verilog入门

模块表达

module 模块名(模块端口名表);

模块端口和模块功能描述

input 端口名1,端口名2,…;

output 端口名1,端口名2,…;

inout 端口名1,端口名2,…;

input[msb:lsb] 端口名1,端口名2,…;

endmodule

//标识符:由英文字母、数字、下划线、$组成,

由字母下划线开始,不能有双下划线。

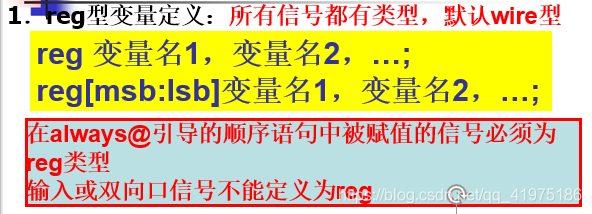

//Intput outout都是默认wire型

//逻辑操作符号

& 与 | 或 ~非 ^ 异或 ~^ 同或

//Always里面被赋值的都是reg类型变量

always

凡是在always里面赋值的变量都是寄存器类型的变量

顺序语句一定要写在always里面,即:任何顺序语句都要放在结构语句里面

解释一下always语句的含义:always语句本质上对实际电路并行运行的一种模拟

always括号里面标记着各种输入信号的激励,每一次激励的发生都会触发一次请求事件

然后执行一遍always里面的顺序语句。相当于网页页面中的添加事件发生

//块语句begin_ end:相当于C语言的花括号

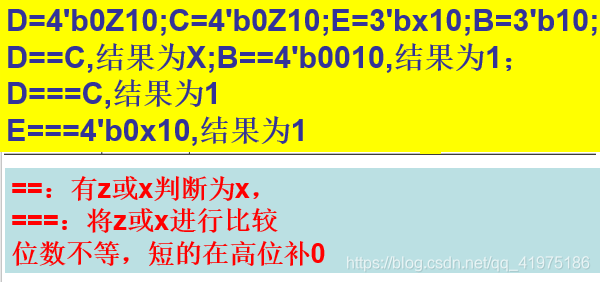

//任何变量有4种逻辑状态

0 1 Z高阻态 X不确定

// assign

assign 连续赋值语句

用前面的case条件判断来类比此处的assign语句

assign 目标变量名 = 驱动表达式

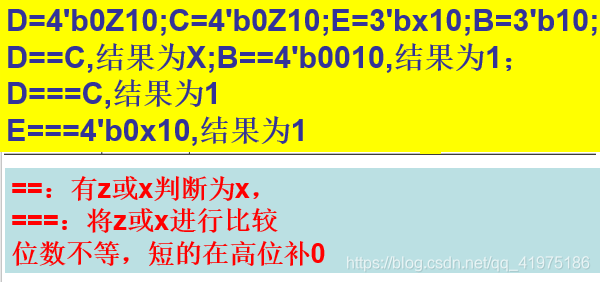

// 等式操作符

==等于 ===全等

//过程赋值语句

1阻塞式赋值: = 立即得到值,顺序性(当执行某一语句时,其他语句不可能同时执行 即顺序执行

2)非阻塞式赋值:<= 即同时执行

总结:

1:组合逻辑,使用 “阻塞赋值”。

2:时序逻辑,使用“非阻塞赋值”。

// assign

assign 连续赋值语句

assign 目标变量名 = 驱动表达式

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?