目录

实验目的

通过上篇文章生成的coe文件初始化rom核,并将数据读出,验证与写入的是否一致,以此来验证对ROM核的控制是否正确。

实验代码

module ip_rom(

input clk,

input rst_n

);

reg [15:0] trig_addr;

reg trig;

always@(posedge clk or negedge rst_n)

if(!rst_n)

trig_addr <= 0;

else

trig_addr <= trig_addr + 1'b1;

always@(posedge clk)

if(trig_addr == 0)

trig <= 1'b1;

else

trig <= 1'b0;

reg [16:0] addr;

always@(posedge clk)

begin

if(trig)

addr <= 0;

else if(~addr[16])

addr <= addr + 1'b1;

end

wire [15:0] xn_re, xn_im;

lfm lfm_inst (

.clka(clk), // input wire clka

.addra({1'b0,addr[15:0]}), // input wire [16 : 0] addra

.douta(xn_re), // output wire [15 : 0] douta

.clkb(clk), // input wire clkb

.addrb({1'b1,addr[15:0]}), // input wire [16 : 0] addrb

.doutb(xn_im) // output wire [15 : 0] doutb

);

endmodule

测试文件

`timescale 1ns / 1ps

module ip_rom_tb();

reg clk, rst_n;

initial begin

clk = 1'b1;

rst_n = 1'b0;

#20

rst_n = 1'b1;

end

always #10 clk <= ~clk;

ip_rom ip_rom_inst(

.clk (clk),

.rst_n (rst_n)

);

endmodule

实验结果及分析

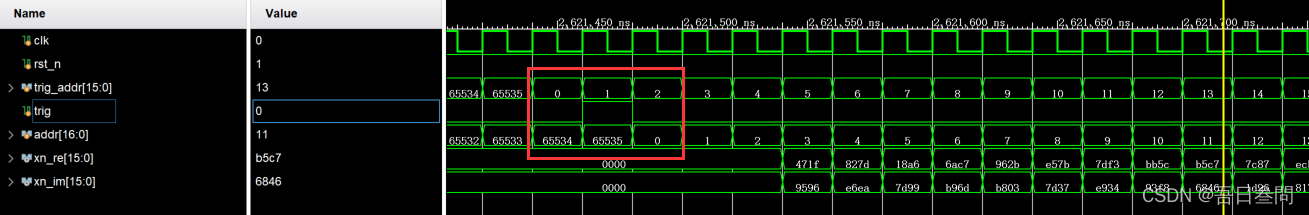

对红色方框中的时序进行分析:当trig_addr为0时(计数器计数溢出后清零),trig信号拉高(延迟一拍,这是时序电路的特点);当trig信号拉高后,addr清零,开始从rom中读数,因为rom核的延迟效果,所以地址为0时读取到的不是第一个数。

489

489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?