一、AXI——高级可扩展接口(UG1037)

参考资源:

- 【SDK篇_58~62_AXI接口简介【Xilinx】+【Vivado】+【AXI4总线】+【FPGA】-哔哩哔哩】 关于AXI握手过程都讲解的很细致

- ug1037(三种AXI的介绍,相关AXI IP的介绍) IHI0022D(握手过程的详细介绍)

- FPGA_HP:AXI4的学习与使用1——基础知识积累 这个博主写的其他内容也不错

- 从零学习AXI4总线(二):AXI4-Stream 介绍

- 带你快速入门AXI4总线–AXI4-Stream篇(1)----AXI4-Stream总线

1、AXI接口介绍

AXI是ARM AMBA的一部分。AMBA:开放的片内互联的总线标准,能在多主机设计中实现多个控制器和外围设备之间的连接和管理。AMBA AXI协议规范在(IHI0022D)中,详细介绍了AXI的端口

AXI4 接口 (AMBA 4.0) 分 3 种类型:

AXI4 (AXI4-Full):用于满足高性能存储器映射需求。

存储器映射:主机在对从机进行读写操作时,指定一个目标地址,这个地址对应系统存储空间的地址,表示对该空间进行读写操作。

AXI4-Lite:用于简单的低吞吐量存储器映射通信(例如,往来于状态寄存器的通信)。

简化版的AXI4接口,AXI4支持突发256,AXI-Lite支持单次传输一个数据,不支持突发

AXI4-Stream(ST):用于高速流传输数据。

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有地址接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模。AXI4-Stream的核心思想在于流式处理数据。 带你快速入门AXI4总线–AXI4-Stream篇(1)----AXI4-Stream总线

PS与PL间的接口,如GP、HP和ACP都只支持AXI_Lite和AXI_Full协议,并不支持AXI_Stream协议,需要进行协议转换后,才能进行相应的对接

2、各总线构成

参考AXI_Lite 总线详解

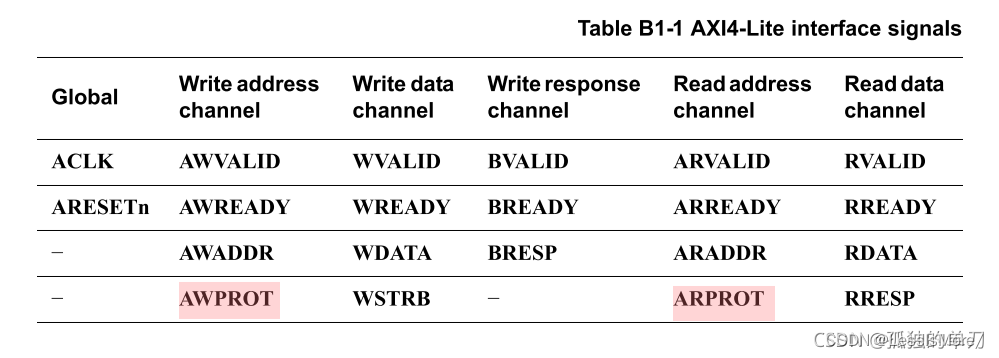

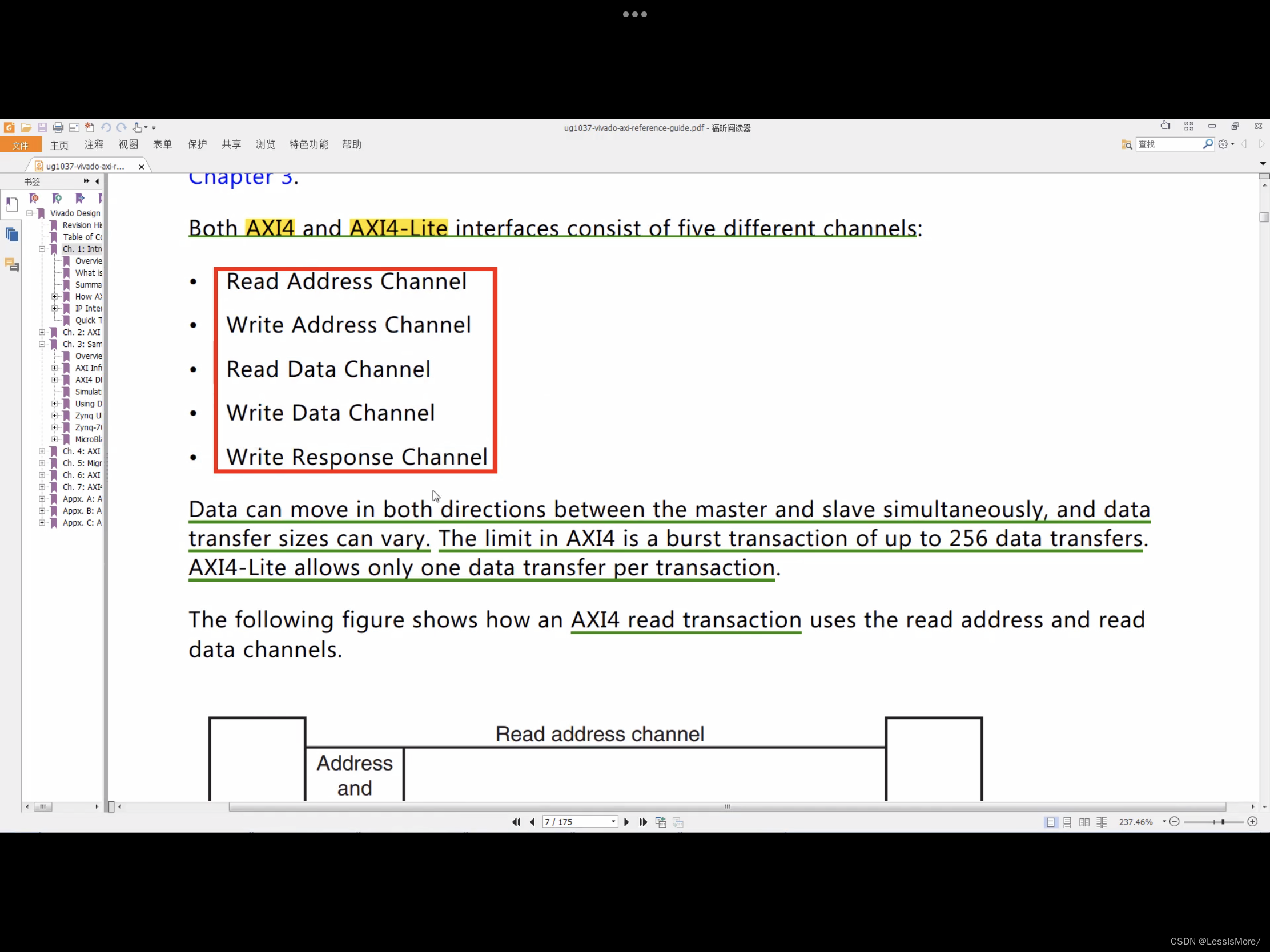

首先说AXI4总线和AXI4-Lite总线具有相同的组成部分:

(1)读地址通道,包含ARVALID, ARADDR, ARREADY信号;

(2)读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

(3)写地址通道,包含AWVALID,AWADDR, AWREADY信号;

(4)写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

(5)写应答通道,包含BVALID, BRESP, BREADY信号;

(6)系统通道,包含:ACLK,ARESETN信号。

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:

读地址信号都是以AR开头(A:address;R:read)

写地址信号都是以AW开头(A:address;W:write)

读数据信号都是以R开头(R:read)

写数据信号都是以W开头(W:write)

应答型号都是以B开头(B:back(answer back))

了解到总线的组成部分以及命名特点,那么在后续的实验中您将逐渐看到他们的身影。每个信号的作用暂停不表,放在后面一一介绍。

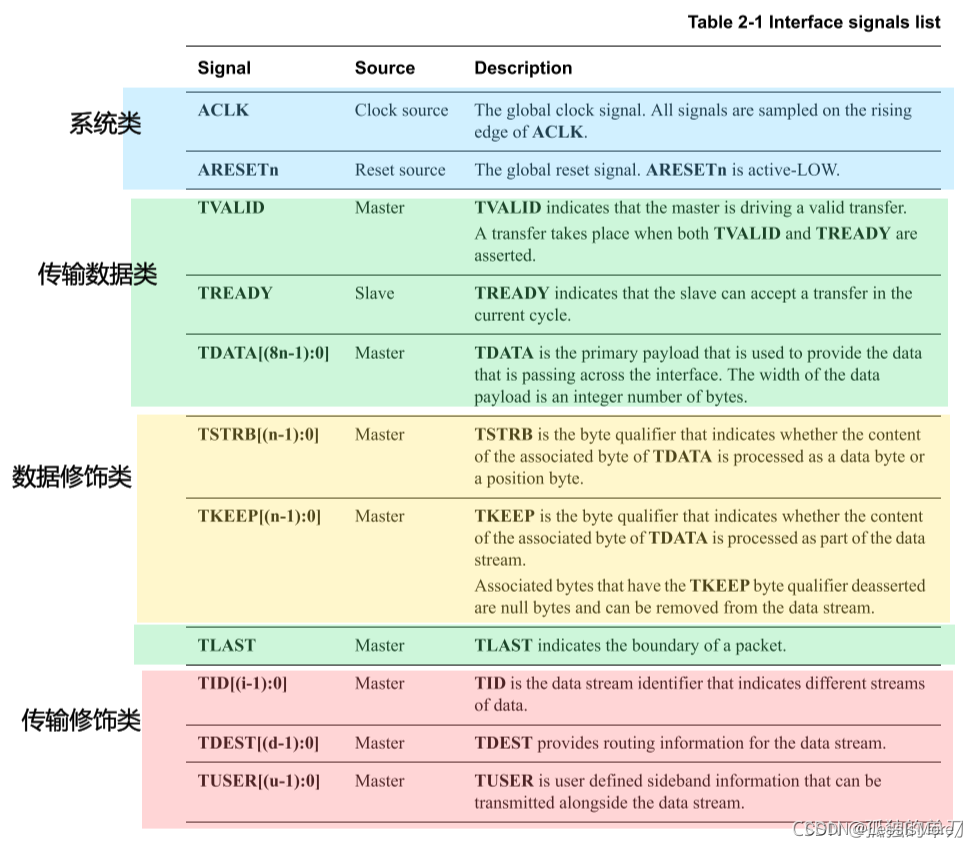

而AXI4-Stream总线的组成有:

(1)ACLK信号:总线时钟,上升沿有效;

(2)ARESETN信号:总线复位,低电平有效

(3)TREADY信号:从机告诉主机做好传输准备;

(4)TDATA信号:数据,可选宽度32,64,128,256bit

(5)TSTRB信号:每一bit对应TDATA的一个有效字节,宽度为TDATA/8

(6)TLAST信号:主机告诉从机该次传输为突发传输的结尾;

(7)TVALID信号:主机告诉从机数据本次传输有效;

(8)TUSER信号 :用户定义信号,宽度为128bit。

对于AXI4-Stream总线命名而言,除了总线时钟和总线复位,其他的信号线都是以T字母开头,后面跟上一个有意义的单词,看清这一点后,能帮助读者记忆每个信号线的意义。如TVALID = T+单词Valid(有效),那么读者就应该立刻反应该信号的作用。每个信号的具体作用,在后面分析源码时再做分析

带你快速入门AXI4总线–AXI4-Lite篇(1)----AXI4-Lite总线 孤独的单刀

3、AXI4-Stream握手信号

从零学习AXI4总线(二):AXI4-Stream 介绍

AXI4-Stream协议的信号接口如下

系统时钟和复位不用说,

传输数据类里就涉及一个握手协议,即在主从双方数据通信前,有一个握手的过程。基本内容:数据的传输源会产生“VALID”信号,来指明何时数据有效或控制信息有效。而在目标源一方,会产生“READY”信号,来指明已经准备好接受数据或控制信息。当“VALID”信号和“READY”信号同时为高时,就会发生数据传输。根据两个信号变高的时间不同,会出现三种传输的情况。但实际中,“写数据或地址信道”只有“先拉高VAILID,后等待READY”这种情况能工作,其他情况一般通过不了。所以,平时按照第一种情况来进行开发设计就OK了。参考:FPGA_HP:AXI4的学习与使用1——基础知识积累

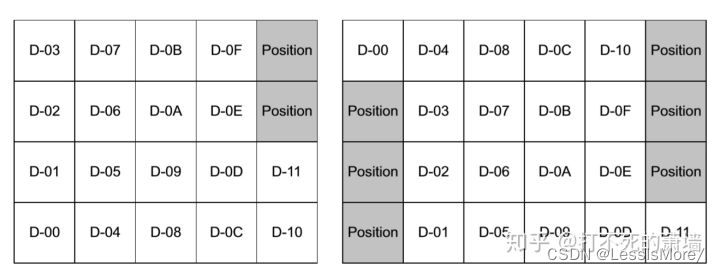

数据修饰类:AXI4-Stream传输的数据流包含三种类型:data type、position type、null type。data type是最有意义的数据;position type 作为占位符使用,可以用来表征date type 的相对位置,null type不包含任何有用的信息。这里面是一个小框代表8bit的一个字节,TKEEP和TSTRB告诉我们每个字节是3个中的哪一个类型。

3

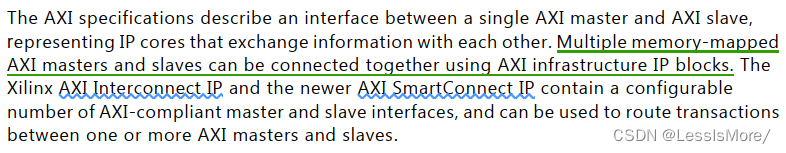

二、AXI Interconnect(vivado中的一个IP)

这个IP的作用是提供将“一个或多个”AXI主设备连接到“一个或多个”AXI从设备的一种交换机制(有解码路由等概念),通常我们Add了AXI的IP并进行连线后,都会自动加上这个IP,这个IP有详细一个文档去介绍,可以查阅PG059。另外SmartConnect IP也可以实现这个功能。FPGA_HP:AXI4的学习与使用1——基础知识积累 文中有使用这个IP的例子,就是主从设备相连

但要注意这个ip不能用于连接AXI4-Stream接口,stream接口要用 AXI4-Stream Interconnect core IP (axis_interconnect)

AXI4 AXI4-Lite都包含5个独立的通道,读写可同时双向传输,具体读写过程见ug1037

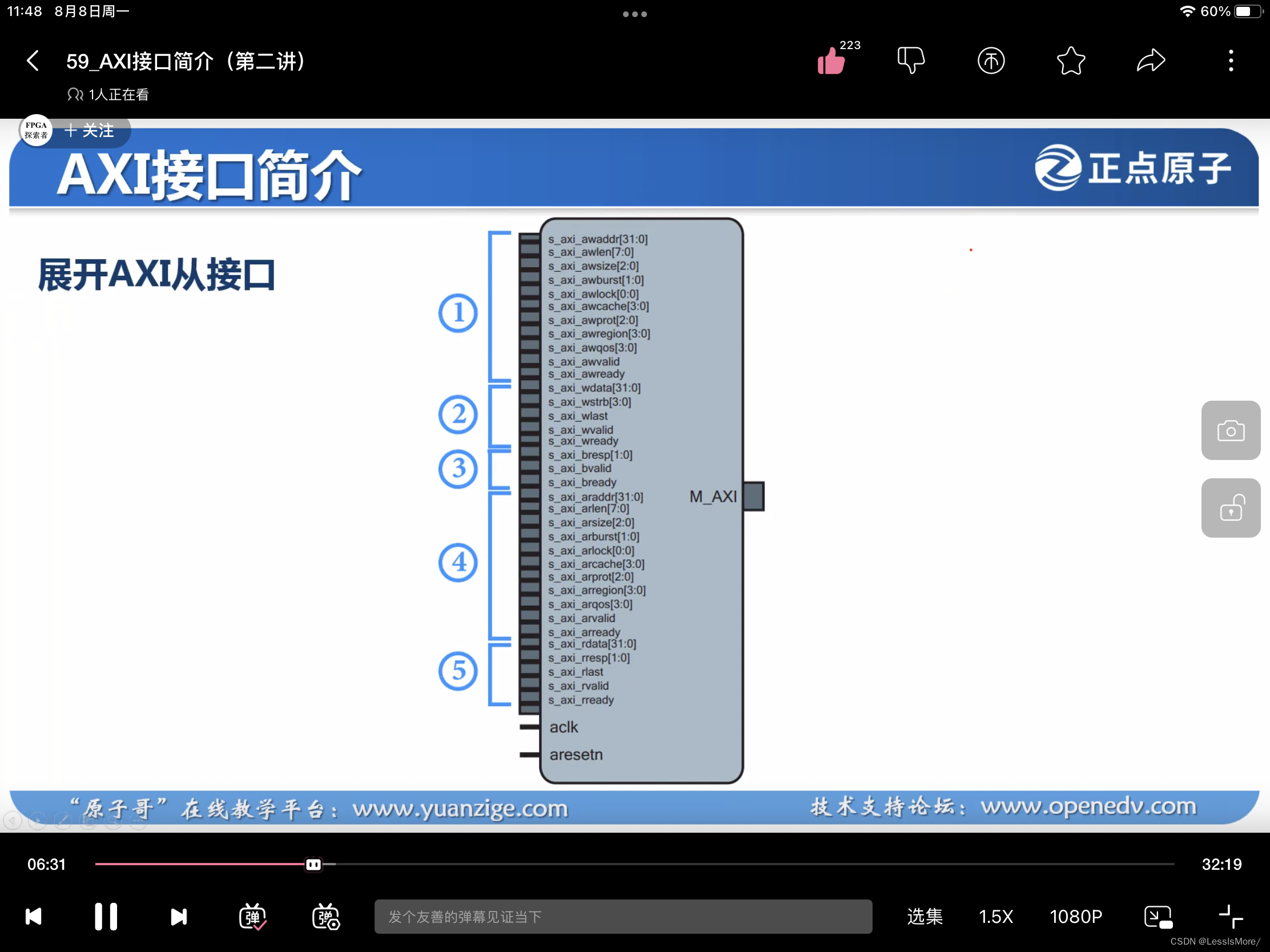

IP核的S_AXI接口展开之后,可以看到所有的端口,下图5组对应上述的5个通道,aw写地址、w写数据、b写响应、ar读地址、r读数据

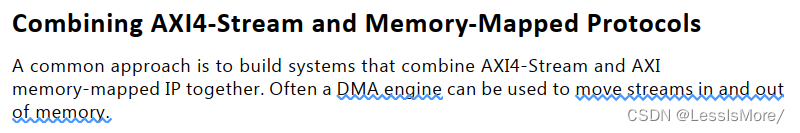

- 数据流和地址映射的转换用的是DMA

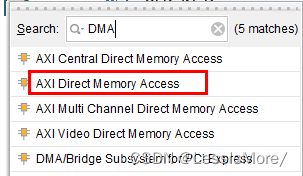

三、DMA

数据流和地址映射的转换用的是DMA

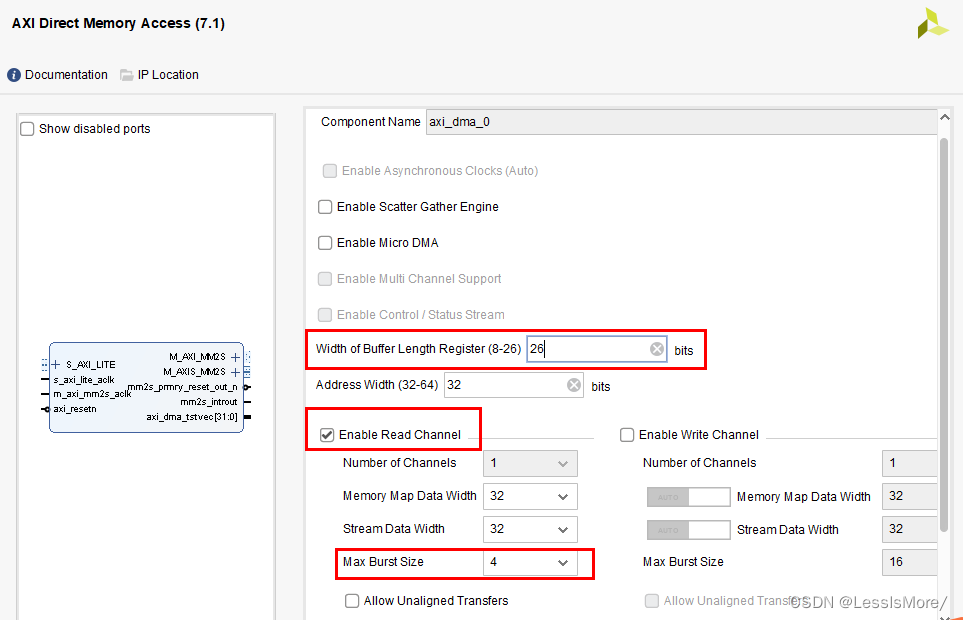

以Xilinx家的DMA控制器(英文全称:AXI Direct Memory Access)的读取功能(Read Channel)为例,它能够通过AXI总线读取某个地址区间的数据,同时再将这些数据转换以数据流的形式传输至处理单元。可以在不在CPU干涉的情况下进行数据的搬运。

Buffer Length最大位宽为26,对应的单次传输大小最大为64MByte

普通模式的DMA对于解决简单的数据传输,完全能够应付。但是当面向大规模数据(单次传输>64MByte),或需要操作的地址不连续时,普通模式的DMA不能够满足要求,即便能够将大规模数据分割为多个<64MByte的片段,但是这个过程需要额外的处理器(例如ARM/NIOS/MicroBlaze/RISC-V)进行查询监测,或者启用中断函数,这样额外的消耗了处理器性能(我们期望的是一次配置,永久使用)。对于这样的问题,通常启用该IP核的高级功能——Scatter Gather (SG) Engine模式,虽然单个传输片段依然有64MByte的限制(取决于Buffer Length Width),但是我们可以把一片>64MByte的数据划分为多个<64MByte的区域来解决。并且在此基础上,我们需要传输的数据有多个地址不连续的片段,同样也能够完美解决。其中开启Scatter Gather Engine后,IP核的接口如下图所示。与普通模式的DMA相比,多了一根M_AXI_SG总线。

基于Xilinx FPGA的AXI Direct Memory Access (Scatter Gather Engine模式) 行为分析及软件操作流程

主要讲的是sc模式的DMA及工程实践

FPGA Vivado AXI _DMA IP介绍参考《pg021》写的性能接口介绍

四、PCIe XDMA

Xilinx PCIe XDMA使用指南

为什么使用PCIe传输

在FPGA需要和处理器打交道时,PCIe具有很多优势。

(PCIE学习应用教程)1.使用XDMA测试FPGA与PC通信讲了三种方式和xdma的配置

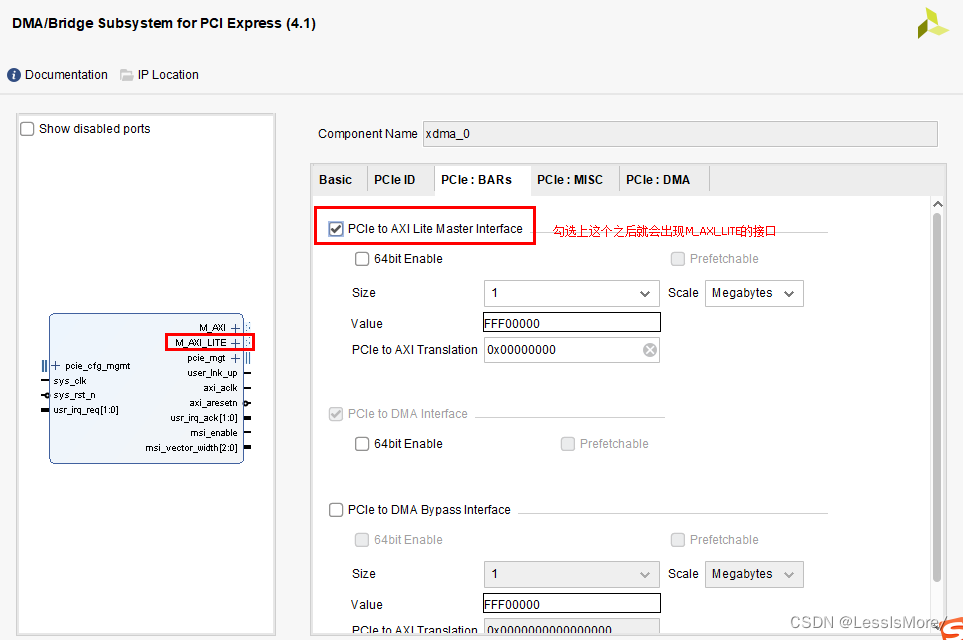

Xilinx的Vivado中,有三种方式可以实现PCIE功能,分别为:

1、调用7 Series Integrated Block for PCI Express IP核,这是最基础的PCIE IP核,使用起来较复杂。

2、调用AXI Memory Mapped To PCI Express IP核,对7 Series Integrated Block for PCI Express进一步封装,可以使用Example Design直接运行;但需要添加DMA IP核实现DMA数据传输。

3、调用DMA/Bridge Subsystem for PCI Express (PCIe) IP核,别名XDMA,对PCIE和DMA一起进行了封装,也可以直接使用Example Design直接运行。

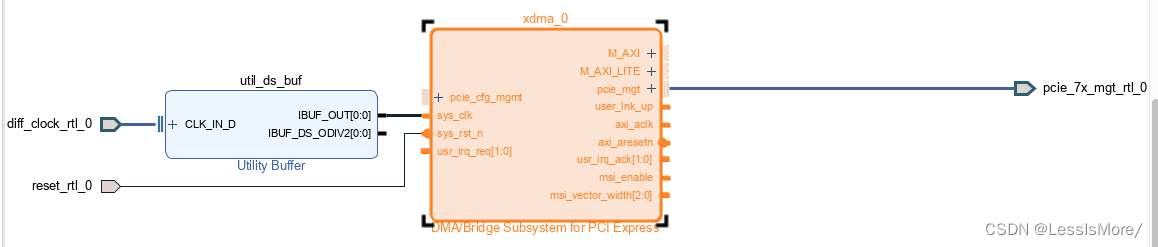

下图的其他模块和接口都是自动出来的

五、DDR

资料参考

1、Xilinx FPGA平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了这篇写的很全面详细

2、快速上手Xilinx DDR3 IP核----汇总篇(MIG) 该系列介绍了Xilinx 控制DDR3的IP核----MIG IP核的基本构成和使用方法,在MIG 接口的基础上在外部封装了FIFO,使得操作时序更加简单,并用此方法实现了几个练手的小项目。

3、FPGA ——DDR基础概念详解_居安士的博客读写操作引脚有详细说明

4、DDR全接口说明: 知乎:基于FPGA的DDR3设计(3)MIG IP核的使用教程

5、

DDR SDRAM介绍

DDR=Double Data Rate双倍速率,DDR SDRAM=双倍速率同步动态随机存储器,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。

SDR SDRAM采用单端(Single-Ended)时钟信号, 在一个时钟周期内只传输一次数据;而 DDR由于工作频率比较快,采用可降低干扰的差分时钟信号作为同步时钟。在一个时钟周期内可以传输两次数据,它能够在的DQS上升沿和和下降沿各传输一次数据。

相对比于DDR,DDR2的时钟加速,是DDR的两倍,DDR3的时钟是DDR的四倍

DDR存储机制

DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑Bank(Logical Bank,下面简称Bank)。

目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”。

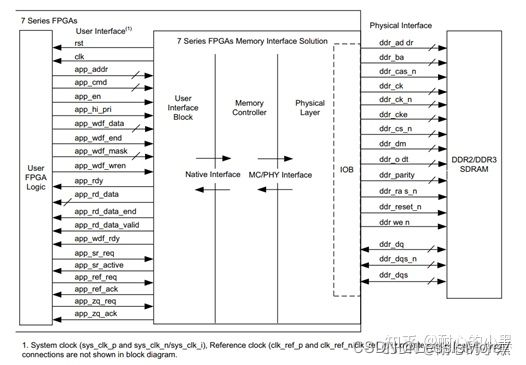

MIG ip核

MIG(Memory Interface Generators) IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的 控制流程。MIG IP 核对外分出了两组接口,左侧是用户接口,就是 用户(FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG。右侧为 DDR 物理芯片 接口,负责产生具体的操作时序,并直接操作芯片管脚。这一侧用户只负责分配正确的管脚,其他不用关心。

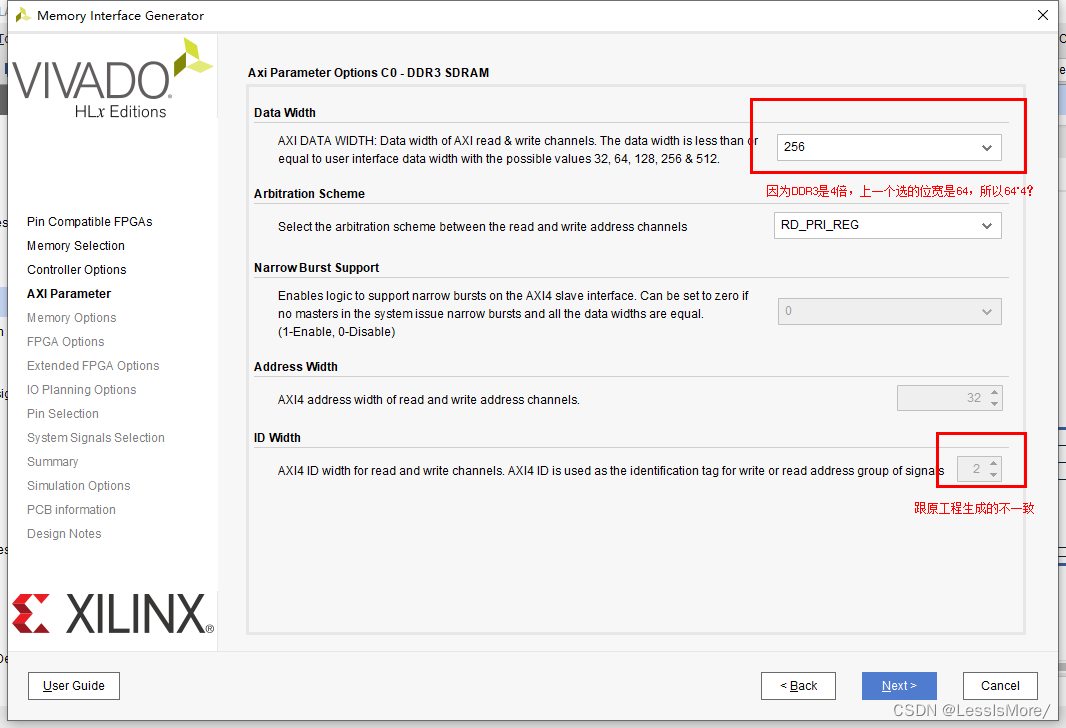

MIG IP核对外提供了两类接口:Native接口和AXI4接口,把我们从DDR3芯片自身复杂的接口和时序中解放了出来。 Native接口比较简单,而且效率很高,但是不如AXI4接口通用性强。本次工程中使用的是AXI4接口。

基于Vivado MIG IP核的DDR3控制器(DDR3_CONTROL)有下图和ip核的对应配置

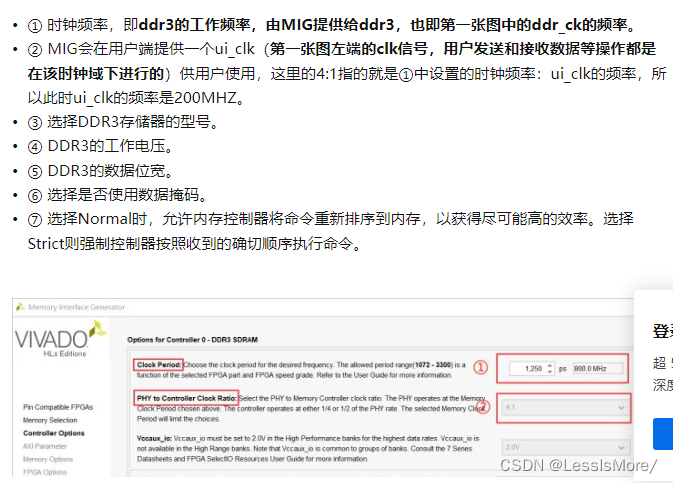

下面介绍MIG在vivado中调用时的配置,前面简单的就不说了,重点来说时钟设置。

以下内容大多参考:FPGA——调用DDR的IP核(MIG核)

这个讲解的更详细:快速上手Xilinx DDR3 IP核(1)----MIG IP核的介绍及配置(Native接口)有ip核的接口介绍和配置介绍 。其中提到:Clock Period:DDR3 芯片运行时钟周期,这里选400M,实际传输频率800M(上下沿双触发)?那用户4:1是100?

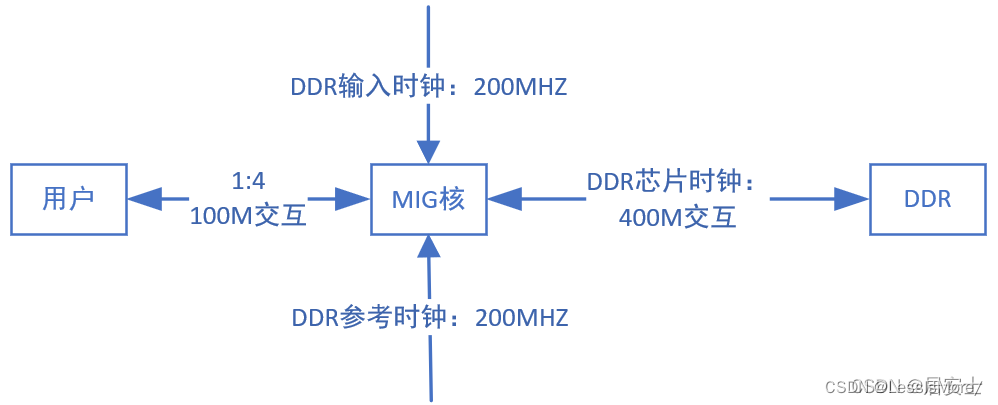

1、DDR的ddr_ck与用户的ui_clk

上图中的800MHZ是由MIG核送给FPGA外的DDR3芯片的

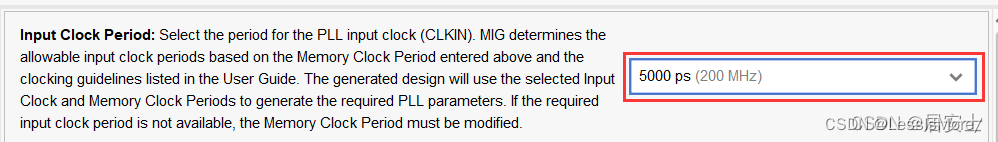

2、给MIG ip核的输入时钟与参考时钟

※DDR输入时钟:此处选择的时**提供给MIG核的时钟**

建议选择200MHZ和参考时钟(固定为200MHZ)相同

注意,这个地方只选了输入时钟的频率,并没有让选输入时钟的形式,输入时钟形式在下一页面选择

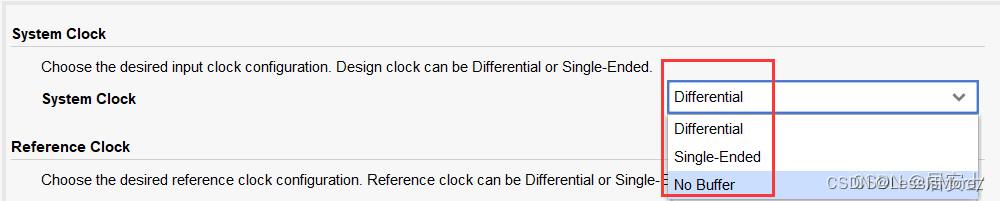

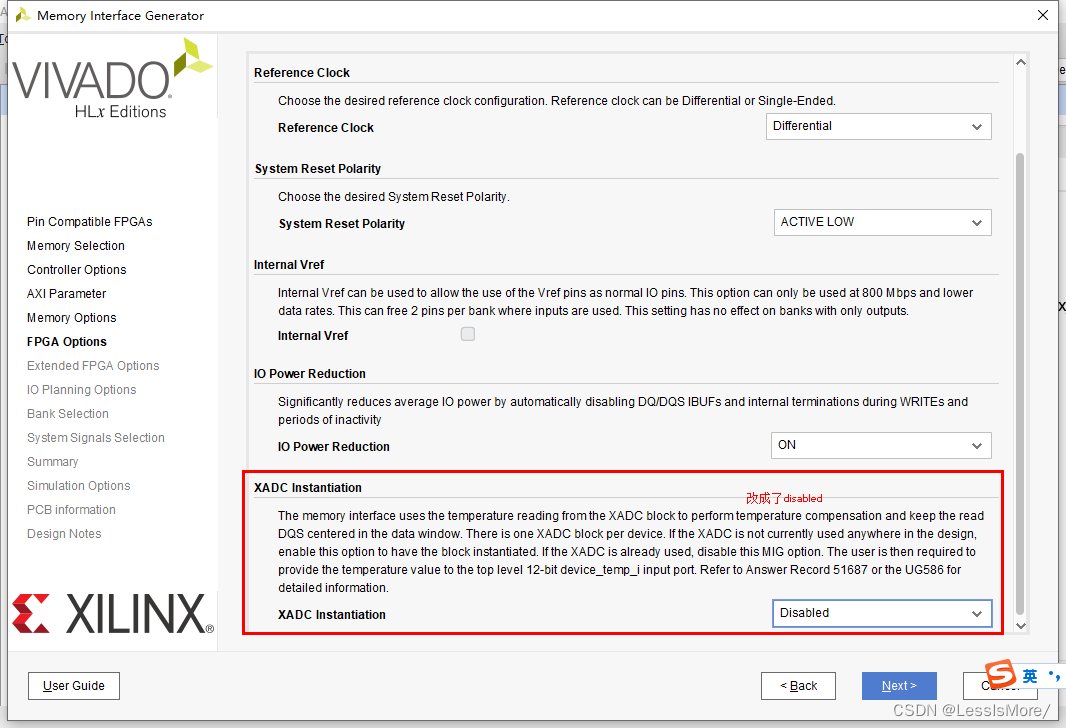

下面就是※MIG核输入时钟的形式选择

输入MIG核的时钟可以从FPGA外部直接给,也可以从FPGA内部给,如果时钟从外部给,那么可以选择差分,如果时钟从内部给,那么选no buffer(没有buffer计)或者单端。

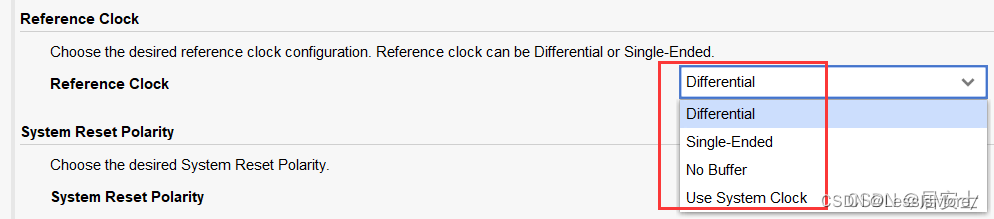

下图为※MIG参考时钟(为200MHZ)

这里面的四个时钟(DDR芯片时钟,DDR输入时钟,DDR参考时钟,用户时钟)是非常叫人迷惑的,下面画张图帮助理解

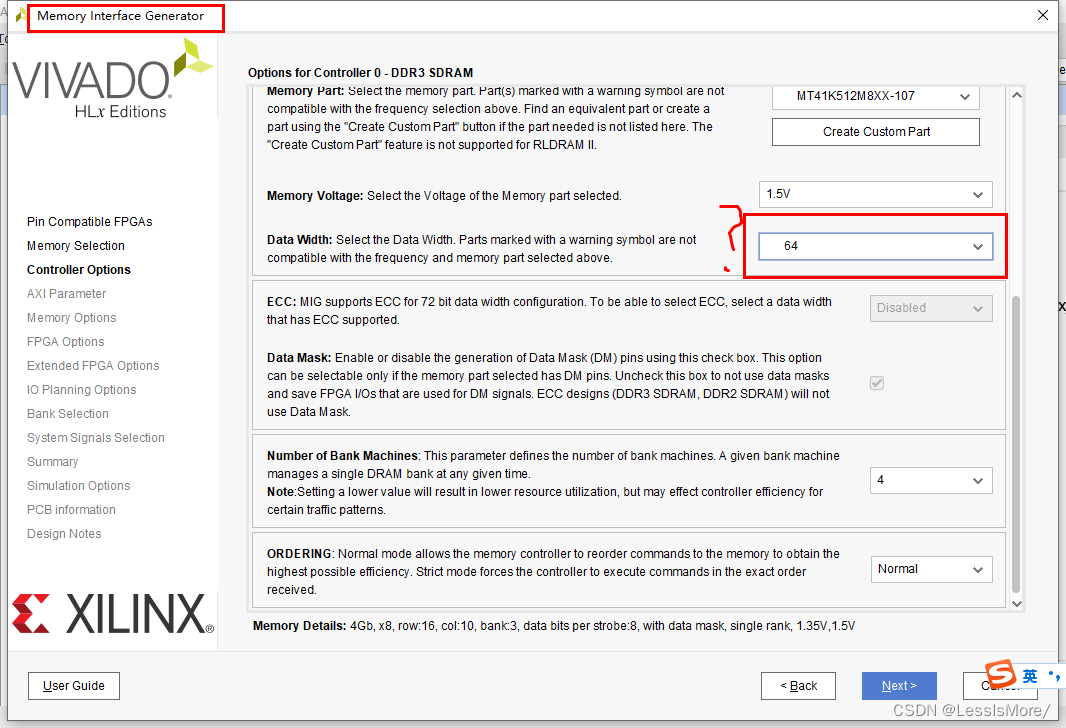

3、数据位宽?(待研究)

2024

2024

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?