第三章 总线技术

一、概述

总线:连接多个部件(在现在总线概念中,多个最少亦可以是两个)的一组公用信息传输线,是各部件共享的传输介质。

1、两种互连方式

(1)专用互连

各部件之间两两互连,建立独享的专用信息传输通路,可以实现速度最大化(就考虑互连的两个部件),但系统扩展新部件时,难以实现(需要考虑新部件与原来所有部件之间的关系)。

(2)共享互连

各部件之间有一组共享的公用传输线,各部件其实都连接到总线上,此时扩展部件易于实现(新部件只需挂接至总线即可),但总线的速度相对要慢(需适应总线上最慢速的部件)。

注意:现在的总线已经是一个泛化的概念,有些两两互连的传数线也称为总线,例如CPU和主存之间通常会有一组专用传输线(就是两个部件互连),这组线就称为主存总线。

2、总线的分类

(1)按所传输的信息

地址总线(Address Bus,AB):传输地址信号的总线

数据总线(Data Bus,DB):传输数据信号的总线

控制总线(Control Bus,CB):传输控制信号的总线

(2)按传输方式

并行总线(一次传输多位数据)、串行总线(一次仅传输一位数据)

(3)按所连接的部件

系统总线(亦称处理器总线):互连系统中主要功能部件的总线,一般主要连接处理器和主存,特点是时钟频率高、线宽大

输入输出总线(亦称I/O总线):连接主机和输入/输出设备的总线,特点是时钟频率低、线宽小

(4)按在系统中的位置

片内总线:位于处理芯片内部的总线,负责寄存器之间和寄存器与运算器之间数据传输

底板总线(亦称系统总线或内总线):计算机系统主板上的总线,负责处理器、主存以及I/O接口之间的互连

板间总线(亦称I/O总线):用于主机与I/O接口的互连,主要反映为主板上的扩展插槽

通信总线(亦称外总线):负责计算机系统之间或计算机与外围设备之间的连接

3、总线的特性

所谓的总线的特性,即如何来描述总线

(1)物理特性(亦称机械特性)

指总线在连接方式上的一些特性,如插头和插座使用标准(几何尺寸、形状、引脚个数以及排列的顺序)

(2)电气特性

指总线的每一根传输线上信号的传递方向和有效的电平范围

传递方向的三种模式

单工:传递方向不可改变,仅按预先设定的方向传递

半双工:传递方向可以改变,但某个时间段仅能按一个方向传递(仅一个信道)

全双工:可两个方向同时传递(实质上是两个信道)

TTL逻辑电平

“0”用+5v电平、“1”用0v电平

(3)功能特性

指总线中每一根传输线的功能

举例:

D0 —D31(数据线) //数据线32根,对应32位机

A0 —A31(地址线) //地址线32根,对应寻址空间4GB

CLK(时钟) RST(复位)

INTR(中断请求) INTA(中断响应)

RD(读) WR(写)

HRQ(总线请求) HLDA(总线允许)

(4)时间特性(亦称过程特性)

指总线中任一根线在什么时间内有效,具体用时序关系图描述

二、总线结构举例

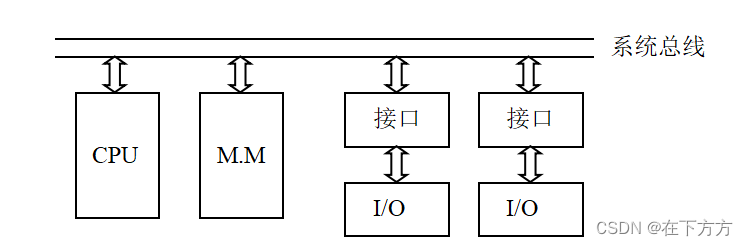

1、单总线结构

- 早期DEC公司的PDP-11/20采用,仅一条共享总线

特点:共享总线,扩展容易,但I/O总数有上限(受总线负载能力限制)

总线速度由最慢设备决定(木桶原理),总线利用率低

正常的I/O模式,即I/O先传数给CPU,CPU再把数传给主存(不存在DMA)

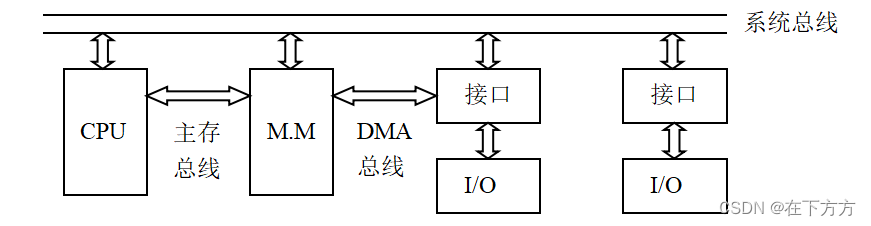

2、多总线结构(系统总线+局部总线) - 系统总线之外的总线均可称为局部总线

上图在CPU和主存之间引入一条主存总线,可以实现主存和CPU之间的高速传输数据;同时在高速I/O和主存之间引入一条DMA总线,可以实现高速I/O和主存之间的高速传输数据。其它低速I/O则通过系统总线和CPU进行低速传输数据。

特点:引入局部总线,可以高速传输数据,局部总线一般为互连总线,不易于扩展

3、总线的层次结构 - 现代计算机系统普遍采用

- 实现不同的总线速度和I/O设备的扩展

- 可以假想下层为一个统一的I/O系统,总线之间通过桥接器(Bridge)连接

三、总线控制

1、总线仲裁(Bus Arbitration) //决定总线归谁使用

- 总线控制器:需要有一个控制器来决定总线的使用权和对总线进行管理

- 控制方式

集中式——控制逻辑集中在一处(早期通常在CPU内部)

分布式——控制逻辑分散到各个部件或设备上

主模块(Master Module):拥有总线控制权的部件

从模块(Slave Module):被主部件访问的部件

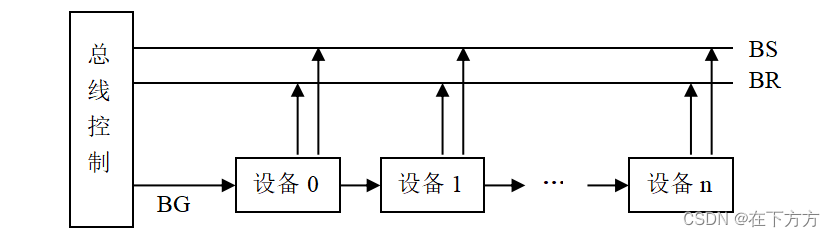

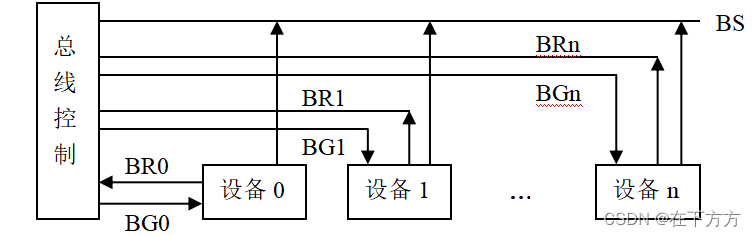

(1)链式查询方式

其中BS(Bus Busy)为总线忙,BR(Bus Request)为总线请求,BG(Bus Get)为总线获得。

特点:结构简单,扩展容易(不管设备为多少,仅需三根控制线即可)

对故障敏感(某个设备出错,其后的所有设备均无法操作)

远端响应机会小(存在饥饿现象),远端响应延迟大

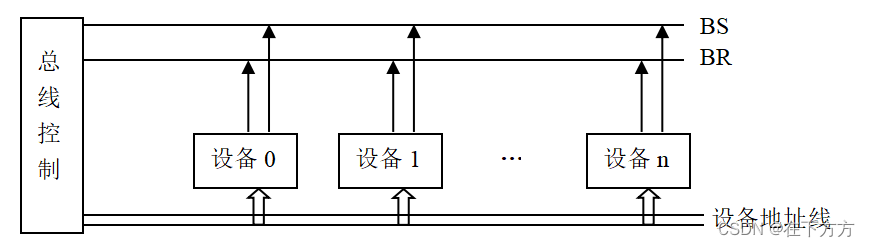

(2)计数器定时查询方式

用一组设备地址线替代原来的BG,由于取消了BG,所以故障敏感特性消失,只有设备地址线上的地址值与请求设备的编号相同时,设备才能获得总线。

用一组设备地址线替代原来的BG,由于取消了BG,所以故障敏感特性消失,只有设备地址线上的地址值与请求设备的编号相同时,设备才能获得总线。

特点:扩展受地址线位数限制(如设备地址线仅3位,则最多设备数为8个)

对故障不敏感

各设备优先级相同(请求时设备地址线数值随机)

响应的延迟可能小,亦可能大(响应时间无法预期)

(3)独立请求方式

每一个设备均有一组BR和BG,所以响应时间短,但硬件开销较大(线数多),总线控制器内需要一个优先级排队器。

(4)固定时间片

一种分时系统模式,即每个设备处理一定时间,时限到了立刻让出总线使用权。

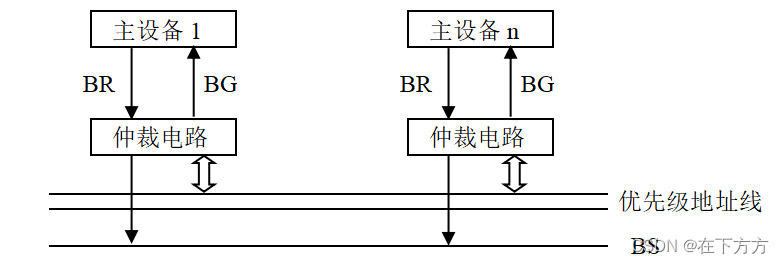

(5)分布式总线仲裁方式

- 前面几种均为集中式仲裁,这是一种分布式仲裁

各设备有自己的仲裁电路,操作时向共享的优先级地址线发自己的优先级号,然后回收地址线上的数值,根据回收的数据决定是否使用总线。(具体的判断规则略)

2、总线通信控制 - 数是否送到总线上、对方是否接收、数是否撤销、下一次是否开始

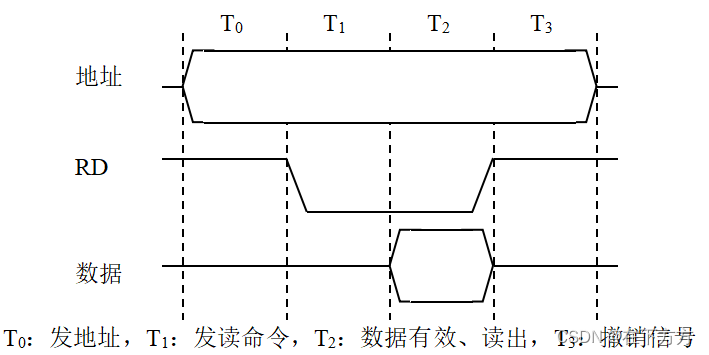

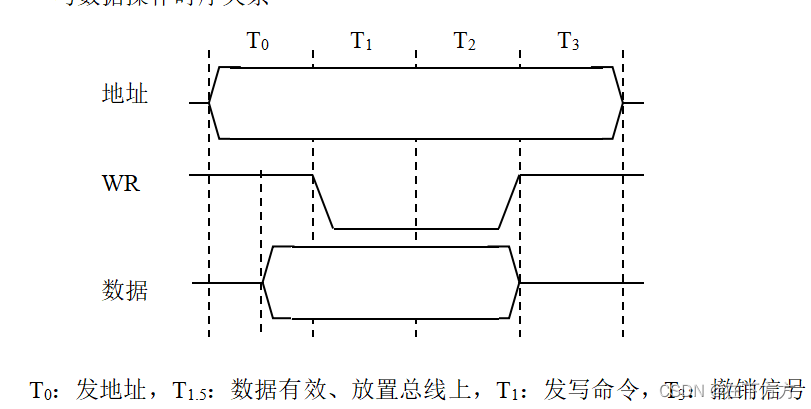

(1)同步通信 - 无需感知对方,按固有时钟周期来处理

- 时钟可共享同一个,亦可彼此各有一个(但使用前需协调同步)

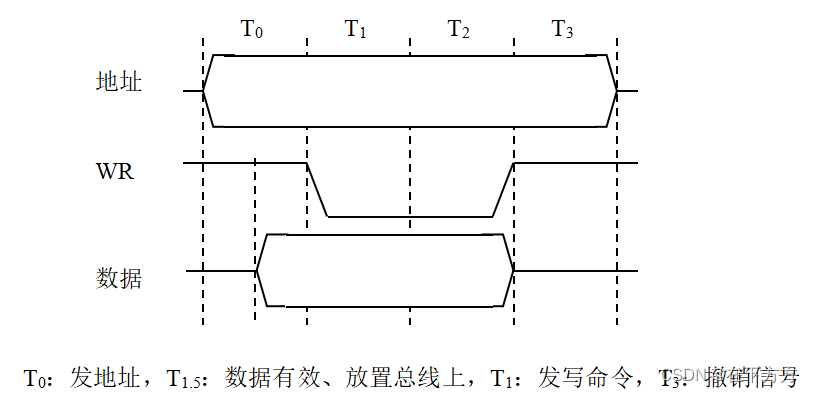

- 读数据操作时序关系

- 写数据操作时序关系

特点:配合简单一致、信号传输速率高、时钟的频率向慢速设备看齐(对快速设备而言效率较低)

特点:配合简单一致、信号传输速率高、时钟的频率向慢速设备看齐(对快速设备而言效率较低)

(2)异步通信 - 需要感知对方的操作,一般用一组应答来进行双方的联络信号

- 单边控制(只一端控制,另一端无需回应) //控制简单,但容易出错

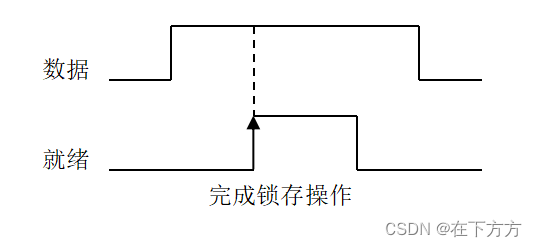

a、源部件控制(即发送端)

发送端送出数据,同时发数据就绪状态(用该状态信号锁存数据给对方端),理想情况是接收端收到就绪状态,取走数据(接收端不发回应信号)。

缺点:存在“毛刺”脉冲干扰,造成错误数据锁存

发送端不能确切知晓接收端是否把数据取走(如接收端未把数据取走,而发送端又发新数,则原数据丢失)

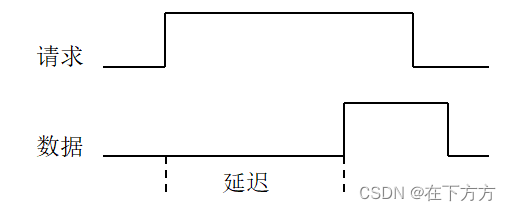

b、目的部件控制(即接收端)

接收端发出数据请求,延迟一定时间(接收端认为理想情况下,发送端应该接收到该信号并已进行了处理),然后取走数据。整个过程不接收发送端任何信号。

缺点:无法确定发送端是否真的发送了数据(只是假定正常情况下,延迟如此长的时间发送端一定响应) - 双边控制(一端请求,另一端需要回应) //安全性要比单边控制高

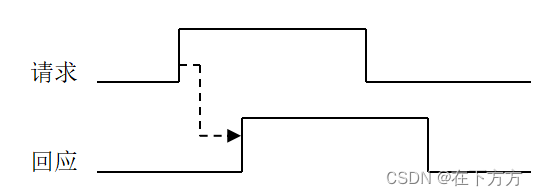

a、不互锁方式

只存在一个递推关系,即回应信号是在接到对方的请求信号发出的。请求端不接收回应信号,而是延迟一段时间(认为时间足够长,对方足够响应)后自动撤销请求信号,同时回应信号也是延长一段时间后自动撤销。 //实质上就是一种单边控制

问题:如果对方没有回应,结果是数据丢失

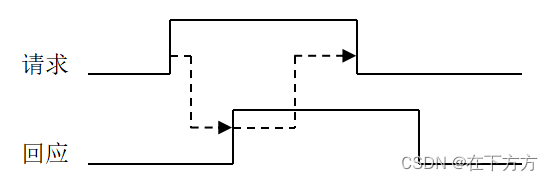

b、半互锁方式

存在两个递推关系,回应信号是在接到对方的请求信号发出的,同时请求信号是在接到对方的回应信号后撤销的。最后回应信号是延长一段时间(认为时间足够长,对方足够响应)后自动撤销。 //安全性更好

问题:如果对方没有接到回应信号,而本方回应又撤销,结果是对方一直请求

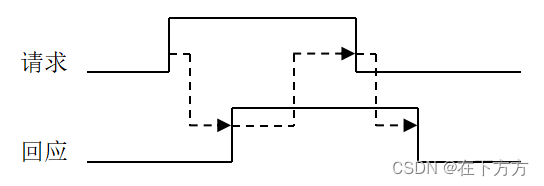

c、全互锁方式

存在三个递推关系,回应信号是在接到对方的请求信号发出的,同时请求信号是在接到对方的回应信号后撤销的,最后回应信号是在接到对方的请求信号撤销后再撤销。此种方式安全性最高,但控制麻烦,在网络通信中采用较多。

注意:计算机系统中永远满足墨菲定律(凡可能出错的地方,终将出错)

四、总线性能指标

1、总线宽度——数据总线的位数

2、工作时钟频率——控制总线中时钟信号线所提供的频率

- 处理器内部总线的频率称为内频

- 系统总线的频率称为外频

3、单个数据传送周期数 - 正常方式:传送时先送地址,然后再送数据(即两个工作周期送一个数)

- 突发方式:只第一个数采用正常方式(两个工作周期),后续数据只需一个工作周期即可(通常满足局部性原理,不需再送地址,地址自动加1即可)

4、负载能力——连接部件数目的多少(平均值一般为3个)

5、标准传输率——即传输带宽

标准传输率=总线宽度×工作频率 //注意不是时钟频率

注意:传输带宽为理论上的最大值(即总线的峰值)

例:某系统一个周期内传4字节信息,一个总线周期占两个时钟周期,总线时钟频率为10MHz,则总线的传输带宽是多少?

4B×(10MHz÷2)=20MB/s

注意:总线时钟周期,即时钟信号线一次时钟震荡的时间值

总线周期,即传输一次数据的时间值,一般需要几个总线时钟周期

例:总线时钟频率为100MHz,总线宽度32位,每传输一次地址或一次数据均只需一个总线时钟周期即可,支持突发传输,则传输128位需多长时间?

一个总线时钟周期TC=(1/100MHz)=10ns

传128位需传数据(128÷32)=4次

第一次传数需传地址和数据,即需2TC,后三次不需要传地址,则只需3TC

共需2TC+3TC=5TC=50ns

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?