实验二 基于FPGA的分频器的设计

1. 实验目的:

(1) 掌握QuartusⅡ软件的层次型设计方法;

(2) 掌握元件封装及调用方法;

(3) 熟悉FPGA实验平台,掌握引脚锁定及下载。

2. 实验任务:

(1) 基本任务:设计一个分频器,输入信号50MHz,输出信号频率分别为1KHz、500Hz及1Hz。

(2) 拓展任务1:用按键或开关控制蜂鸣器的响与不响。

(3) 拓展任务2:用按键或开关选择1KHz和500Hz两种不同频率信号驱动蜂鸣器。

基本任务:

(1)设计思路

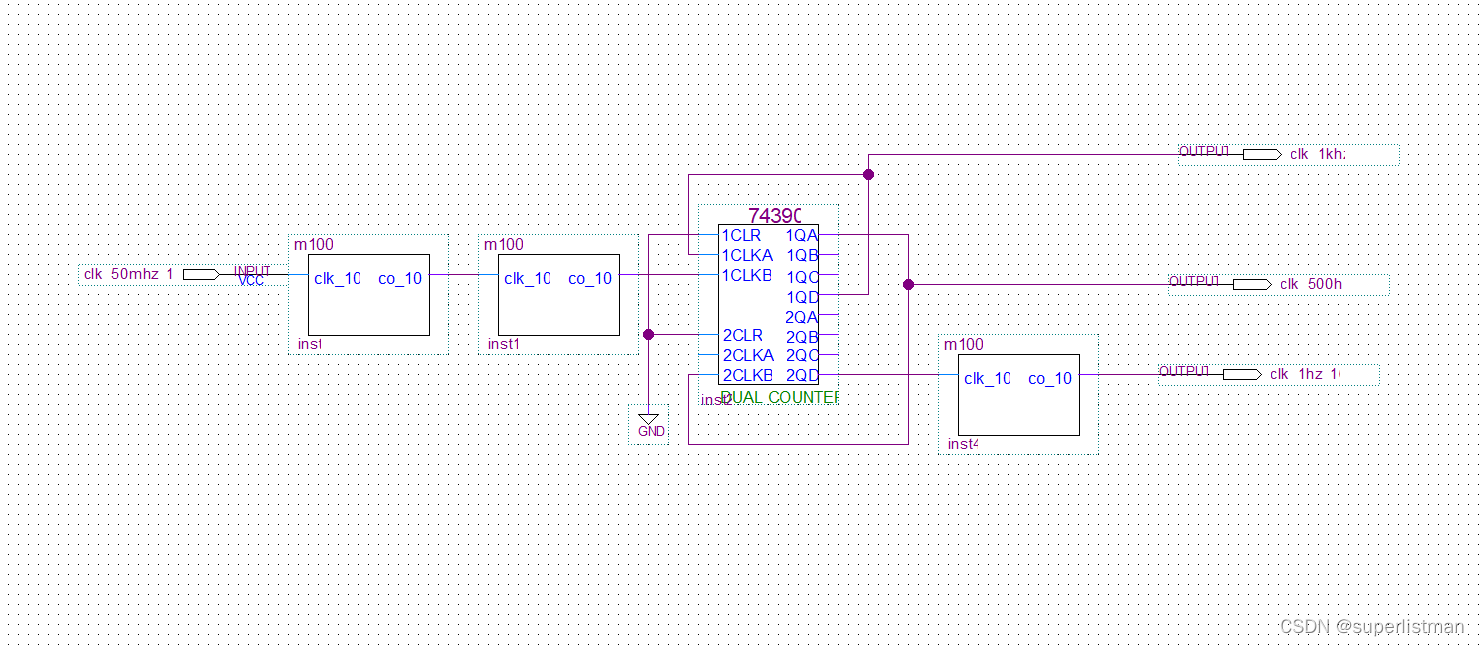

实验平台上提供有两个时钟信号clk0和clk1,频率均为50MHz,通过2、5、100分频,对输入信号进行逐级分频。2、5、100分频功能采用74390实现。

(2)电路设计

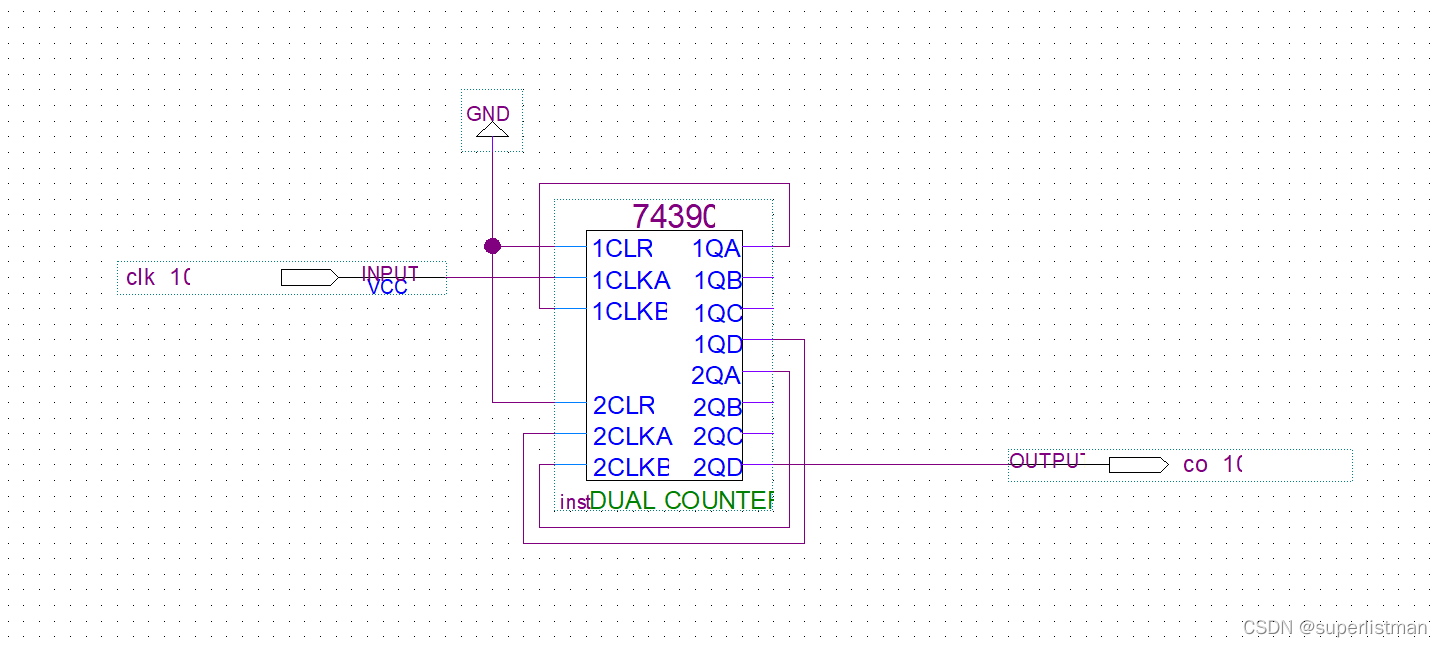

1.模100计数器设计

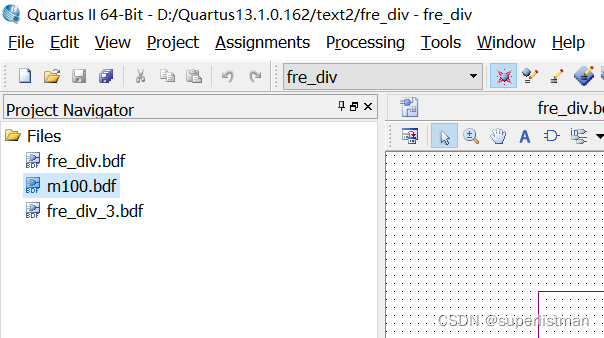

2.将m100计数器封装

方法:选中右侧的m100文件

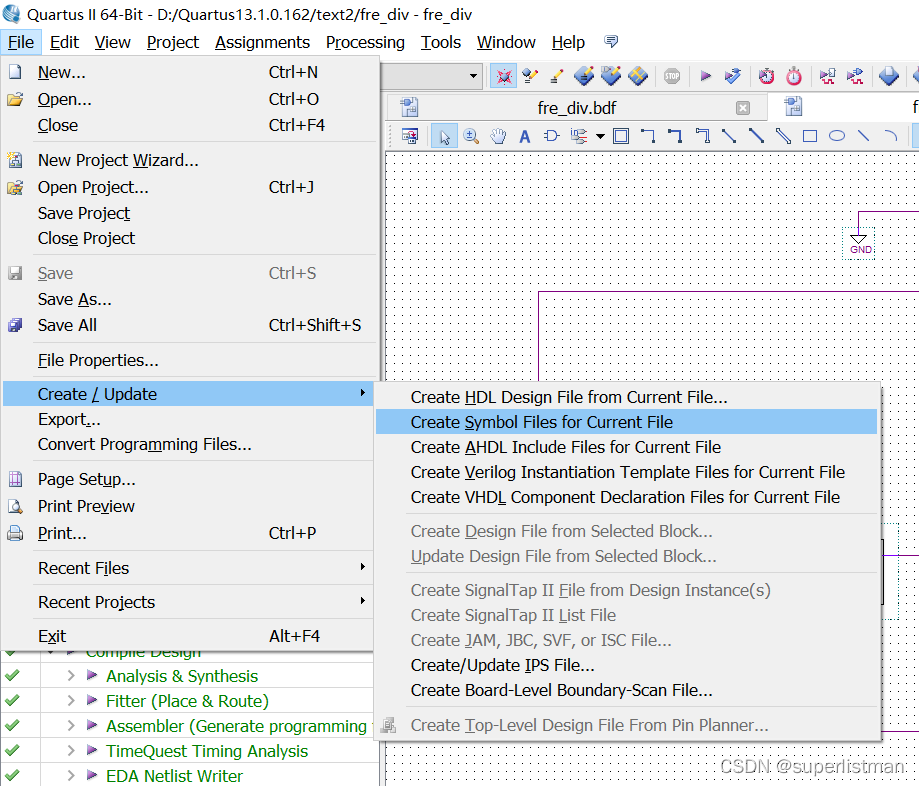

点击File->Create->Create Symbol Files for Current File

选择储存位置,一定要和工程文件在一个文件夹里

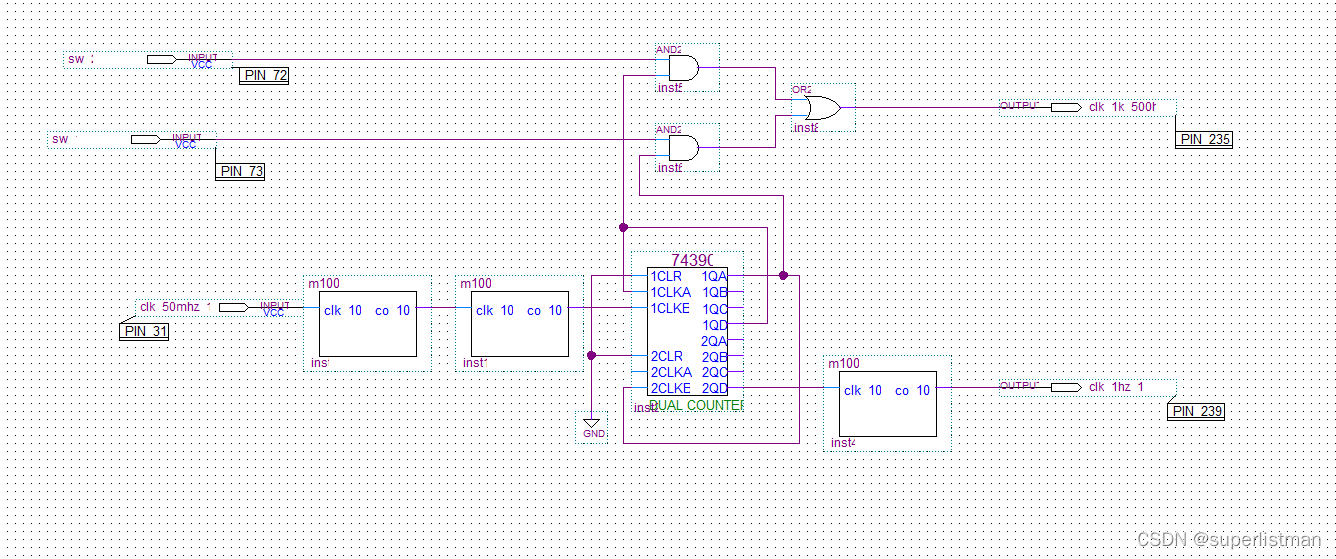

3.分频器设计电路图

拓展任务1和2:

用按键或开关控制蜂鸣器的响与不响。

(1)任务1加个开关即可

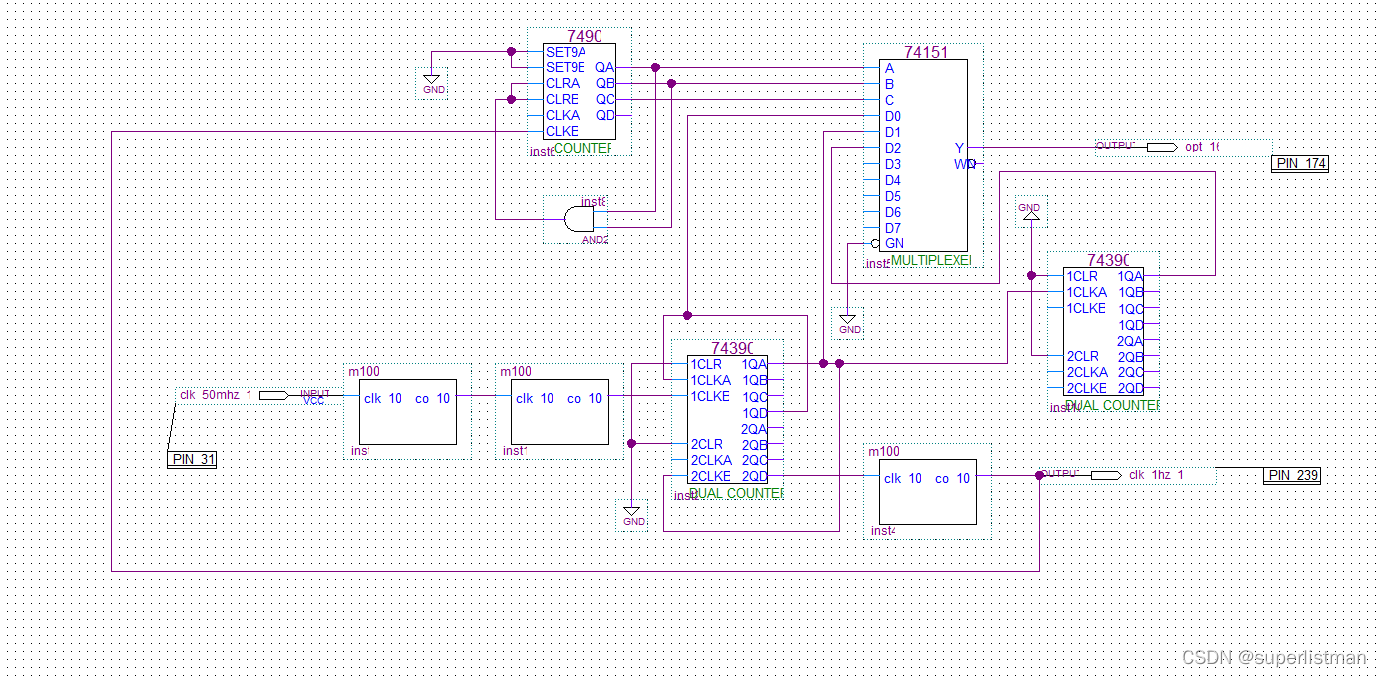

(2)任务2如下图

拓展任务3

自动在三个频率间切换

用分频器的1Hz输出信号作为时钟

工程文件下载连接

求赞!!!

154

154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?