实验三 基于FPGA的数码管动态扫描电路设计

源文件的链接放在最后啦

- 实验目的:

(1) 熟悉7段数码管显示译码电路的设计。

(2) 掌握数码管显示原理及静态、动态扫描电路的设计。 - 实验任务:

(1) 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选;

(2) 基本任务2:利用FPGA硬件平台上的4位数码管显示模10计数结果(以1S为节拍);

(3) 基本任务3:利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);

(4) 拓展任务1:对7448译码结果中的“6”和“9”进行补段;

(5) 拓展任务2:用按键控制计数器从0-9计数,4位数码管显示计数结果;(注意按键消抖)

(6) 拓展任务:3:dig_select、decoder和code_select三个模块做波形仿真。(注意输入设置)

基本任务一:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选;

1、实验原理

使用decoder模块控制数码管的显示功能,输入二进制码,输出对应的数码管显示数字。

dig_select模块负责选择哪一个数码管显示数字,add端输入二进制码,如果输入的频率特别高的话,人眼就分辨不出来一个个显示的过程了,看起来就是六个数码管都在亮。

2、电路模块设计

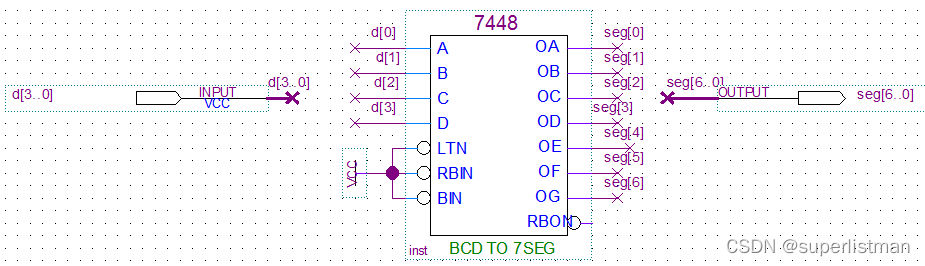

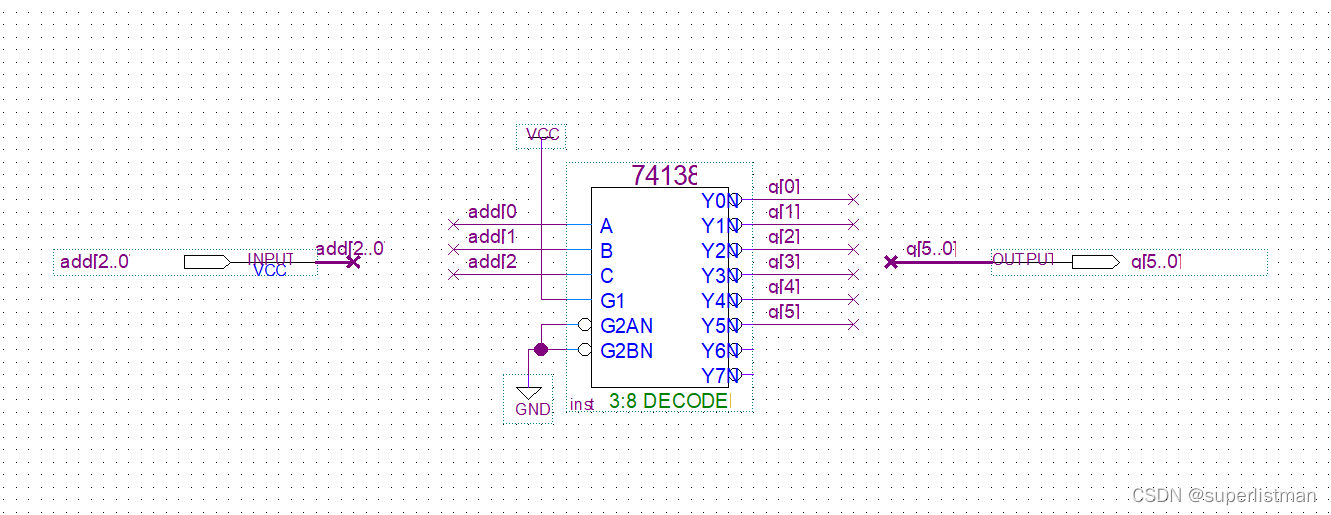

(1)decoder模块

(2)dig_select模块

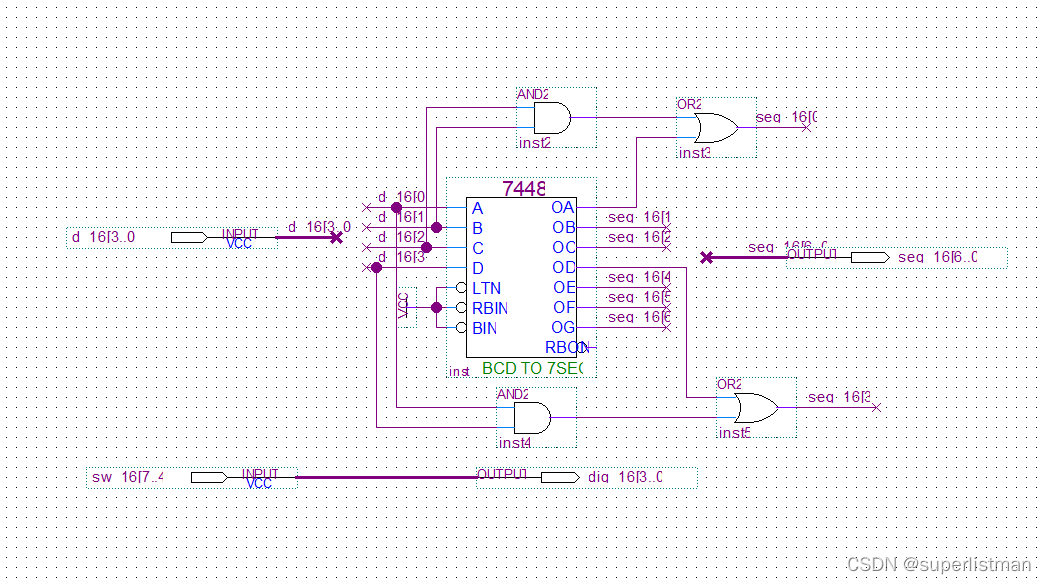

拓展任务一:对7448译码结果中的“6”和“9”进行补段;

1、电路模块设计

(1)补段后的decoder模块,原本6和9显示的时候会少一段没有显示,加上外部与非门后就可以完整显示了。

基本任务二:利用FPGA硬件平台上的4位数码管显示模10计数结果(以1S为节拍);

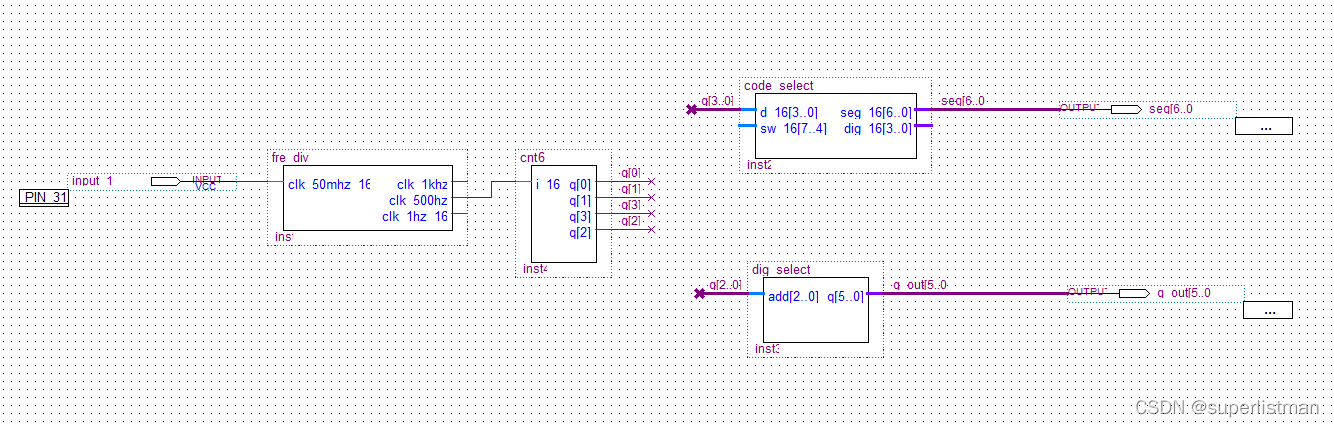

1、电路模块设计

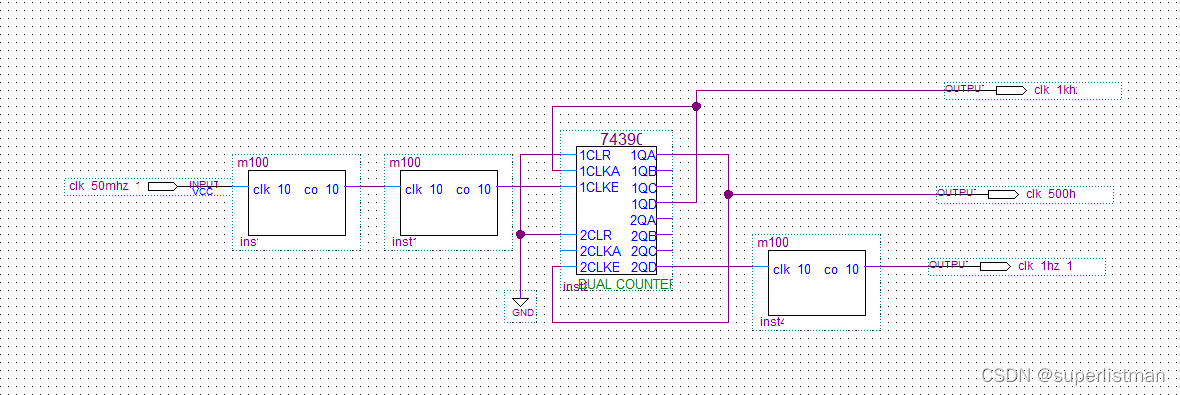

(1)fre_div模块(如果不知道原理可以看我的上一篇文章实验二)

(2)基本任务一的decoder和dig_select模块(在上面,用那个补过段的)

(3)模六计数器cnt6(实验一里有)

(4)整体设计

拓展任务二:用按键控制计数器从0-9计数,4位数码管显示计数结果;(注意按键消抖)

1、电路模块设计

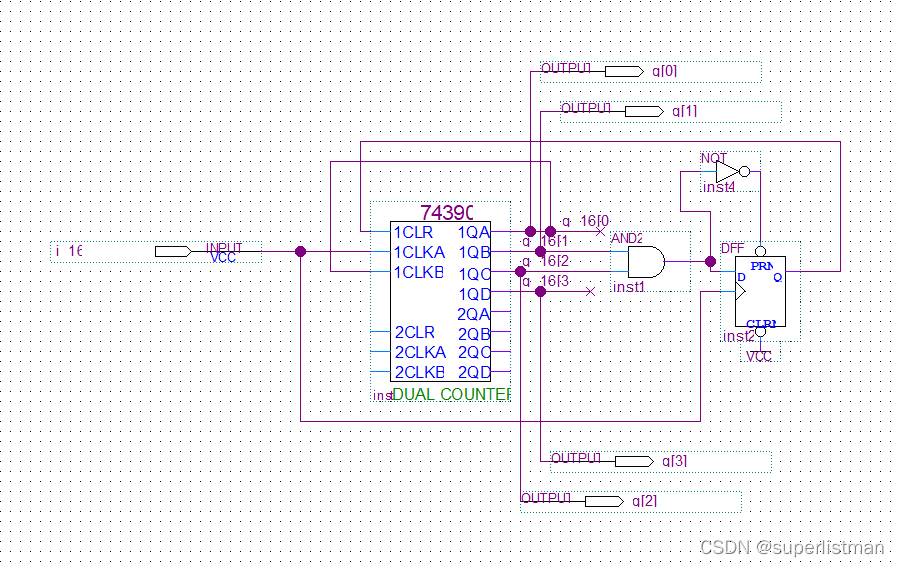

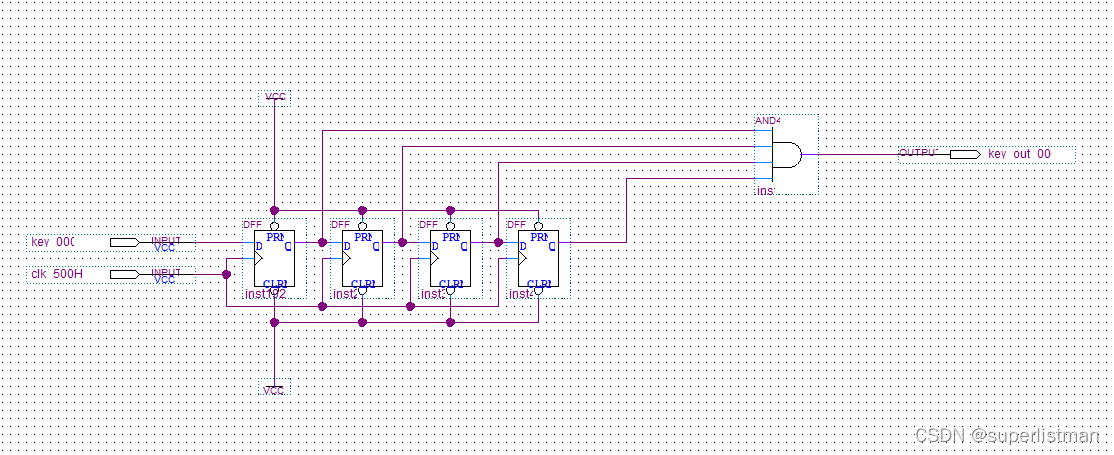

(1)按键消抖key_debounce模块

(2)原理

利用D触发器的延时特性,将每一个D触发器(延时不同)的输出端相与,仅当所有D触发器都输出为1的时候,消抖模块才输出为1,这样就可以将按键抖动的部分(有1也有0的部分)跳过,达成消抖的目的。

后面还可以接更多的D触发器,如果效果不好的话。

clk端要接一个500Hz的时钟

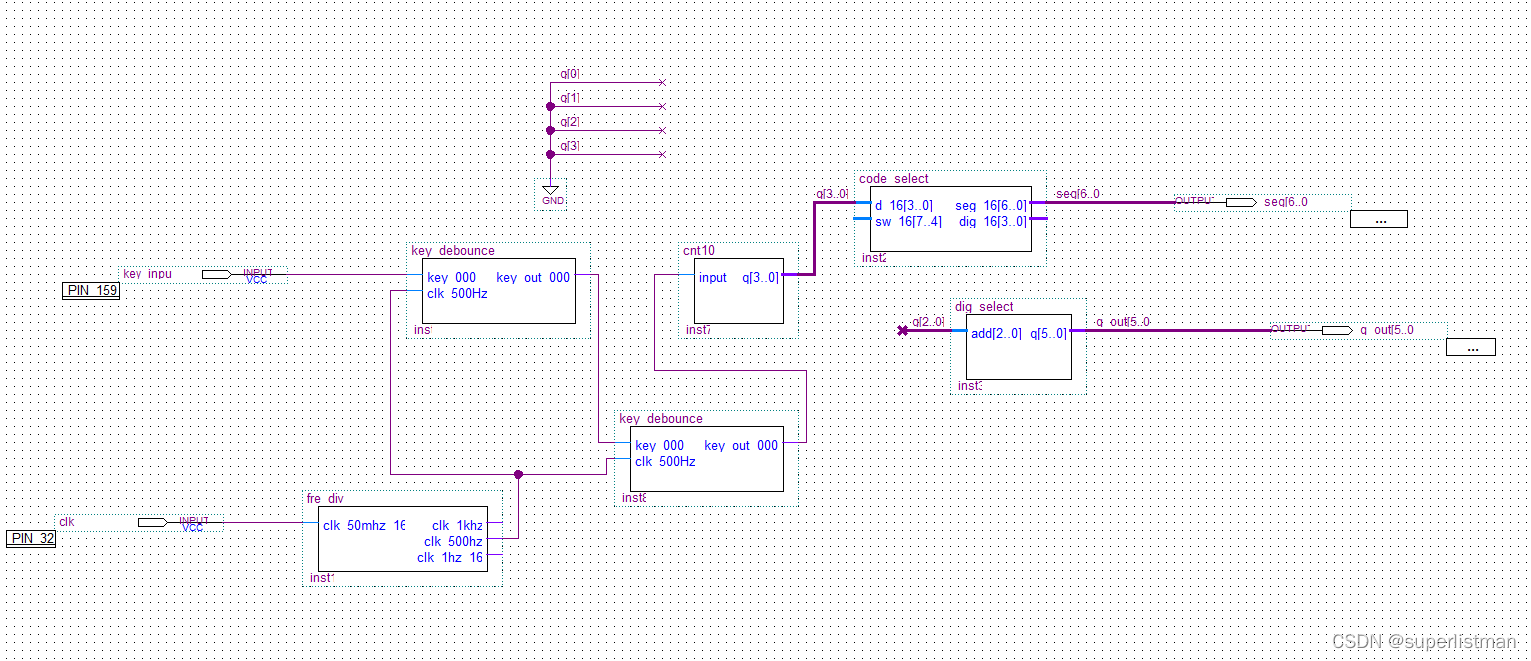

(3)整体设计

接下来就和上面的差不多了。

我这里接了两个消抖模块是因为一个好像效果不太好。

基本任务3:利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);

1、电路设计

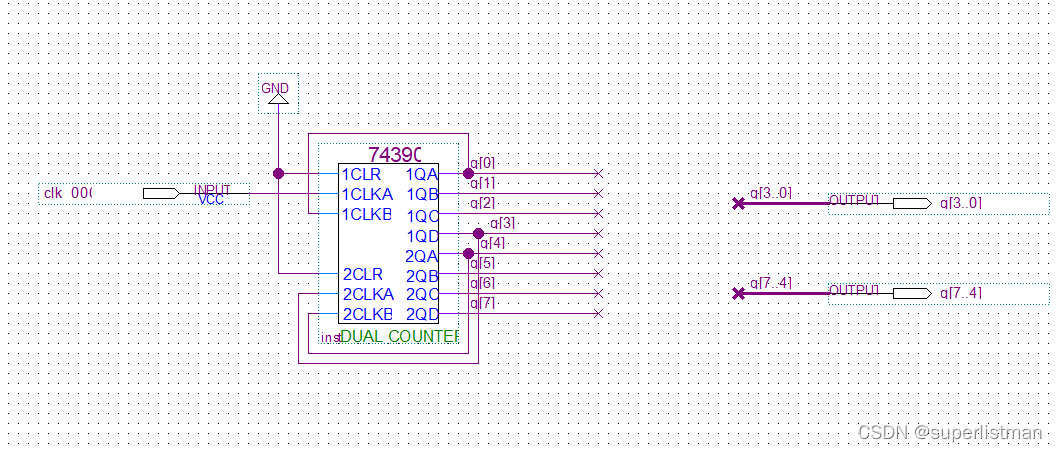

(1)实验三就有一些复杂了。要实现模100计数结果,我们首先要有一个模100计数器。

cnt100

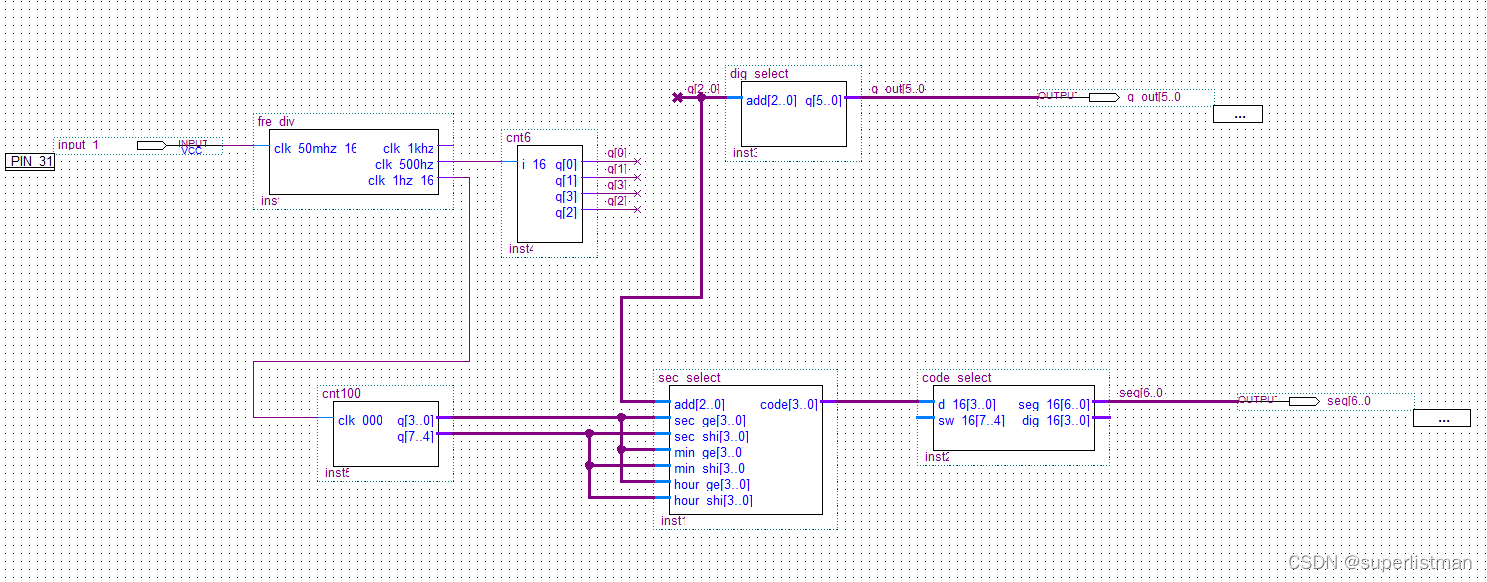

(2)第二个新模块是sec_select模块,之所以这么命名和设计是为了下面的数字电子钟做准备。

这个模块的主要作用是将每一个电子管显示不同的内容,根据基本任务二可知一次只能一个数码管显示一位数字,我们是通过加快频率使得人眼看起来是6个数码管一起显示。但是每一位都是显示的都是同一个内容,还没有分开,所以要用sec_select模块进行数据选择。我们可以看到现在有6组输入,以总线的形式输入到数选模块里来,这6组分别代表了六个数码管上显示的数字,

add端输入二进制BCD码与dig_select端保持同步,表示现在在显示的是哪一个电子管,那么code输出端就会选择相应的输入端输出。(比如add端是000,表示0号数码管显示,code端就会将D0对应的sec_ge秒的个位数字输出)

(3)整体电路连接

其他用到的还有fre_div模块、模六计数器cnt6、code_select/decoder、dig_select模块

这些在上面都已经实现了复制过来就好。

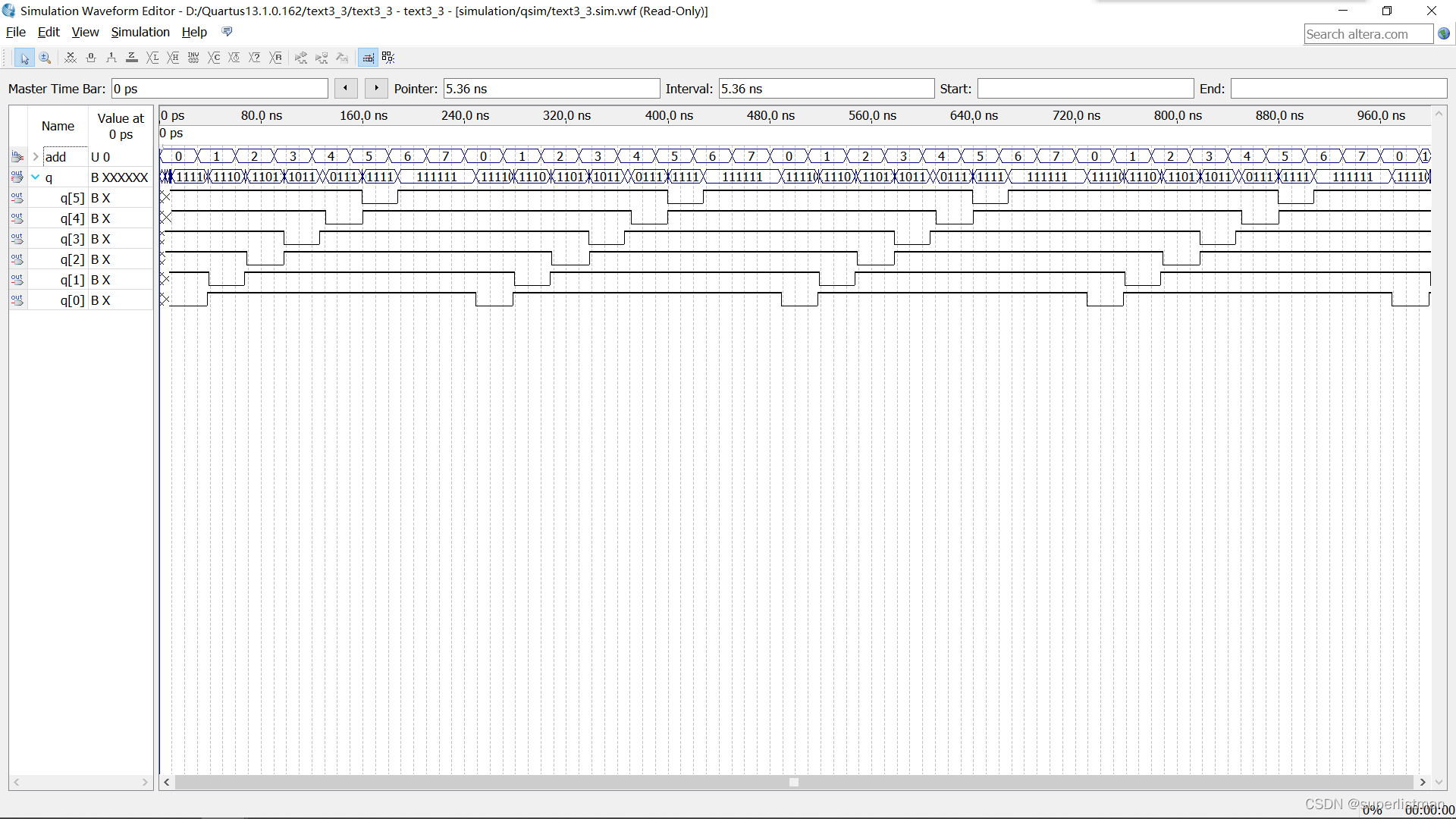

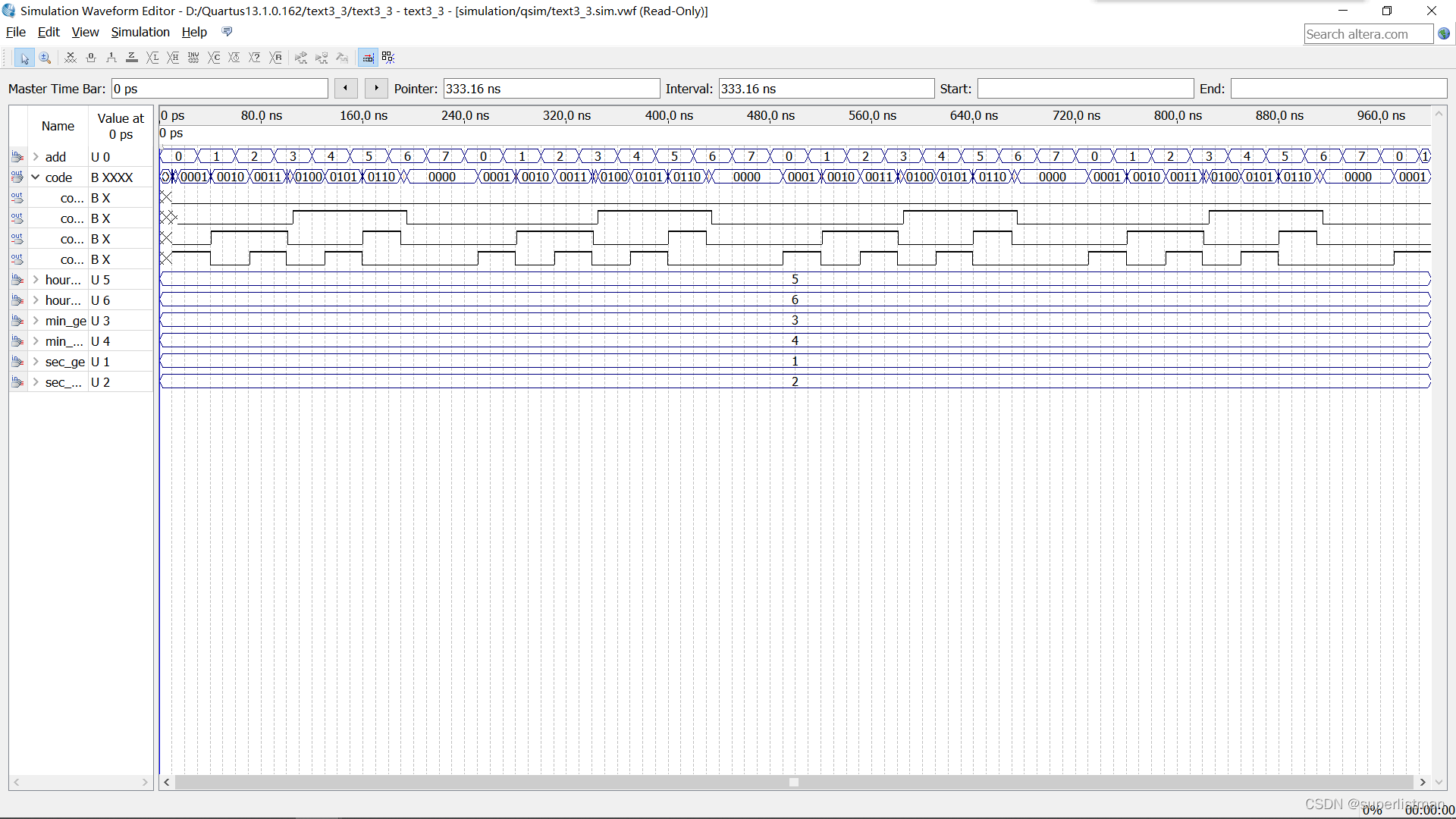

拓展任务:3:dig_select、decoder和code_select三个模块做波形仿真。(注意输入设置)

这一步就比较简单了,直接将前面已经封装好的模块生成相应的波形就行。

dig_select

decoder

sec_select

(最后的6个输入端的数字是自己输入的)

以上三个任务的源文件的链接在这里。以后也会更新更多的实验的,这么好的up主还不赶紧关注之后白嫖。☺

511

511

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?