一.查找表(Look-Up-Table)的原理与结构

采用这种结构的PLD芯片我们也可以称之为FPGA:如altera的ACEX,APEX系列,xilinx的Spartan,Virtex系列等。

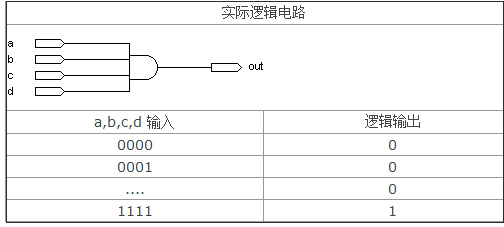

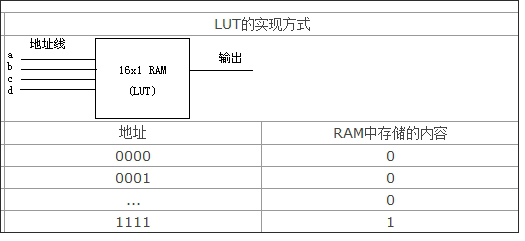

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。 目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。 当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

下面是一个4输入与门的例子,

二.基于查找表(LUT)的FPGA的结构

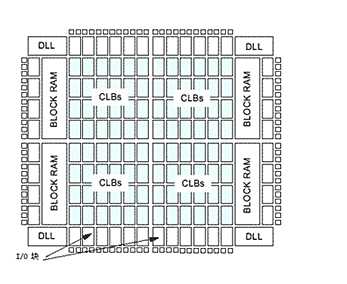

我们看一看xilinx Spartan-II的内部结构,如下图:

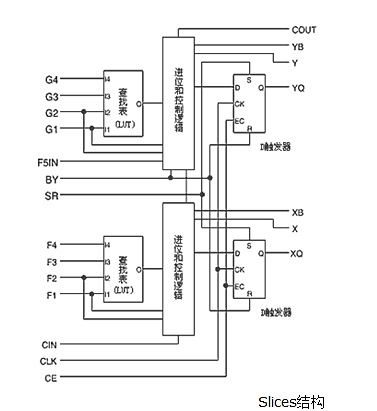

Spartan-II主要包括CLBs,I/O块,RAM块和可编程连线(未表示出)。在spartan-II中,一个CLB包括2个Slices,每个slices包括两个LUT,两个触发器和相关逻辑。 Slices可以看成是SpartanII实现逻辑的最基本结构 (xilinx其他系列,如SpartanXL,Virtex的结构与此稍有不同,具体请参阅数据手册)

FLEX/ACEX的结构主要包括LAB,I/O块,RAM块(未表示出)和可编程行/列连线。在FLEX/ACEX中,一个LAB包括8个逻辑单元(LE),每个LE包括一个LUT,一个触发器和相关的相关逻辑。LE是FLEX/ACEX芯片实现逻辑的最基本结构(altera其他系列,如APEX的结构与此基本相同,具体请参阅数据手册)

二.查找表结构的FPGA逻辑实现原理

我们还是以这个电路的为例:

A,B,C,D由FPGA芯片的管脚输入后进入可编程连线,然后作为地址线连到到LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出,这样组合逻辑就实现了。 该电路中D触发器是直接利用LUT后面D触发器来实现。时钟信号CLK由I/O脚输入后进入芯片内部的时钟专用通道,直接连接到触发器的时钟端。触发器的输出与I/O脚相连,把结果输出到芯片管脚。这样PLD就完成了图3所示电路的功能。(以上这些步骤都是由软件自动完成的,不需要人为干预)

这个电路是一个很简单的例子,只需要一个LUT加上一个触发器就可以完成。对于一个LUT无法完成的的电路,就需要通过进位逻辑将多个单元相连,这样FPGA就可以实现复杂的逻辑。

由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的,而SRAM工艺的芯片在掉电后信息就会丢失,一定需要外加一片专用配置芯片,在上电的时候,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作,由于配置时间很短,不会影响系统正常工作。 也有少数FPGA采用反熔丝或Flash工艺,对这种FPGA,就不需要外加专用的配置芯片。

三.其他类型的FPGA和PLD

随着技术的发展,在2004年以后,一些厂家推出了一些新的PLD和FPGA,这些产品模糊了PLD和FPGA的区别。例如Altera最新的MAXII系列PLD,这是一种基于FPGA(LUT)结构,集成配置芯片的PLD,在本质上它就是一种在内部集成了配置芯片的FPGA,但由于配置时间极短,上电就可以工作,所以对用户来说,感觉不到配置过程,可以传统的PLD一样使用,加上容量和传统PLD类似,所以altera把它归作PLD。 还有像Lattice的XP系列FPGA,也是使用了同样的原理,将外部配置芯片集成到内部,在使用方法上和PLD类似,但是因为容量大,性能和传统FPGA相同,也是LUT架构,所以Lattice仍把它归为FPGA。

四.选择PLD还是FPGA?

根据上一篇PLD的结构和原理可以知道,PLD分解组合逻辑的功能很强,一个宏单元就可以分解十几个甚至20-30多个组合逻辑输入。而FPGA的一个LUT只能处理4输入的组合逻辑,因此,PLD适合用于设计译码等复杂组合逻辑。 但FPGA的制造工艺确定了FPGA芯片中包含的LUT和触发器的数量非常多,往往都是几千上万,PLD一般只能做到512个逻辑单元,而且如果用芯片价格除以逻辑单元数量,FPGA的平均逻辑单元成本大大低于PLD。 所以如果设计中使用到大量触发器,例如设计一个复杂的时序逻辑,那么使用FPGA就是一个很好选择。 同时PLD拥有上电即可工作的特性,而大部分FPGA需要一个加载过程,所以,如果系统要可编程逻辑器件上电就要工作,那么就应该选择PLD。

原文链接:http://xilinx.eetrend.com/forum/350

6055

6055

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?