- 最简单的自定义IP封装

1.1实验任务

将PL端控制LED灯每隔1s进行闪烁的IP核进行简单的封装,然后与ARM A9处理器连接,A9处理器给该LED IP核提供clk和rst_n信号

1.2实验过程

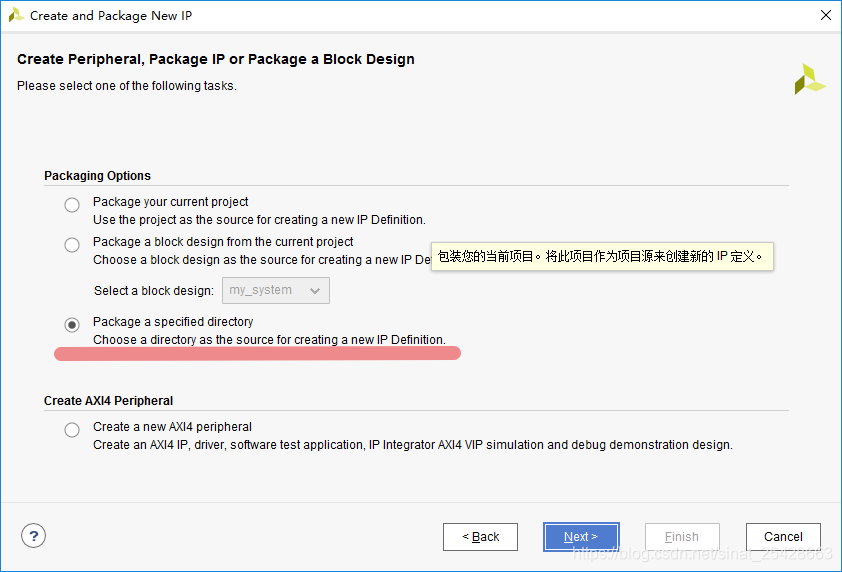

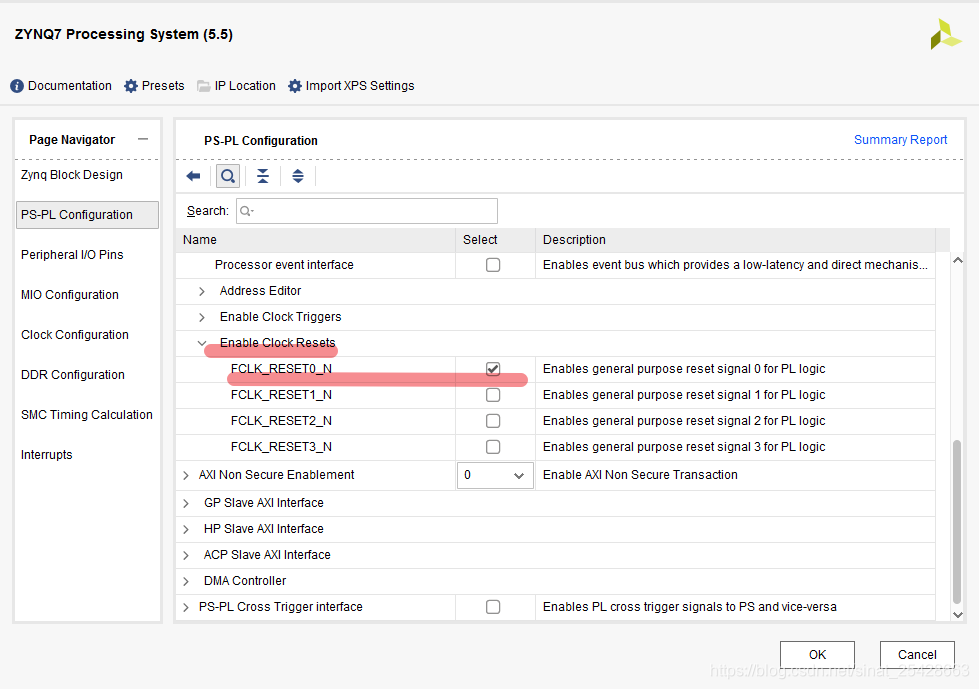

首先将Zynq_Uart工程另存为,在此工程上修改,避免重复性工作。首先需要显示FCLK,并将频率设置为100MHz,双击Zynq模块

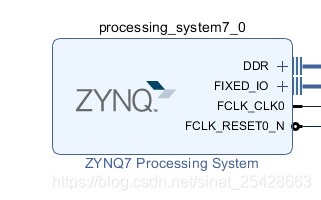

显示clk_rst_n信号

显示之后的效果如下

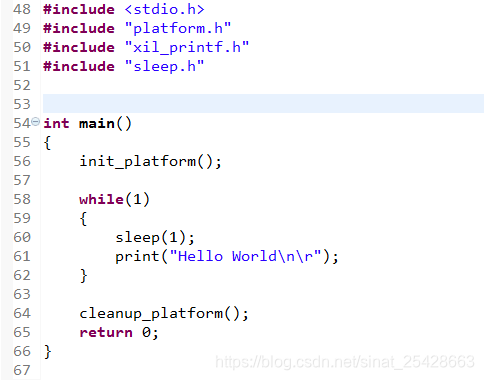

下面编写驱动PL端LED灯的代码,如下

- `timescale 1ns / 1ps

- module led(

- input clk, // 100MHz

- input rst_n,

- output reg[3:0] led

- );

- reg[31:0] cnt;

- always @(posedge clk, negedge rst_n) begin

- if(!rst_n)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5066

5066

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?